在超聲流量檢測(cè)過(guò)程中,,由于環(huán)境噪聲使得流量檢測(cè)的精度收到了嚴(yán)重的影響,。目前多采用軟件濾波的方法,對(duì)采集回來(lái)的聲波信號(hào)進(jìn)行數(shù)字處理,,以提高檢測(cè)的精度,。此類方法對(duì)硬件處理器的運(yùn)算能力要求較高,而且會(huì)影響檢測(cè)的實(shí)時(shí)性,。隨著微電子技術(shù)的不斷進(jìn)步,,FPGA的容量和處理速度已有了飛躍性的提高。特別是在數(shù)字信號(hào)處理方面,,其性能已經(jīng)超過(guò)了某些專用的信號(hào)處理芯片,。本文在的超聲波流量檢測(cè)信號(hào)采樣處理電路中,采用FPGA實(shí)現(xiàn)了聲波信號(hào)的高速緩存和FIR濾波器,,不僅達(dá)到了預(yù)期的消噪效果,,而且提高了系統(tǒng)運(yùn)行速度和集成度。下面將介紹FIR濾波器的具體實(shí)現(xiàn)過(guò)程,。

1 數(shù)字濾波原理與設(shè)計(jì)

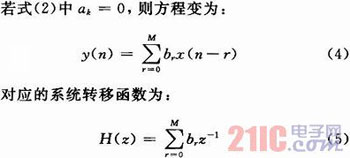

FIR數(shù)字濾波器的特性可以用它的系統(tǒng)轉(zhuǎn)移函數(shù)或差分方程來(lái)描述,。一般地,線性是不變離散系統(tǒng)的差分方程,,可表示為:

式中:zr,,pk分別為H(z)的M個(gè)零點(diǎn)和N個(gè)極點(diǎn),它們由系統(tǒng)的形式和各系統(tǒng)參數(shù)ak,,br所決定,。FIR濾波器都是非遞歸形式的濾波器。

此系統(tǒng)的輸出只與輸入x(n),x(n-1),,…有關(guān),,而與系統(tǒng)過(guò)去的輸出y(n-1),y(n-2),,…無(wú)關(guān),,此即非遞歸濾波器。

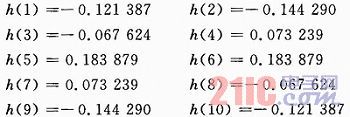

濾波器設(shè)計(jì)采用Matlab中的FDA Tool計(jì)算帶通濾波器系數(shù),。濾波器采用Kaiser窗函數(shù)設(shè)計(jì),,采樣頻率為40MHz,窗上下截止頻率分別為3MHz和7MHz,。由此得到的濾波器系數(shù)為:

2 FIR濾波器的FPGA實(shí)現(xiàn)

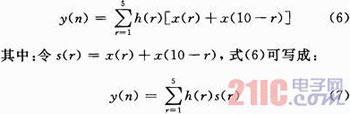

由式(4)可知,,F(xiàn)IR濾波器的數(shù)學(xué)表達(dá)式就是卷積運(yùn)算,也就是做乘加運(yùn)算,。例如,,一個(gè)M階的FIR濾波器的輸出是輸入樣本的M個(gè)依次值的加權(quán)和,加權(quán)系數(shù)就是此濾波器的單位沖激響應(yīng)值,。對(duì)于上節(jié)設(shè)計(jì)的10階線性FIR濾波器,可以得到:

這樣,,10階FIR濾波器的結(jié)構(gòu)可以描述為:輸入樣本x(n)經(jīng)過(guò)10階移位寄存器延遲后得到10個(gè)具有不同延遲的抽頭,,將對(duì)稱的抽頭值相加后再與相應(yīng)的權(quán)系數(shù)相乘,5個(gè)乘積相加就得到濾波器的輸出值,。濾波器結(jié)構(gòu)如圖1所示,。

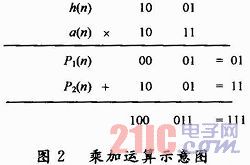

濾波器抽頭與權(quán)系數(shù)之間存在著乘法運(yùn)算,在硬件實(shí)現(xiàn)中乘法運(yùn)算是相當(dāng)復(fù)雜的運(yùn)算,,不僅占用大量硬件資源,,而且運(yùn)算速度較慢。為了提高運(yùn)算速度,,在此利用FPGA邏輯單元(LE)中的查找表實(shí)現(xiàn)替代乘法運(yùn)算的查表運(yùn)算,。為了說(shuō)明方便,在此以4階濾波器為例,,數(shù)據(jù)為2位的二進(jìn)制整形,。設(shè)a(1)=01,a(2)=11,,h(1)=10,,h(2)=01,權(quán)系數(shù)與抽頭之間的乘加運(yùn)算如圖2所示,。

圖2中,,P1(n)為抽頭低位與權(quán)系數(shù)的乘積結(jié)果,P2(n)為抽頭高位與權(quán)系數(shù)的乘積結(jié)果,在此稱之為單位積,。常規(guī)的計(jì)算順序是先將P1(n)和P2(n)的對(duì)應(yīng)項(xiàng)在垂直方向上移位相加,,所得結(jié)果再進(jìn)行水平方向上相加。但是從圖中可以看出,,先將P1(n)和P2(n)在水平方向上相加,,然后再進(jìn)行垂直方向上移位相加,所得的結(jié)果是一樣的,。第二種順序中,,P1(n)和P2(n)是h(n)和a(n)的某個(gè)比特位的乘積,而對(duì)于設(shè)計(jì)好的FIR濾波器h(n)是固定的,,這樣就可以通過(guò)a(n)某比特位的組合來(lái)查表求出P1(n)或P2(n),,并在水平方向上實(shí)現(xiàn)求和。如表1所示,,a1(n)表示a(n)的低位組合,,單位積P1表示相應(yīng)的權(quán)系數(shù)和。

對(duì)于a(n)的高位組合,,單位積P2可以建立同樣的組合表,。將P1和P2移位相加,即可得到濾波器的輸出結(jié)果,。在此例中采用的是2位二進(jìn)制的權(quán)系數(shù)和輸入樣本,,對(duì)于高精度的權(quán)系數(shù)和輸入樣本,只不過(guò)是增加更多的單位積P3,,P4,,…等等。

實(shí)際操作過(guò)程中,,基于FPGA的FIR濾波器通過(guò)三步完成,,第一步將輸入信號(hào)x(n)進(jìn)行移位延遲,形成n階抽頭,,再將相互對(duì)稱的抽頭相加得到濾波器抽頭,;第二步在FPGA中構(gòu)造ROM,按前一步產(chǎn)生的濾波器抽頭進(jìn)行查表運(yùn)算,;最后將所有位的查表運(yùn)算結(jié)果移位相加得到濾波器輸出y(n),。

3 試驗(yàn)結(jié)果分析

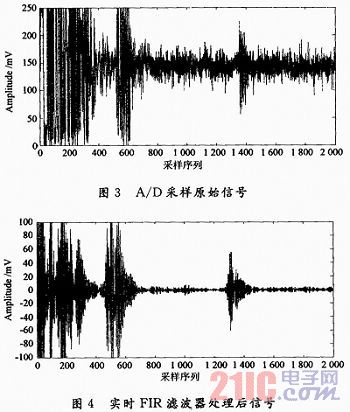

采用Altera公司的FPGA器件EPF10K30實(shí)現(xiàn)10階的帶通FIR濾波器進(jìn)行試驗(yàn)。A/D采樣頻率為40MHz,,精度為12位,,聲波中心頻率為5M-Hz。A/D采樣得到的原始聲波信號(hào)如圖3所示,。經(jīng)過(guò)FIR濾波器處理后的聲波信號(hào)如圖4所示,。

試驗(yàn)結(jié)果表明,采用FPGA實(shí)現(xiàn)的FIR濾波器有效地消弱了噪聲干擾,在保證實(shí)時(shí)性的基礎(chǔ)上,,為后期處理提供了可靠的數(shù)據(jù),。

4 結(jié)論

針對(duì)超聲波信號(hào)中的噪聲采用基于FPGA的FIR濾波,提高了硬件電路的集成度,,并取得了良好的消噪效果,。在硬件實(shí)現(xiàn)過(guò)程中采用查表方法替代濾波過(guò)程中的乘法運(yùn)算,節(jié)省了占用的片內(nèi)資源,,提高了處理速度,。同時(shí)由于采用了并行硬件算法,其處理速度遠(yuǎn)高于CPU或DSP上的程序處理速度,。