摘要:為實現(xiàn)高速電容耦合器件(CCD)數(shù)字圖像采集傳輸,提出一種基于PXIE總線和Camera Link協(xié)議的高速圖像采集系統(tǒng)設(shè)計方案。設(shè)計了Camera Link硬件接口電路,實現(xiàn)了視頻數(shù)據(jù)信號的接口設(shè)計、控制信號的接口設(shè)計、串行通信信號接口設(shè)計;同時采用Xilinx公司的Vir-tex-5 LX50T型FPGA作為PXIE傳輸控制器,并對IP核進(jìn)行了開發(fā),減少了外圍電路設(shè)計難度。創(chuàng)新性地運用直接內(nèi)存訪問的工作方式對PXIE傳輸速度進(jìn)行優(yōu)化。實驗結(jié)果表明,PXIE配置為8通道時,讀取數(shù)據(jù)速率達(dá)到1 504 MB/s,寫入速率達(dá)到了1 490 MB/s,可以滿足高速CCD數(shù)據(jù)的傳輸要求。

關(guān)鍵詞:PXIE;Camera Link;IP核;CCD DMA

電容耦合器件(Charge Coupled Device,CCD),是20世紀(jì)70年代初發(fā)展起來的新型半導(dǎo)體光電成像器件。由于其具有信號輸出噪聲低、動態(tài)范圍大、量子效率和電荷轉(zhuǎn)移效率高等特點,加之多年來新型半導(dǎo)體材料技術(shù)的不斷積累和大規(guī)模集成技術(shù)的日臻完善,CCD技術(shù)目前廣泛應(yīng)用于國民經(jīng)濟、國防建設(shè)、科學(xué)研究等各個領(lǐng)域。隨著上述領(lǐng)域?qū)?shù)字圖像的分辨率以及傳輸速度的要求越來越高,人們對高速圖像采集系統(tǒng)的性能、穩(wěn)定性和可靠性也提出了新的要求。本文提出了一種基于PXIE總線和Camera Link協(xié)議的高速CCD圖像采集系統(tǒng)設(shè)計方案,并詳細(xì)說明了部分模塊的具體實現(xiàn)方式。

1 系統(tǒng)工作原理及總體設(shè)計

1.1 Camera Link協(xié)議及PXIE協(xié)議介紹

(1)Camera Link協(xié)議簡介

Camera Link是一種基于視頻應(yīng)用發(fā)展而來的通信接口。它是NI等13家公司基于Channel Link技術(shù)聯(lián)合推出的一種新型接口,簡化了相機與其他設(shè)備的連接。Camera Link的驅(qū)動端將28位并行數(shù)據(jù)以7:1方式轉(zhuǎn)化為4組LVDS數(shù)據(jù)流和1組LVDS時鐘信號,串行發(fā)送至接收端進(jìn)行處理。其最高傳輸速率可達(dá)2.38 Gb/s。圖1為Camera Link工作原理圖。

Camera Link接口協(xié)議提供4類信號:相機控制信號、圖像數(shù)據(jù)信號、電源和串行通信信號。其接口有3種結(jié)構(gòu),分別是初級配置(Base)、中級配置(Medium)和高級配置(Full)。Camera Link使用端口定義來區(qū)分這些配置。3M 26-pin MDR(Mini D Ribbon)連接器之所以被選擇與Camera Link配套使用是因為它優(yōu)秀的設(shè)計和先前Channel Link高速傳輸?shù)某晒?jīng)驗。

(2)PXIE協(xié)議簡介

PXI(PCI Express for Instrumentation)由NI公司于1997年率先提出。PXIE基于Compact PCI標(biāo)準(zhǔn),增加了時鐘和同步觸發(fā)總線,但其核心仍然是PCI總線。PXI Express相對PXI最顯著的改進(jìn)和優(yōu)勢就在于它融入PCI Express的特點,采用串行傳輸,點到點的總線拓?fù)浣Y(jié)構(gòu)。不同于PXI在所有總線設(shè)備間分享帶寬,PXI Express為每一個設(shè)備提供單獨的傳輸通道。同時它所增加的時鐘和同步觸發(fā)信號以及擁有特殊的接口物理特性使得其在測量、通信、工業(yè)自動化等領(lǐng)域擁有更大的技術(shù)優(yōu)勢。本文采用PXIE-8x,最高傳輸速度達(dá)到1400Mb/s。

1.2 總體設(shè)計

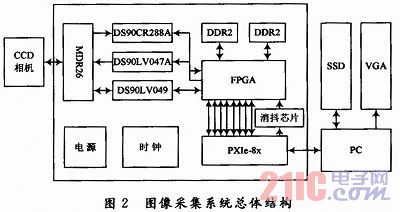

系統(tǒng)總體結(jié)構(gòu)圖,如圖2所示。

圖2中,DS90CR288A為NI公司高性能串并轉(zhuǎn)換器,將Camera Link接口協(xié)議的4路LVDS信號和1路LVDS時鐘轉(zhuǎn)換為28位LVCMOS/LVTTL數(shù)據(jù)和一路時鐘信號,DS90LV047A為NI公司的3 VLVDS 4路單端轉(zhuǎn)差分驅(qū)動器。DS90LV049為NI公司的3V LVDS雙向線路驅(qū)動器和雙向線路接收器。

系統(tǒng)工作流程為:

首先,采集卡通過DS90LV047A對CCD相機發(fā)出的控制指令。CCD相機在接到指令后,將采集到的圖像數(shù)據(jù)分為4路LVDS數(shù)據(jù)信號和1路LVDS時鐘信號,通過接口連接器MDR26,輸送到圖像采集卡;圖像采集卡將串行數(shù)據(jù)轉(zhuǎn)換成38路并行信號和1路隨路時鐘傳送給FPGA進(jìn)行數(shù)據(jù)處理。由于數(shù)據(jù)量很大,為保證數(shù)據(jù)低誤碼率及提高可靠性,使用了2塊Micron 2 GB DDR2對數(shù)據(jù)進(jìn)行緩存和乒乓處理。FPGA根據(jù)用戶的需求進(jìn)行高速的圖像處理。采集卡通過PXIE-8x將圖像數(shù)據(jù)上傳至PC(上位機)上進(jìn)行后期處理,同時實現(xiàn)PC(上位機)對圖像采集卡的控制。圖像數(shù)據(jù)最終通過PC將數(shù)據(jù)存儲在SSD(Solid-state Drive)電子盤上,以供隨時調(diào)用。在讀/寫速度等關(guān)鍵性能上,SSD電子盤遠(yuǎn)遠(yuǎn)優(yōu)于傳統(tǒng)機械硬盤,因此選用SSD電子盤為數(shù)據(jù)存儲介質(zhì)。采集卡還采用DS90LV049(LVDS雙線路驅(qū)動器,帶有雙線路接收器)來實現(xiàn)采集卡與相機間的串行通信,用戶可以根據(jù)需要對CCD相機進(jìn)行配置。

2 關(guān)鍵模塊設(shè)計

2.1 Camera Link接口設(shè)計

根據(jù)系統(tǒng)功能要求,Camera Link接口設(shè)計包括3個部分,即為視頻數(shù)據(jù)信號接口設(shè)計,控制信號接口設(shè)計,串行通信命令接口設(shè)計。

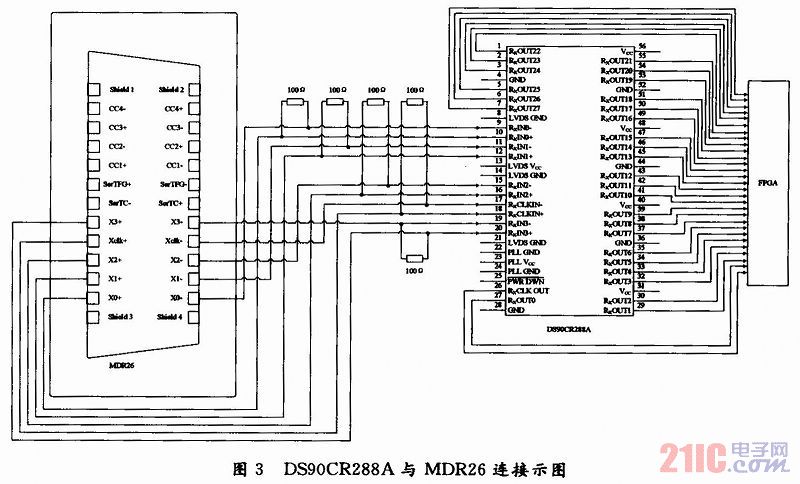

2.1.1 視頻數(shù)據(jù)信號的接口設(shè)計

視頻數(shù)據(jù)信號為FVAI,LVAL,DVAL和SP,它們分別是幀允許信號、行允許信號、數(shù)據(jù)允許信號和保留信號,4路均為LVDS數(shù)據(jù)信號,外加1對LVDS時鐘信號,在此采用了National Semiconductor公司的DS90CR288A芯片,將5路LVDS信號轉(zhuǎn)換為28路數(shù)據(jù)信號。具體連接圖如圖3所示。

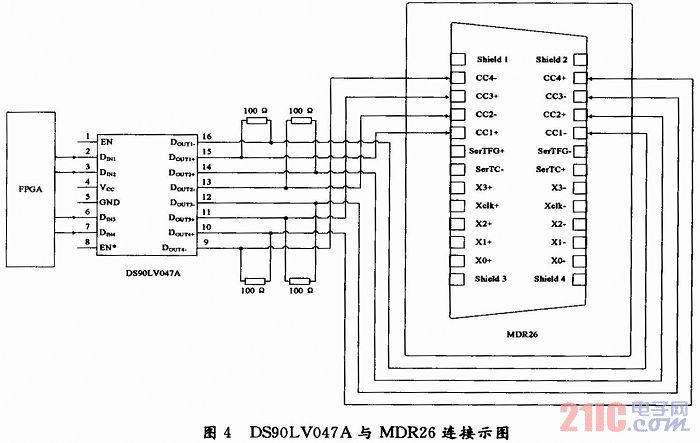

2.1.2 控制信號接口設(shè)計

相機控制信號CC1,CC2,CC3,CC4為4路LVDS信號,為節(jié)省布線空間,F(xiàn)PGA發(fā)出的控制信號均為單端信號,因此采用National Semicon-ductor公司的DS90LV047A芯片將采集卡發(fā)出的單端COMS控制信號轉(zhuǎn)化為LVDS信號,完成對CCD相機的控制。圖4為DS90LV047A與MDR26的連接。

2.1.3 串行通信信號接口設(shè)計

串行通信信號由兩對LVDS信號提供,這些信號使相機與其使用者之間可以進(jìn)行通信。因為是雙向通信,在此采用了National Semicon-ductor公司的DS90LV049芯片實現(xiàn)了LVDS差分信號到單端CMOS信號的雙向轉(zhuǎn)換。圖5為DS90LV049與MDR26的連接示圖。圖中EN為1時,EN可以不接,4條通路可以全通。

2.2 PXIE模塊設(shè)計

2.2.1 PXIE的時鐘電路設(shè)計

在PXIE規(guī)范中,對于時鐘的頻率穩(wěn)定度要求是100 MHz±300 ppm,抖動(Cycle-to-Cycle)需要小于125 ps,占空比要求50%±5%以內(nèi)。因此,系統(tǒng)中選用IDT公司的ICS874003-02作為100 MHz參考時鐘的抖動衰減器。ICS874003-02是一款高性能的將差分時鐘轉(zhuǎn)換為LVDS電平時鐘信號的時鐘抖動衰減器,該元件可支持PXI Express系統(tǒng),具有衰減或“清除”100 MHz PXIE輸入時鐘抖動,同時將其轉(zhuǎn)換成250 MHz LVDS輸出能力的時鐘器件。ICS874003-02在芯片內(nèi)部集成了一個高性能,低相噪的鎖相環(huán)。鎖相環(huán)的鑒相帶寬為400 kHz,可以快速鎖定時鐘,減小抖動。該器件支持低于1 ps RMS極低相位噪聲的基準(zhǔn)時鐘生成,滿足基于PXIE的高速應(yīng)用的嚴(yán)格的抖動要求。它的最大周期抖動為35 ps,占空比變化為50%±2%,完全可以滿足PXIE對時鐘的要求,其內(nèi)部原理圖如圖6所示。

該系統(tǒng)設(shè)計中采用QA0/nQA0和QA1/nQA1兩對差分輸出時鐘,并且將這兩個輸出分頻器的分頻系數(shù)設(shè)置為5,使輸出時鐘頻率和輸入時鐘頻率相同。

ICS874003-02提供獨立的電源用以隔離內(nèi)部鎖相環(huán)產(chǎn)生的開關(guān)噪聲,VDD,VDDA,以及VDDO抑必須單獨通過過孔連接到電源層,并且在每個電源腳上都要加入旁路電容,為了獲得最佳的時鐘抖動特性,電源需要相互隔離。如圖7所示,1個10 Ω的電阻以及1個10 μF和0.01 μF的旁路電容構(gòu)成了一個電源濾波電路,連接到每個VDDA腳,10 Ω的電阻可以被磁珠所替代。

2.2.2 PXIE的IP core設(shè)計

該系統(tǒng)中,采用Virtex-5LX50T型FPGA作為PXIE的傳輸控制器,由于FPGA內(nèi)部集成了PCIe端點模塊,所以減少了很多外圍硬件電路的設(shè)計難度。PCIe端點模塊的IP核框圖如圖8所示。

由圖8可以看出,PXIE IP核采用分層結(jié)構(gòu),即分別為物理層鏈路模塊、物理層、數(shù)據(jù)鏈路層、傳輸層和用戶應(yīng)用層。傳輸層負(fù)責(zé)處理用戶應(yīng)用層(User Applieation)提供的傳輸層包(TLP)并安排其傳輸。數(shù)據(jù)鏈路層負(fù)責(zé)鏈路管理和數(shù)據(jù)完整性,包括錯誤的檢測和糾正。物理層負(fù)責(zé)完成包的成幀和解幀、字節(jié)的組合和拆分、鏈路的初始化和訓(xùn)練、擾碼生成和解擾。發(fā)送時,物理層鏈路模塊負(fù)責(zé)將物理層生成的擾碼應(yīng)用到傳輸數(shù)據(jù)中,同時復(fù)用到物理層模塊接收到的有序集中,最后把包傳輸給傳輸接口;接收時,負(fù)責(zé)從傳輸接口上接收TLP字節(jié),從數(shù)據(jù)中解碼有序集,并且將DLLP和TLP解擾。

2.2.3 PXIE傳輸速度問題及解決情況

由于PXIE傳輸協(xié)議是基于PCIe傳輸協(xié)議的擴展,所以可以利用目前比較成熟的PCIe傳輸協(xié)議實現(xiàn)技術(shù)在硬件程序設(shè)計層次上實現(xiàn)PXIE傳輸協(xié)議,至于PXIE協(xié)議的一些擴展接口,都可以在FPGA外圍用基本硬件電路簡易的實現(xiàn)。FPGA生產(chǎn)廠商Xilinx公司提供了一套成熟,穩(wěn)定并且免費的PCIe傳輸方案,以IP(Intellectual Property)的形式提供給用戶。

PCIe IP核雖然為PXIE傳輸協(xié)議提供了解決方案,但是仍然存在問題。首先,在實際測試過程當(dāng)中,由于PCIe IP一直占用了CPU,使得PC在進(jìn)行數(shù)據(jù)傳輸時,主機本身無法進(jìn)行其他操作,還有一定幾率造成系統(tǒng)崩潰。其次,由于PCIe協(xié)議進(jìn)行傳輸?shù)陌d荷過小,在進(jìn)行大數(shù)據(jù)量傳輸?shù)臅r候,會進(jìn)行多次傳輸,從而浪費大量時間在結(jié)束和發(fā)起傳輸上,導(dǎo)致平均數(shù)據(jù)傳輸率下降。最后,由于IP核的重要特性是通用化,所以IP核的接口包括了所有PCIe信號,使得用戶操作非常繁瑣,不利于設(shè)計的移交和修改。直接內(nèi)存訪問(Direct Memory Access,DMA)控制器能夠從根本上解決前兩個問題,經(jīng)過優(yōu)化設(shè)計也能改善第三個問題。

PXIE總線DMA的FPGA功能設(shè)計框圖如圖9所示。

當(dāng)PC機需要通過PXIE總線發(fā)送數(shù)據(jù)時,首先PC機為DMA傳輸在內(nèi)存中劃定兩塊內(nèi)存空間,作為數(shù)據(jù)的第一級緩存,并將這兩塊內(nèi)存空間的基地址和大小輪流通過PXIE總線傳給DMA控制器。這些配置命令通過特定的字符串被識別,并寫入相應(yīng)的配置命令寄存器。劃定兩塊內(nèi)存空間是為了在當(dāng)DMA控制器從一塊內(nèi)存中讀取數(shù)據(jù)時,PC機可以向另一塊內(nèi)存寫入數(shù)據(jù),以乒乓操作的形式提高傳輸效率。

接下來,PC機發(fā)起對數(shù)據(jù)的傳輸。PC機上的PCIe控制器從內(nèi)存中取得數(shù)據(jù)后,將原始數(shù)據(jù)封裝,并串轉(zhuǎn)換往下繼續(xù)傳輸,數(shù)據(jù)包通過吉比特串行收發(fā)器傳至FPGA,在進(jìn)入PCIe IP核后被拆解,剝離的糾錯信息作為包進(jìn)一步處理的依據(jù),最后在應(yīng)用層以并行數(shù)據(jù)的形式推入DMA控制器。

DMA控制器將數(shù)據(jù)流存人數(shù)據(jù)輸出FIFO,根據(jù)FIFO剩余空間的大小判定是否從PC機中繼續(xù)讀取數(shù)據(jù),這樣就保證了數(shù)據(jù)不會因為來不及從FIFO中取走而丟失。當(dāng)DMA控制器接收到一塊內(nèi)存大小的數(shù)據(jù)之后,就會以邊帶信號的形式發(fā)送中斷信號給上位機,上位機接收到中斷之后就可以開始下1次DMA傳輸。

當(dāng)PC機需要通過PXIE總線接收數(shù)據(jù)時,工作流程與通過PXIE總線發(fā)送數(shù)據(jù)基本類似,主要區(qū)別在于從PC機往下發(fā)送的包里不包含數(shù)據(jù),僅包含路由及其他控制信息,DMA控制器接收到包后,會以完成包的形式將數(shù)據(jù)打包往上傳回PC機,完成包按照接收到包中的路由信息,逆向?qū)ぶ坊氐絇C機的內(nèi)存,PC機就完成了一次通過PXIE總線接收數(shù)據(jù)。

加入DMA控制器之后的PXIE總線被重新封裝,操作得到簡化。

2.3 測試結(jié)果

在測試中,PXIE配置為8通道,測試數(shù)據(jù)為16 MB,在PC機通過PXIE接口讀取數(shù)據(jù)的操作過程當(dāng)中,平均數(shù)據(jù)率達(dá)到1 504 Mb/s。在PC機通過PXIE接口發(fā)送數(shù)據(jù)的操作過程中,平均數(shù)據(jù)率達(dá)到1 490 Mb/s。通過PCIe測速軟件進(jìn)行傳輸速度測試,其結(jié)果如圖10所示。

3 結(jié)語

本文介紹了一種基于PXIE總線和Camera Link協(xié)議的高速CCD圖像采集系統(tǒng)的設(shè)計方案。該方案給出了一種Camera Link硬件接口電路的設(shè)計思路,并且選用Xilinx公司的Virtex-5 LX50T型FPGA作為整個采集系統(tǒng)的核心處理器,同時對Virtex-5自帶的IPcore進(jìn)行研究和開發(fā),實現(xiàn)Camera Link采集卡通過PXIE總線與上位機進(jìn)行串行通信。在試驗過程中,F(xiàn)PGA設(shè)計靈活,開發(fā)周期短的優(yōu)點充分得以體現(xiàn),為下一步的高速圖像采集系統(tǒng)的研制奠定了基礎(chǔ)。