摘要:介紹了遠(yuǎn)距離測(cè)溫器的結(jié)構(gòu)組成和工作原理,設(shè)計(jì)了基于FPGA的遠(yuǎn)距離測(cè)溫器數(shù)控系統(tǒng)的數(shù)據(jù)采集與控制系統(tǒng),,使用Altera公司的Cyclonell系列的FPGA實(shí)現(xiàn)了包括數(shù)據(jù)采集,、數(shù)據(jù)通信等控制功能,著重?cái)⑹隽擞布c軟件的實(shí)現(xiàn)方法,。該數(shù)控系統(tǒng)具有測(cè)量精度高,,低功耗等特點(diǎn)。

關(guān)鍵詞:遠(yuǎn)距離測(cè)溫,;FPGA,;數(shù)據(jù)采集與控制系統(tǒng);NiosⅡ

0 引言

在一些特殊的科研場(chǎng)所和工業(yè)生產(chǎn)單位,,出于各種條件限制,,儀表往往不能就近測(cè)量物體實(shí)際溫度;而以往所使用的一些傳感器在使用時(shí)受到各種環(huán)境因素的影響,,使得傳感器測(cè)量得到的溫度不能精確地反映被測(cè)物體的溫度,。因此,人們需要找尋一種遠(yuǎn)距離測(cè)溫器,,能夠精確測(cè)量物體溫度,,并能實(shí)時(shí)監(jiān)控溫度數(shù)據(jù)。

遠(yuǎn)距離測(cè)溫器是一種被動(dòng)式的溫度遙感器,,可用于遠(yuǎn)距離探測(cè)物體的溫度,,在科學(xué)研究和工業(yè)生產(chǎn)中發(fā)揮了重要作用,。由于在使用時(shí)人們對(duì)測(cè)溫器的測(cè)量范圍、靈敏度要求很高,,同時(shí)由于當(dāng)今遙感儀器的設(shè)計(jì)越來越趨于低功耗高密度及小型化,因此,,要求測(cè)溫器的數(shù)據(jù)處理與控制系統(tǒng)具有高可靠性,、高分辨率、實(shí)時(shí)性,、體積小等特點(diǎn),。由于FPGA的功能強(qiáng)大,邏輯速度快,,可以用多種接口電平與外界通信,,可以方便的更新程序以實(shí)現(xiàn)多種功能,所以本文采用Altera公司的CycloneⅡ系列的FPGA為核心進(jìn)行遠(yuǎn)距離測(cè)溫器的數(shù)控系統(tǒng)設(shè)計(jì),,實(shí)現(xiàn)了系統(tǒng)的多功能和小型化,。

1 系統(tǒng)結(jié)構(gòu)

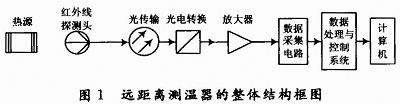

遠(yuǎn)距離測(cè)溫器的結(jié)構(gòu)框圖如圖1所示。由紅外線探測(cè)頭,、光電轉(zhuǎn)換單元,、放大電路、數(shù)據(jù)采集電路和數(shù)據(jù)處理與控制系統(tǒng)等功能模塊組成,。紅外探測(cè)頭用于搜集物體發(fā)射出的紅外光線,,將有用信號(hào)傳輸至較遠(yuǎn)且適合人操作的地方,最后使用數(shù)據(jù)處理和控制系統(tǒng)進(jìn)行控制,。

數(shù)據(jù)處理與控制系統(tǒng)接收計(jì)算機(jī)傳輸?shù)闹噶?,控制系統(tǒng)運(yùn)行。系統(tǒng)通電后,,紅外接收天線接收的光信號(hào)模擬量經(jīng)過遠(yuǎn)距離傳輸,,信號(hào)放大后經(jīng)過A/D模數(shù)轉(zhuǎn)換后再送入數(shù)據(jù)處理和控制系統(tǒng),由數(shù)據(jù)處理與控制系統(tǒng)進(jìn)行數(shù)據(jù)采集和存儲(chǔ),、與計(jì)算機(jī)的數(shù)據(jù)通信,、工作狀態(tài)控制。數(shù)據(jù)處理與控制系統(tǒng)在遠(yuǎn)距離測(cè)溫器中處于重要的位置,。

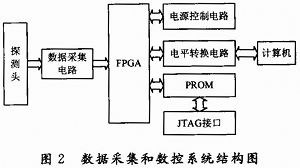

數(shù)據(jù)采集,、數(shù)據(jù)處理與控制系統(tǒng)電路由FPGA及其外圍電路、數(shù)據(jù)采集系統(tǒng),、電平轉(zhuǎn)換電路,、總線接口電路等部分組成,如圖2所示,。

FPGA根據(jù)系統(tǒng)本身的時(shí)序和計(jì)算機(jī)送入的控制指令,,控制數(shù)據(jù)采集電路完成數(shù)據(jù)的采集,。同時(shí),F(xiàn)PGA內(nèi)部的可配置軟處理核NiosⅡ系統(tǒng)將根據(jù)計(jì)算機(jī)中提供的校準(zhǔn)值來修正由前端模擬電路引起的偏差,,并由此生成實(shí)際誤差很小的曲線方程,。校準(zhǔn)工作完畢后,整個(gè)系統(tǒng)既可脫離計(jì)算機(jī)方便地用于遠(yuǎn)距離的溫度測(cè)量,,也可以用于聯(lián)機(jī)對(duì)物體溫度的實(shí)時(shí)檢測(cè),,采集到的大量數(shù)據(jù)提供給計(jì)算機(jī)作分析用。

數(shù)控系統(tǒng)采用Altera公司的CycloneⅡ系列FPGA中的EP2C8為核心進(jìn)行設(shè)計(jì),。CycloneⅡ器件采用90 nm,、低K值電介質(zhì)工藝,通過使硅片面積最小化,,可以在單芯片上支持復(fù)雜的數(shù)字系統(tǒng),。眾多可由用戶自行定義的I/O管腳有利于系統(tǒng)進(jìn)行外部擴(kuò)展。其配置PROM采用Altera公司提供的16 MB的EPCS4串行配置PROM,,該配置器件具備在系統(tǒng)編程(ISP)能力和多次編程能力,,具有包括ISP和FLASH存儲(chǔ)器訪問接口等特性。

數(shù)據(jù)采集電路采用AD公司的模數(shù)轉(zhuǎn)換器AD7675,,該芯片只需要提供+5 V工作電源,,典型功耗為15 mW,芯片轉(zhuǎn)換速度為100 KSPS,,可選并行或串行采樣數(shù)據(jù)輸出,,對(duì)外可選+5 V或+3.3 V接口電平。被測(cè)模擬信號(hào)電壓輸入范圍為-2.5~+2.5 V,,可以做到最高16位不失碼,。

2 硬件電路設(shè)計(jì)

2.1 電源控制電路

由于整個(gè)電路系統(tǒng)涉及模擬和數(shù)字部分多種芯片的運(yùn)作,A/D采樣芯片和FPGA芯片均需要兩種以上的電源供電,,所以選取合適的電壓轉(zhuǎn)換器非常重要,。電源控制電路選用Linear公司的線形電源模塊來提供A/D芯片所需要的+3.3V,+2.5V電壓和FPGA所需要的+3.3V和+1.2V電壓,,為了提高信號(hào)質(zhì)量,,模擬和數(shù)字部分的+3.3 V電壓分別由不同的電源轉(zhuǎn)換模塊提供。

2.2 數(shù)據(jù)采集電路

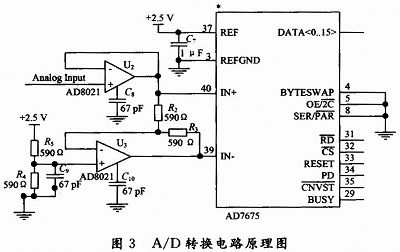

數(shù)據(jù)采集電路主要由AD7675組成,,由于其輸出I/O部分采用+3.3 V供電,,故其所有的數(shù)據(jù)輸出管腳和輸入控制信號(hào)不需要進(jìn)行電平轉(zhuǎn)換,可以直接與FPGA的I/O管腳相連,。A/D芯片的轉(zhuǎn)換速率為100KSPS,,選擇16 b雙極性補(bǔ)碼輸出,最高位表示符號(hào)位,。硬件電路如圖3所示,。采集到的數(shù)據(jù)送入FPGA的寄存器,,再傳送到計(jì)算機(jī)中,供數(shù)據(jù)分析用,。

AD7675的模擬信號(hào)輸入部分選用AD公司的AD8021運(yùn)算放大器實(shí)現(xiàn)模擬輸入信號(hào)的單端到差分信號(hào)的轉(zhuǎn)換,。電源進(jìn)入電源管腳前應(yīng)就近安裝鉭電容進(jìn)行濾波,以減小電源上的雜波干擾,,提高信號(hào)質(zhì)量,。AD7675支持并行和串行兩種數(shù)據(jù)輸出方式,本系統(tǒng)選擇并行16 b補(bǔ)碼采樣數(shù)據(jù)輸出,,與此相關(guān)的一些控制信號(hào),如BYTESWAP,,OB,,SER/PAR需要被置為低電平。而其它RESET和數(shù)據(jù)輸出I/O管腳接入FPGA,,由FPGA控制,。

2.3 FPGA與計(jì)算機(jī)接口電路

FPGA通過串行通信接口與外接計(jì)算機(jī)實(shí)現(xiàn)通信。本文選用MAX232實(shí)現(xiàn)LVTTL與EIA的電平轉(zhuǎn)換,,可方便的完成FPGA與計(jì)算機(jī)之間的RS 232通信,。

2.4 數(shù)字控制單元設(shè)計(jì)

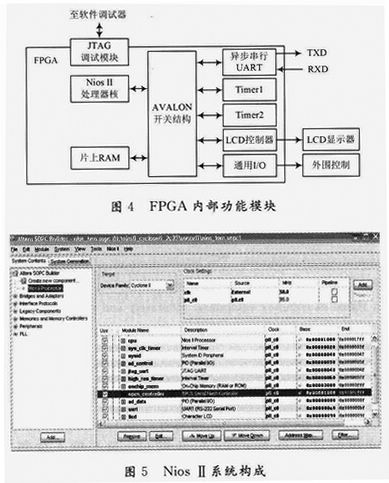

該測(cè)溫器的軟件設(shè)計(jì)主要分為兩個(gè)部分,一是FPGA的相關(guān)程序設(shè)計(jì),,其主要功能包括:A/D數(shù)據(jù)采集控制,、串口數(shù)據(jù)通信控制、LCD的讀寫控制以及PROM的燒錄等,;二是計(jì)算機(jī)中的相關(guān)程序,,主要功能包括數(shù)值運(yùn)算、標(biāo)定FPGA和將采集到的數(shù)據(jù)存儲(chǔ)以供分析等,。在整個(gè)FPGA的設(shè)計(jì)上,,由Altera公司開發(fā)的基于SoPC的NiosⅡ處理器及其軟件開發(fā)包SoPC Builder可以方便地將所需要的IP核、存儲(chǔ)器,、接口控制器等簡(jiǎn)單而又快速的集成到FPGA中去,,從而縮短設(shè)計(jì)周期。FPGA內(nèi)部功能模塊如圖4所示,。

FPGA的核心控制系統(tǒng)是由1 400~1 800 LE構(gòu)成的,,運(yùn)行起來可以到達(dá)86DMIPSD的f型NiosⅡCPU。除了CPU外,,數(shù)控系統(tǒng)主要還包括一個(gè)標(biāo)志NiosⅡ系統(tǒng)的系統(tǒng)ID核,;一個(gè)提供JTAG串行異步收發(fā)器的IP核,用于在線調(diào)試FPGA的程序,;一個(gè)可以實(shí)現(xiàn)任何標(biāo)準(zhǔn)RS 232標(biāo)準(zhǔn)波特率的UART核,,用在控制電路調(diào)試成功后在單機(jī)工作狀態(tài)下與外接計(jì)算機(jī)通信,;兩組并行輸入、輸出PIO核,,分別對(duì)A/D采樣電路進(jìn)行控制和讀取A/D采樣后得到的數(shù)據(jù),;兩個(gè)LCD控制器IP核;一個(gè)用于運(yùn)行程序的片內(nèi)ROM,;一個(gè)提供系統(tǒng)時(shí)鐘的pll,;一個(gè)EPCS串行配置器件控制器IP核。如圖5所示,。

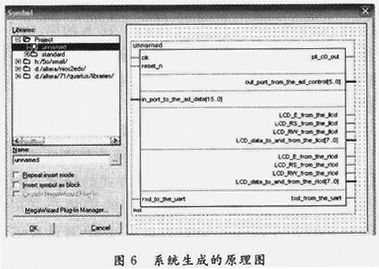

系統(tǒng)生成的原理圖如圖6所示,。

3 系統(tǒng)開發(fā)測(cè)試

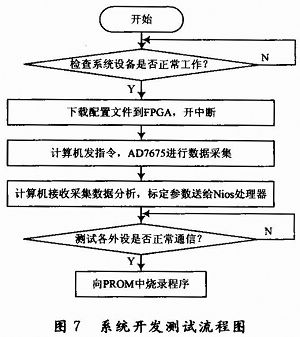

系統(tǒng)構(gòu)建好之后,需要進(jìn)一步的測(cè)試才能確保其正常測(cè)溫,。系統(tǒng)的開發(fā)測(cè)試流程如圖7所示,。

上電后首先觀測(cè)系統(tǒng)的主要硬件是否正常工作,將在NiosⅡIDE中生成的SOF文件下載到FPGA中,,完成NiosⅡ系統(tǒng)的下載和初始化,。然后將NiosⅡ軟件通過JTAG口下載到目標(biāo)系統(tǒng)中。系統(tǒng)正常工作后,,由遠(yuǎn)端計(jì)算機(jī)通過串口對(duì)A/D進(jìn)行初始化,,采集數(shù)據(jù)。計(jì)算機(jī)接收到A/D采樣數(shù)據(jù)后,,就可以對(duì)測(cè)溫器進(jìn)行標(biāo)定,,通過數(shù)據(jù)處理計(jì)算出用于標(biāo)定各臺(tái)測(cè)溫器的校準(zhǔn)方程。

標(biāo)定過程如下,,將測(cè)溫器紅外接收探測(cè)頭對(duì)準(zhǔn)熱源,,熱源產(chǎn)生準(zhǔn)確的溫度。為了測(cè)量準(zhǔn)確,,對(duì)于同一個(gè)溫度點(diǎn),,采用多次測(cè)量取平均值的方法。由計(jì)算機(jī)通過串口通信記錄下多次A/D采樣的值與對(duì)應(yīng)的溫度值,。從低溫開始到較高的溫度,,由計(jì)算機(jī)通過串口通信記錄下A/D采樣值。當(dāng)記錄下的數(shù)值達(dá)到可以反映各溫度段變化的情況時(shí),,就可以讓計(jì)算機(jī)采用合適的數(shù)據(jù)擬合方法生成反映該測(cè)溫器測(cè)量特性的曲線方程,。計(jì)算機(jī)將方程系數(shù)傳送給NiosⅡ系統(tǒng),完成對(duì)整個(gè)測(cè)溫器的校準(zhǔn),。

最后檢查FPGA中NiosⅡ處理器能否通過LCD控制器與LCD正常通信,、LCD能否正常顯示字符;NiosⅡ軟處理器可否與PROM實(shí)現(xiàn)正常的讀寫,。調(diào)試成功后為了節(jié)約資源可將JTAG調(diào)試去掉,,然后將正確的程序燒錄到EPCS4中,。這時(shí)所設(shè)計(jì)的程序即可脫離計(jì)算機(jī)及NiosⅡIDE獨(dú)立運(yùn)行。

完成了整個(gè)開發(fā)過程的測(cè)溫器即可正常使用,,對(duì)標(biāo)定溫度范圍內(nèi)的溫度進(jìn)行測(cè)量,。脫機(jī)測(cè)量時(shí),由定時(shí)器產(chǎn)生對(duì)A/D采樣時(shí)所需的時(shí)鐘脈沖,,NiosⅡ系統(tǒng)的兩組PIO,,分別控制A/D的控制信號(hào)和將A/D采樣值讀入NiosⅡ系統(tǒng)。在使用時(shí),,仍然采用多次測(cè)量取平均值的方法來得到A/D采樣值,,然后根據(jù)擬合方程,即可得到對(duì)應(yīng)的溫度值,,然后NiosⅡ系統(tǒng)控制LCD控制器的R/W,,RS和DB0~DB7,將對(duì)應(yīng)的溫度值顯示在

LCD上,。而當(dāng)需要聯(lián)機(jī)使用時(shí),NiosⅡ系統(tǒng)通過串口將存儲(chǔ)在內(nèi)部的A/D采樣值和對(duì)應(yīng)的溫度值發(fā)送到計(jì)算機(jī)中,,形成文件供分析用,。

4 結(jié)語

本文設(shè)計(jì)的測(cè)溫器的數(shù)控電路以Altera公司的CycloneⅡ系列的FPGA為核心,完成了從總體方案設(shè)計(jì)到系統(tǒng)調(diào)試等一系列過程,。整個(gè)數(shù)控系統(tǒng)共計(jì)占用3 700多個(gè)LE,,99 200個(gè)存儲(chǔ)器比特。為整個(gè)測(cè)溫器提供了穩(wěn)定可靠的數(shù)據(jù)處理平臺(tái),,可為更高級(jí)別的功能擴(kuò)展提供一定的參考,,具有很廣的應(yīng)用前景。