直接數(shù)字頻率合成(DDS)具有快速頻率切換和調(diào)制能力,應(yīng)用廣泛。但是,當?shù)凸暮偷统杀臼侵饕紤]因素時,DDS常常不得不退居其次,讓位于模擬鎖相環(huán)(PLL)。AD9913改變了這一局面,不僅能在125MHz輸出帶寬范圍提供DDS技術(shù)的快速切換和調(diào)制靈活性,而且具備與PLL相似的低功耗特性,其功耗僅有大約50mW。

DDS解決方案的功耗一直比較高,例如AD9850,它是20世紀90年代中期推出的首批DDS產(chǎn)品之一,集成數(shù)模轉(zhuǎn)換器(DAC),在50MHz輸出帶寬時的功耗為380mW;而AD9913采用了創(chuàng)新技術(shù),其帶寬功耗比相對于AD9850提高了20倍。

AD9913帶給便攜式和/或儀器儀表應(yīng)用的好處主要有三方面:50mW的低功耗使得手持式和其他便攜式應(yīng)用也能受惠于DDS技術(shù);可編程模數(shù)架構(gòu)對于網(wǎng)絡(luò)時鐘和儀器儀表應(yīng)用是一項有吸引力的特性,它支持合成同一速率的任意有理分數(shù)(兩個整數(shù)的比)的頻率。傳統(tǒng)的DDS只能合成同一速率的分母為2的冪的有理分數(shù)頻率,例如1/4和5/16,而AD9913則不受“2的冪”限制,它能產(chǎn)生同一速率的任意有理分數(shù)頻率,如1/10、3/7或286/11487等,只要它們處于AD9913的編程范圍內(nèi);最后,AD9913像ADI公司的一些早期DDS產(chǎn)品一樣,能夠極其靈活地產(chǎn)生多種波形。

AD9913采用了多項創(chuàng)新省電技術(shù),從而實現(xiàn)低功耗特性。第一項創(chuàng)新涉及到DDS的相位幅度轉(zhuǎn)換部分,該部分根據(jù)一個正弦和/或余弦函數(shù)將相位累加器產(chǎn)生的瞬時相位值轉(zhuǎn)換為幅度值。傳統(tǒng)上,此任務(wù)由一個只讀存儲器(ROM)查找表來執(zhí)行。然而,隨著DDS技術(shù)的速度不斷提高,結(jié)構(gòu)日益復雜,ROM方法的功耗負擔已變得不可接受,這就需要使用一個專有角度-旋轉(zhuǎn)(angle-rotation)算法,依靠計算引擎來執(zhí)行正弦和/或余弦轉(zhuǎn)換。角度-旋轉(zhuǎn)算法方法可以追溯到AD9850,相比于ROM查找表方法,其功耗大大降低。如果不采用角度-旋轉(zhuǎn)算法,許多早期DDS產(chǎn)品將需要特殊的散熱封裝來適應(yīng)更高的功耗。此外,散熱考慮還可能會使我們不得不減去現(xiàn)有DDS產(chǎn)品上的許多有用功能,例如,對DDS輸出信號的數(shù)字相位和/或頻率調(diào)制、利用數(shù)字濾波降低sin(x)/x損耗、針對多通道應(yīng)用使用多個DDS內(nèi)核。

第二項重大省電突破可以歸功于ADI公司已獲專利的相位交錯DDS架構(gòu)(美國專利第6587863號)。相位-旋轉(zhuǎn)算法實現(xiàn)的節(jié)能降耗使得我們可以考慮在同一芯片上運行多個DDS內(nèi)核。我們發(fā)現(xiàn),以較低采樣速率運行多個DDS內(nèi)核的功耗小于以極高采樣速率運行一個DDS內(nèi)核的功耗,這是一項非常有意義的突破,因為要充分利用新型高分辨率(14位或更高)、高采樣速率(1GHz或更高)數(shù)模轉(zhuǎn)換器(DAC)內(nèi)核,必須創(chuàng)新DDS技術(shù)。交錯DDS架構(gòu)使得設(shè)計工程師能夠集成多個已經(jīng)降低功耗的DDS內(nèi)核,并且以低于高頻DAC內(nèi)核的采樣速率運行這些內(nèi)核。這種創(chuàng)新架構(gòu)連同180nm CMOS制造工藝的采用,導致DDS輸出帶寬顯著提高,而功耗只比上一代低頻DDS產(chǎn)品略有增加。

然而,對于手持式和便攜式應(yīng)用,即使有了上述創(chuàng)新,功耗仍然顯得過大。為了解決這一問題,還需要一項創(chuàng)新。為此,我們對角度-旋轉(zhuǎn)算法進行改進,推出一種新的專有算法,以便進一步降低DDS內(nèi)核的功耗。新算法與注重低功耗操作的設(shè)計原則相結(jié)合,使得設(shè)計工程師能夠?qū)崿F(xiàn)期望的低功耗設(shè)計目標。新的設(shè)計原則包括:關(guān)閉特定工作模式不需要的所有多余內(nèi)部時鐘,以及在不會降低頻譜性能或不當?shù)叵拗茙挼那疤嵯拢鳒p每個電路模塊的功耗。

這些創(chuàng)新的成果就是AD9913,其采樣速率最高可達250MHz,而功耗僅有50mW。在250MHz的采樣速率下,可用帶寬約為100MHz。AD9913的這種輸出頻率能力和低功耗特性使它特別適合各種無線電控制單元,以及用于條形碼和射頻識別(RFID)標簽的無線掃描器。然而,對于要求100MHz以上帶寬的應(yīng)用,必須使用一個輔助PLL進行上變頻。其他能夠受益于低功耗DDS技術(shù)的手持式/便攜式應(yīng)用包括:軟件無線電(SDR)、遠程或便攜式有線電視測試設(shè)備、醫(yī)療血糖儀、無線火災報警,以及頻譜分析儀和波形發(fā)生器等電子測量設(shè)備。

獨特的架構(gòu)

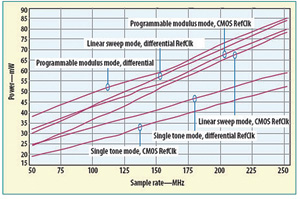

圖1顯示了AD9913在標稱輸出頻率100MHz下的低功耗特性。圖中的曲線對應(yīng)3種不同的工作模式(單音、線性掃描和可編程模數(shù))和兩種REFCLK輸入驅(qū)動方式(直接由差分源驅(qū)動或直接由單端源驅(qū)動,內(nèi)部PLL禁用)。

圖1 AD9913的功耗和采樣率之間的關(guān)系

AD9913區(qū)別于傳統(tǒng)DDS器件的地方在于其獨特的可編程模數(shù)架構(gòu)。傳統(tǒng)的DDS依靠相位累加器來分辨頻率,累加器的大小(位數(shù))決定DDS的頻率分辨率。

如果相位累加器具有C位分辨率,則傳統(tǒng)DDS提供的頻率分辨率為fS/2C,其中,fS為DDS的采樣速率。數(shù)字調(diào)諧字M可以是從0?2(C-1)的任意整數(shù)。理論上,允許的調(diào)諧字范圍是從2(C-1)?2C-1,但這會導致奈奎斯特鏡像頻率(即計數(shù)器旋轉(zhuǎn)相量)的合成。根據(jù)數(shù)字調(diào)諧字和DDS采樣速率(fS)可以列出熟悉的DDS頻率合成方程式,其中,fO為DDS輸出頻率:

fO/fS=M/2C (1)

因為M必須為整數(shù),所以對于給定的采樣速率,傳統(tǒng)DDS只能合成2(C-1)個獨特的頻率。也就是說,當M=0時,輸出頻率為0(DC);當M=2(C-1)-1時,輸出頻率只差0.5fS。所有剩余的輸出頻率都是fs/(2C)(DDS的頻率分辨率)的增量。多數(shù)情況下,如此精密的頻率分辨率是非常令人滿意的。例如,AD9913擁有一個32位累加器,其頻率分辨率為(250MHz)/232,或者大約0.058Hz。

現(xiàn)在考慮這樣一種情況:一個傳統(tǒng)DDS具有一個32位累加器,要求利用它來合成一個恰好為采樣速率的1/1000的輸出頻率。這意味著fO/fS=1/1000,將它代入方程式1的左邊并求解M可得:M=232/1000,或M=4294967.296。該M顯然不是整數(shù),但傳統(tǒng)DDS要求M必須是整數(shù)值,因此使用它的最接近整數(shù)值,本例為4294967。問題在于,使用這個調(diào)諧字不能精確地合成0.001fS的頻率,而是合成大約0.000999999931fS的頻率。在某些應(yīng)用中,例如網(wǎng)絡(luò)時鐘應(yīng)用,這一細微的偏差是不可接受的。

傳統(tǒng)DDS中的C位相位累加器導致模數(shù)(N)是固定的,即N=2C。可編程模數(shù)DDS架構(gòu)對相位累加器進行了巧妙的改造,使得模數(shù)可以是滿足條件1≤N≤2C的任意整數(shù)。也就是說,N值可以由用戶設(shè)定。對于可編程模數(shù)DDS架構(gòu),當N=1或N=2時,合成的頻率為0Hz,因此可用的最小模數(shù)(用于產(chǎn)生DC以外的輸出)為N=3。像傳統(tǒng)DDS一樣,可編程模數(shù)DDS也要求方程式1中的M為整數(shù)。然而,由于N是可編程的,因此DDS輸出頻率方程式變?yōu)?br />

fO/fS =M/N (2)

方程式2乍看之下平淡無奇,實則頗具意義。考慮選擇特定模數(shù)N=2C的情況,此時可以合成的頻率集與傳統(tǒng)DDS相同。然而,可編程模數(shù)DDS不僅包括傳統(tǒng)DDS的整個頻率集,而且包括許許多多的其他頻率。這是因為,每個特定的N值(從3到2C)都對應(yīng)與M(1≤M<0.5N-1)相關(guān)的所有頻率。對于任何給定的采樣速率,它所代表的可能輸出頻率集遠遠大于傳統(tǒng)DDS。

可編程模數(shù)架構(gòu)的優(yōu)勢在于,幾乎所有的有理數(shù)頻率比都可以合成。例如,現(xiàn)在令M=1、N=1000,就可以精確合成fO=fS/1000的頻率。事實上,不僅可以合成fO=fS/1000,還能合成fS/1000的各次諧波(最高499次,即最高諧波次數(shù)為0.5N-1)。

在發(fā)展可編程模數(shù)的同時保持低功耗絕不是小事一樁。看起來很簡單,只要增加一些額外的邏輯來改造傳統(tǒng)的累加器,迫使它在新模數(shù)值時翻滾,但不要忘了,原來的DDS省電創(chuàng)新涉及到角度-旋轉(zhuǎn)算法,它正是基于累加器模數(shù)為2的冪這一情況而實現(xiàn)高效運行的。當累加器模數(shù)變?yōu)?的冪以外的值時,將無法使用省電的角度-旋轉(zhuǎn)算法。

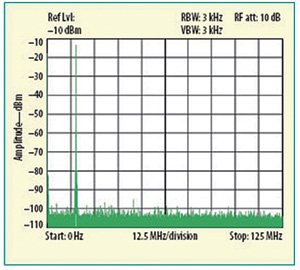

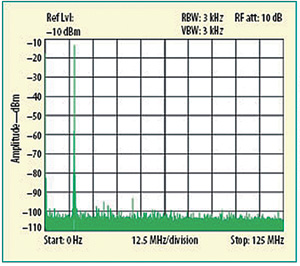

累加器改進的巧妙之處體現(xiàn)在兩方面。第一,它一方面允許模數(shù)變化,另一方面仍然滿足角度-旋轉(zhuǎn)算法的“2的冪”要求。第二,它在實現(xiàn)第一點的同時,將對雜散性能的影響降至最低程度。在圖2和圖3中,頻譜分析儀的掃描頻率范圍均為0~125MHz,AD9913以250MHz的采樣速率工作。圖2中,AD9913配置為傳統(tǒng)DDS,頻率調(diào)諧字為262160001(f0≈15.26MHz),這是傳統(tǒng)DDS能夠?qū)崿F(xiàn)的最接近M/N=1000/16383的值。圖3則使用可編程模數(shù)設(shè)置。兩種情況的頻率差僅為大約0.00136Hz(約1MHz)。除了雜散成分略有不同外,兩條跡線看起來幾乎完全一致。

圖2 標準DDS技術(shù)的調(diào)諧限制

圖3 AD9913的可編程模塊調(diào)諧能力

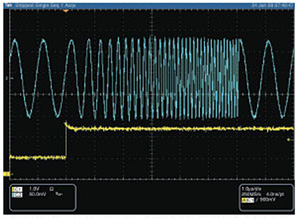

盡管功耗非常低,但AD9913并未減損波形發(fā)生能力,仍然能夠產(chǎn)生線性頻率或相位隨時間而以斜坡形式變化的波形。用戶設(shè)置起點和終點(頻率為32位,相位為14位)。兩個斜坡方向(從起點到終點和從終點到起點)的步長和步進速率參數(shù)都是可以獨立編程的。利用這些控制參數(shù)和其他用戶控制的特性,可以產(chǎn)生多種多樣的調(diào)制輸出信號。圖4所示為波形發(fā)生能力的一個示例,顯示了頻率在6μs內(nèi)從1MHz掃描到10MHz的時域圖(6kHz步長、4ns間隔)。下方跡線的上升沿表示頻率掃描的起點。到達10MHz后,器件折回并保持1MHz,因此跡線非常清楚地顯示了頻率掃描的終點。

圖4 ADS9913掃頻產(chǎn)生的時域波形

AD9913也集成了參考時鐘乘法器,支持設(shè)計人員使用低頻時鐘源。除了直接利用高頻時鐘源來驅(qū)動該器件外,設(shè)計人員還可以將低頻時鐘源或晶體諧振器與AD9913集成的PLL(1X至64X)頻率乘法器一起使用,產(chǎn)生所需的250 MHz內(nèi)部采樣時鐘。采樣直接時鐘信號時,AD9913的參考時鐘(REFCLK)輸入端口接受差分或單端信號源。