關(guān)鍵字:89C55 圖像處理

隨著圖像處理技術(shù)應用的普及,其應用范圍越來越廣。在醫(yī)學、軍事、公安等領(lǐng)域,特別是近些年在工業(yè)自動化、工業(yè)檢測方面得到廣泛應用。目前的圖像處理系統(tǒng)大多采用計算機加上視頻采集卡和攝像頭來構(gòu)成其硬件系統(tǒng),這種硬件結(jié)構(gòu)對于處理自滿不復雜的簡易圖像處理系統(tǒng)顯然是不合適的。

目前,EPLD芯片內(nèi)部的資源越來越多,速度越來越快,開發(fā)的軟件功能也更加完善,使其應用逐步擴大。人們普遍認為,今后的許多電子系統(tǒng),將以CPU+RAM+EPLD的結(jié)構(gòu)為特征。圖像系統(tǒng)將向小型化發(fā)展。如何設計一套簡單的、低成本的圖像處理系統(tǒng)是將圖像處理技術(shù)應用到更廣的領(lǐng)域的迫切要求。

本文介紹的系統(tǒng)正是針對這樣的需求而開發(fā)出來的。

1 總體設計方案

整個系統(tǒng)由攝像頭、圖像輸入單元、圖像存儲單元、圖像處理單元、圖像顯示單元及驅(qū)動控制單元幾部分組成。圖像處理系統(tǒng)框圖如圖1所示。

該圖像處理系統(tǒng)采用Atmel的89C55為中央處理單元,系統(tǒng)時鐘為20MHz。圖像采集部分由ISPLSI1032E提供存儲圖像RAM的地址信號和采集圖像點陣的時鐘信號。根據(jù)需要每幀圖像可分為256×256或512×512點陣,在特殊情況下也可采用256×128或512×256半屏方式。在圖像輸出單元,可將圖像與顯示菜單迭加輸出,構(gòu)成可視菜單。

另外,為適應工業(yè)檢測和工業(yè)自動化方面的應用,在系統(tǒng)中還設計了驅(qū)動控制電路,可以輸出開關(guān)量和模擬量。基本上能夠適應各種控制場合。

2 硬件電路設計

2.1 ISP器件開發(fā)

ISP器件除具有一般PLD器件所具有的易用性、高性能和FPGA的靈活性、高密度外,最重要的一條是它的在系統(tǒng)可編程技術(shù),即ISP可以在空白的狀態(tài)下焊接到電路板上。任何已經(jīng)安裝好ISP器件的電路板,只要通過PC機和下載電纜,就能升級新的編程代碼,并且一切工作可在不斷電的前提下進行。

ISP(In SYSTEM PROGRAMMING)技術(shù)是LATTICE半導體公司首先提供出來的一種能在產(chǎn)品設計、制造過程中的每個環(huán)節(jié),甚至在產(chǎn)品賣給最終用戶以后,隨時對其器件、電路板或整個電子系統(tǒng)的邏輯和功能進行組態(tài)或重組的最新技術(shù)。

在系統(tǒng)開發(fā)過程中,圖像采集的核心部分是視頻信號經(jīng)A/D轉(zhuǎn)換的結(jié)果如何存儲到存儲器中,即如何根據(jù)視頻信號產(chǎn)生存儲器的地址信號。經(jīng)過對所需邏輯門數(shù)量的估算,我們采用ISPLSI1032為地址發(fā)生器和其它一些邏輯電路。

2.2 圖像采集時序的產(chǎn)生

這里,以256×128點陣為例,說明圖像采集時序的產(chǎn)生。

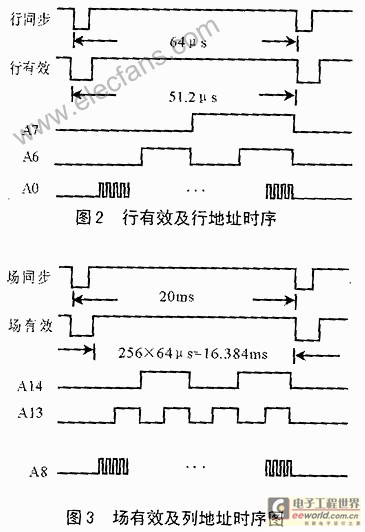

以A0~A7表示每行中點陣的地址,A8~A14表示行地址。其行有效信號和A0~A7地址的時序如圖2所示,其場有效信號和A8~A14地址的時序如圖3所示。這樣共用256×128=32

768個存儲單元存儲1幅圖像。

如果需要采集圖像,由由CPU給ISP發(fā)出START信號,令I(lǐng)SP斷開CPU提供給圖像RAM的地址線,改由ISP產(chǎn)生圖像RAM的地址A0~A14。SIP產(chǎn)生完1幅圖像的地址后,輸出1個END信號,通知CPU采圖完畢,并讓出RAM的地址線和數(shù)據(jù)線給CPU,供其進行圖像處理。

系統(tǒng)中共有4片32K×8bit的RAM(62256),其中:

RAM1為圖像幀存;

RAM2為圖形標志位,用于圖像的標注;

RAM3為菜單界面的顯存;

RAM4為系統(tǒng)內(nèi)存,用來存儲處理的中間數(shù)據(jù)和處理結(jié)果。

圖4為圖像采集部分原理圖。

在實際使用中,CPU對RAM1、RAM4與RAM2、RAM3的操作是分時進行的。在掃描期,CPU對RAM1和RAM4進行操作,進行圖像的計算和結(jié)果處理;而在回掃期,則進行菜單和標注的刷新。ISP對RAM2和RAM3的操作是在掃描期,進行菜單和標注與圖像的合成輸出。

ISPEXPERT的LATTICE公司于20世紀90年代末推出的一套完整的ISP集成開發(fā)環(huán)境。它有500個宏元件可供調(diào)用,支持VHDL、Verilog-HDL、ABELHDL和原理圖編譯器一體的開發(fā)軟件;可用于ISP器件的邏輯設計和優(yōu)化、邏輯映射、自動布局布線、生成熔絲圖文件和編程下載。此外,它還可以對設計的數(shù)字系統(tǒng)進行功能仿真、時序仿真和靜態(tài)時序分析。

從使用者的角度看,ISPEXPERT比Workview office和Synario軟件功能更強大,操作更方便。

本系統(tǒng)采用ISP1032E芯片省略了復雜的、大量的邏輯電路,利用VHDL語言編程,通過ISPEXPERT集成開發(fā)環(huán)境開發(fā),既節(jié)省了大量的硬件調(diào)試時間,又減少了線路間的相互干擾。更重要的是節(jié)省了重復制板的時間,大大縮短了產(chǎn)品開發(fā)周期。

結(jié)束語

基于ISP和單片機構(gòu)成的圖像處理系統(tǒng),具有結(jié)構(gòu)簡單、集成度高、體積小、價格低廉等特點,尤其適用于具有圖像處理功能的嵌入式系統(tǒng)的開發(fā)。本系統(tǒng)已在實際中使用,取得了良好的效果。