1 概述

印品質(zhì)量檢測(cè)系統(tǒng)是一種基于視覺(jué)在線的檢測(cè)系統(tǒng),通過(guò)攝像機(jī)在線掃描印品圖像,然后送至內(nèi)存通過(guò)圖像處理軟件處理,結(jié)果與標(biāo)準(zhǔn)數(shù)據(jù)比較,找出兩者之間的差異并分析產(chǎn)生誤差原因,進(jìn)而重新設(shè)計(jì)參數(shù)。實(shí)際中,通常需要對(duì)大面積印品進(jìn)行高精度的檢測(cè),而單個(gè)攝像頭只適于攝取小范圍的圖像,為了保證精度、同步測(cè)量、協(xié)作狀態(tài)檢測(cè),本文使用了多個(gè)CCD攝像頭同步獲取不同位置信息,利用CPLD的邏輯控制功能配合PCI總線以DMA方式同步傳輸數(shù)據(jù)供上層的應(yīng)用軟件對(duì)采集到的數(shù)據(jù)進(jìn)行實(shí)時(shí)處理。從而很好地滿足尺寸、精度和實(shí)時(shí)性的要求。

2 系統(tǒng)硬件結(jié)構(gòu)與工作原理

系統(tǒng)框圖如圖1所示,該圖像采集系統(tǒng)由四路CCD相機(jī)、PCI圖像采集卡和計(jì)算機(jī)組成。其中,四路高速CCD攝相機(jī)同步獲取大面積被檢測(cè)印紙圖像信息;PCI多路采集卡由PCI接口芯片、配置EEPROM、CPLD邏輯控制芯片、高速緩存(FIFO)、視頻解碼芯片等構(gòu)成,主要實(shí)現(xiàn)CCD圖像的采集、緩存和傳輸;PC機(jī)完成采集工作的控制、圖像數(shù)據(jù)的傳輸控制、圖像處理、存儲(chǔ)及在顯示器上顯示的功能。

其工作原理如下:PC機(jī)應(yīng)用程序通過(guò)PCI總線向CPLD控制邏輯電路發(fā)出“采集開(kāi)始”命令,CPLD控制邏輯收到開(kāi)始采集指令后通過(guò)虛擬I2C總線控制方式來(lái)控制四路視頻解碼器開(kāi)始解碼,解碼后同步輸出的高速圖像數(shù)據(jù)及同步信號(hào)到FIFO數(shù)據(jù)輸入端緩存,當(dāng)存儲(chǔ)空間將要滿時(shí),向PCI總線控制器發(fā)出中斷請(qǐng)求信號(hào),PCI總線控制器將中斷信號(hào)轉(zhuǎn)發(fā)到PCI圖像采集卡,PC機(jī)響應(yīng)此中斷信號(hào),通過(guò)PCI總線控制器讀取FIFO中的數(shù)據(jù),直至讀取FIFO空為止,數(shù)據(jù)經(jīng)由PCI總線,以DMA方式將圖像數(shù)據(jù)快速送入計(jì)算機(jī)的內(nèi)存緩沖區(qū),由應(yīng)用程序根據(jù)需要提供對(duì)其進(jìn)行數(shù)據(jù)圖像處理,及在屏幕上顯示處理后的結(jié)果。

系統(tǒng)由硬件部分和軟件部分構(gòu)成。硬件部分設(shè)計(jì)主要指四路CCD攝像機(jī)圖像采集卡的電路設(shè)計(jì)、CPLD的邏輯控制功能設(shè)計(jì);軟件部分設(shè)計(jì)包括底層的設(shè)備驅(qū)動(dòng)程序設(shè)計(jì)和上層的應(yīng)用程序設(shè)計(jì),其功能是控制硬件電路實(shí)現(xiàn)對(duì)四路CCD圖像數(shù)據(jù)的采集、圖像處理、存儲(chǔ)和顯示。

3 系統(tǒng)各功能模塊介紹

3.1 CCD選型

CCD器件采用加拿大DALSA公司的IL-E2線陣2048像素的TDICCD,它以3500行/s速度對(duì)印品逐行掃描。四路CCD相機(jī)通道同步采樣,采樣信號(hào)數(shù)據(jù)塊大小默認(rèn)為:20484150=1.17Mb。這里150為掃描行數(shù)(根據(jù)五號(hào)字體計(jì)算得出),行數(shù)程序可調(diào),即掃描塊面積可調(diào)。掃描這樣一幅圖像所需要的時(shí)間為150/3500=42.85ms。

3.2 PCI接口設(shè)計(jì)

PCI接口是外部總線與PCI總線的通信接口,完成PCI總線與外部總線間的通信,PCI總線協(xié)議復(fù)雜,接口電路實(shí)現(xiàn)比較困難。目前實(shí)現(xiàn)PCI接口的方案一般分為兩種:一種是全部用可編程邏輯器件完成;另一種是用PCI接口芯片與邏輯電路配合實(shí)現(xiàn)。相對(duì)而言,后者設(shè)計(jì)簡(jiǎn)單,開(kāi)發(fā)周期短,兼容性好。本系統(tǒng)采用AMCC公司專(zhuān)用的PCI接口芯片AMCCS5933,其復(fù)雜的PCI接口規(guī)范完全由S5933實(shí)現(xiàn),只需將其PCI接口信號(hào)與PCI總線相連,不需要額外的驅(qū)動(dòng)電路,從而加快了設(shè)計(jì)進(jìn)程。

采集卡利用S5933通過(guò)DMA實(shí)現(xiàn)采集數(shù)據(jù)的實(shí)時(shí)傳輸。S5933支持3個(gè)物理總線接口,PCI總線、ADD-ON總線及一個(gè)可選的非易失性存儲(chǔ)器總線接口,其中PCI接口完全符合PCI總線規(guī)范,它的引腳和PCI總線信號(hào)一一對(duì)應(yīng),用戶可以根據(jù)自己的需要選擇其中部分管腳和總線相連。用戶真正所需要做的就是設(shè)計(jì)S5933與ADD-ON總線接口相連接的邏輯電路和配置空間的初始化,而不用去考慮PCI總線規(guī)范上面眾多的協(xié)議。

3.3 視頻解碼器

采用Philps公司提供的可編程數(shù)字圖像視頻解碼芯片SAA7110對(duì)視頻圖像信號(hào)進(jìn)行采集,它應(yīng)用I2C總線的配置方式。內(nèi)部包括6通道的模擬輸入,能實(shí)現(xiàn)視頻源的選擇、模數(shù)變換、自動(dòng)嵌位、自動(dòng)增益控制、抗混疊濾波、多制式(PAL、PALN、PALM、NTSCM、NTSC-Japan、NTSC4.43和SECAM)解碼、放大或縮小數(shù)字圖像以及亮度、飽和度和對(duì)比度的控制等。為視頻采集系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)提供了極大的方便。

3.4 高速緩存(FIFO)

高速緩存FIFO,在CCD輸出信號(hào)和S5933之間作為數(shù)據(jù)緩沖,防止數(shù)據(jù)的丟失。采用IDT公司的雙端口異步FIFO IDT7207作為外接FIFO,其容量為32k×9bit(其中8bit是數(shù)據(jù),1bit是做奇偶校驗(yàn))。該FIFO具有很高的存取速度(12ns);標(biāo)準(zhǔn)的滿標(biāo)志位(FF)、空標(biāo)志位(EF),可禁止數(shù)據(jù)繼續(xù)寫(xiě)入或讀出。同時(shí),還有可編程快滿標(biāo)志(PAF)以及可編程快空標(biāo)志(PAE)。

3.5 CPLD邏輯控制電路設(shè)計(jì)

采用Altera公司的MAX7000A系列的復(fù)雜可編程邏輯器件(CPLD)EPM7128A芯片實(shí)現(xiàn)數(shù)據(jù)傳輸通道的邏輯控制,完成對(duì)四路CCD攝像機(jī)控制、FIFO控制以及S5933的控制。利用QuartusII6.0軟件進(jìn)行設(shè)計(jì)、調(diào)試、和仿真,實(shí)現(xiàn)各種復(fù)雜的組合邏輯和時(shí)序邏輯,大大提高了控制電路的集成度。

3.5.1 CPLD對(duì)四路視頻解碼器的控制

對(duì)四路SAA7110,我們?cè)O(shè)計(jì)了利用CPLD虛擬I2C總線技術(shù)來(lái)實(shí)現(xiàn)SAA7110的初始化控制。首先根據(jù)I2C總線的原理寫(xiě)出啟動(dòng)、結(jié)束、發(fā)送應(yīng)答信號(hào)及讀、寫(xiě)一個(gè)字節(jié)的程序,然后根據(jù)SAA7110的寄存器操作格式寫(xiě)出讀、寫(xiě)寄存器的程序,最后根據(jù)以上子程序?qū)懗龀跏蓟绦騿T段。系統(tǒng)復(fù)位完成CPLD程序加載,先由CPLD的I2C總線模塊對(duì)SA7110初始化,然后等待采集圖像的命令。初始化成功后,SAA7110實(shí)時(shí)處理模擬視頻信號(hào),輸出亮度和色度信號(hào),同時(shí)輸出像素時(shí)鐘信號(hào),行、場(chǎng)同步信號(hào)和參考信號(hào)等。本系統(tǒng)只需要灰度圖像,不用色度信號(hào),所以數(shù)據(jù)線為8位。

3.5.2 CPLD對(duì)FIFO的控制

對(duì)FIFO的控制主要是涉及到讀取數(shù)據(jù)的時(shí)序匹配和FIFO存儲(chǔ)器滿或空后的電路控制問(wèn)題。從SAA7110來(lái)的數(shù)據(jù),當(dāng)幀同步信號(hào)VSYNC由低變高時(shí),表示一個(gè)有效的數(shù)據(jù)幀開(kāi)始,在每幀數(shù)據(jù)的開(kāi)頭,CPLD都要置FIFO復(fù)位,同時(shí)設(shè)置偏移量。然后等待行同步信號(hào)HSYNC由低變高(表示輸出一行有效數(shù)據(jù)),忽略開(kāi)頭和末尾幾十個(gè)時(shí)鐘周期內(nèi)的無(wú)效數(shù)據(jù),取中間2048個(gè)有效像元,在每個(gè)像元時(shí)鐘PIXCLX的下降沿采集像元數(shù)據(jù)。

CPLD對(duì)采集到的四路有效像元數(shù)據(jù)具體操作為:CPLD將像元數(shù)據(jù)放到FIFO輸入數(shù)據(jù)線上,同時(shí)設(shè)定FIFO的寫(xiě)允許信號(hào)W#有效,并給出WCLK信號(hào),在WCLK信號(hào)的上升沿把FIFO輸入數(shù)據(jù)線上的數(shù)據(jù)存入FIFO。當(dāng)本行的數(shù)據(jù)傳輸完畢,HSYNC就變低,等HSYNC再次變高,即下一行數(shù)據(jù)到來(lái)時(shí)再開(kāi)始對(duì)下一行的像元數(shù)據(jù)進(jìn)行同樣的操作。這里置W#信號(hào)有效與否要受FIFO滿信號(hào)(FF#)控制,如果FIFO已滿則W#信號(hào)無(wú)效,即只有在FIFO不滿的情況下才能將數(shù)據(jù)寫(xiě)入。當(dāng)VSYNC和HSYNC都變低時(shí),表示一幀數(shù)據(jù)輸出完畢。當(dāng)VSYNC再次變高,就可以開(kāi)始下一幀圖像的采集了。

3.5.3 CPLD對(duì)S5933的控制

由于SAA7110來(lái)的數(shù)據(jù)位為8位,我們把S5933的32位數(shù)據(jù)線分四路分別與四路8位數(shù)據(jù)線相接。當(dāng)S5933發(fā)起一次DMA讀FIFO數(shù)據(jù)到計(jì)算機(jī)時(shí),則CPLD置FIFO讀允許(REN)、輸出允許(OE)有效,同時(shí)給出讀時(shí)鐘(RCLK),在RCLK的每一個(gè)上升沿,F(xiàn)IFO會(huì)把內(nèi)部存儲(chǔ)中的圖像數(shù)據(jù)輸出到S5933的數(shù)據(jù)線上,這里RCLK信號(hào)的給出與否受FIFO空信號(hào)(FE#)的控制,如果FIFO已經(jīng)為空,則RCLK信號(hào)不應(yīng)該給出,即只有在FIFO非空的情況下才能將其中數(shù)據(jù)讀出。此后的處理由S5933來(lái)實(shí)現(xiàn)。

3.6 串行EEPROM的配置

系統(tǒng)上電后,PCI總線的RST#信號(hào)有效,同時(shí),S5933輸出局部復(fù)位信號(hào)DEVSET#,并且檢查EEPROM是否存在,若存在,則S5933根據(jù)預(yù)先燒入EEPROM的內(nèi)容設(shè)置內(nèi)部寄存器,否則設(shè)為缺省值,PCI配置寄存器只能通過(guò)EEPROM或PCI主機(jī)CPU進(jìn)行設(shè)置,因此有必要要對(duì)寄存器進(jìn)行說(shuō)明。要注意各屬性寄存器和控制寄存器的設(shè)置不要前后矛盾,地址范圍和基址寄存器的設(shè)置要符合要求。EEPROM的內(nèi)容很重要,它直接關(guān)系到PCI圖像采集卡能否正常工作。

系統(tǒng)選用2K的ST93CS56串行EEPROM作為S5933的配置芯片,其中存儲(chǔ)的是廠家標(biāo)識(shí)、設(shè)備標(biāo)識(shí)以及局部總線的基地址空間、I/O空間、中斷控制信號(hào)等信息。

4 系統(tǒng)軟件設(shè)計(jì)

系統(tǒng)的軟件設(shè)計(jì)包括兩部分:底層的設(shè)備驅(qū)動(dòng)程序和上層的應(yīng)用程序設(shè)計(jì)。

編寫(xiě)驅(qū)動(dòng)程序需要開(kāi)發(fā)環(huán)境的支持,現(xiàn)在流行的開(kāi)發(fā)環(huán)境有:Device Driver Kit,DDK系列、DriverStudio系列和WinDriver系列,由于開(kāi)發(fā)套件對(duì)底層函數(shù)的封裝要引入額外的延時(shí),所以對(duì)于這種實(shí)時(shí)性強(qiáng)、高質(zhì)量的設(shè)備,我們選擇Microsoft提供的DDK。

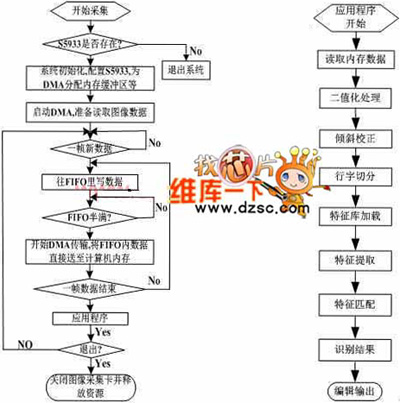

底層的設(shè)備驅(qū)動(dòng)軟件編程主要對(duì)PCI接口芯片S5933進(jìn)行相關(guān)的底層操作,如:向系統(tǒng)申請(qǐng)物理地址連續(xù)的內(nèi)存塊;為采集卡申請(qǐng)板上中斷;設(shè)備的初始化;端口的讀寫(xiě)操作;內(nèi)存的直接讀寫(xiě)以及中斷的設(shè)置、響應(yīng)和調(diào)用;啟動(dòng)DMA向內(nèi)存送數(shù)據(jù),DMA完成后響應(yīng)DMA中斷,并通知應(yīng)用程序數(shù)據(jù)準(zhǔn)備好等。如圖2驅(qū)動(dòng)程序流程圖。

上層的應(yīng)用程序主要對(duì)采集到的四路CCD圖像數(shù)據(jù)轉(zhuǎn)換成標(biāo)準(zhǔn)Windows位圖文件格式(本文采用了非壓縮格式的BMP文件格式),然后對(duì)位圖文件數(shù)據(jù)進(jìn)行圖像處理及顯示。具體過(guò)程是:首先將由DMA通道從FIFO送到送到內(nèi)存數(shù)據(jù)送入圖像處理模塊,經(jīng)二值化,傾斜校正,行字切分等圖像頂處理操作后,得到待識(shí)文字的點(diǎn)陣,漢字識(shí)別模塊從點(diǎn)陣中提取識(shí)別特征,通過(guò)分類(lèi),精確匹配得出識(shí)別結(jié)果,然后送人編輯模塊進(jìn)行識(shí)別后的人工校對(duì)。

5 結(jié)束語(yǔ)

本文作者創(chuàng)新點(diǎn)是提出了一種基于PCI總線的印品質(zhì)量檢測(cè)系統(tǒng)能實(shí)時(shí)采集和處理、分析多通道數(shù)據(jù),實(shí)現(xiàn)大容量數(shù)據(jù)的傳送。采集卡已制作完成,經(jīng)測(cè)試性能完全達(dá)到設(shè)計(jì)要求,由于采用了專(zhuān)用的PCI接口控制芯片,簡(jiǎn)化了設(shè)計(jì)工作,縮短了設(shè)計(jì)周期。而且現(xiàn)場(chǎng)可編程器件CPLD,實(shí)現(xiàn)了對(duì)PCI、FIFO、虛擬I2C、SA7110的控制,使這一設(shè)計(jì)方案集成度和自動(dòng)化程度高、檢測(cè)控制周期短、人為因素干擾少等優(yōu)點(diǎn),在印品工業(yè)自動(dòng)化中會(huì)起到很重要的作用,有著很好的發(fā)展前景。