摘要:傳統(tǒng)測試儀器普遍存在生產(chǎn)出來后普通用戶難以改變其相對固定的功能,無法滿足多樣性的測量。基于此本文開發(fā)了基于FPGA的可重構(gòu)智能儀器,利用SOPC Builder軟件在FPGA中嵌入了Nios II處理器系統(tǒng),采用可重構(gòu)的應用框架技術利用HAL系統(tǒng)庫進行軟件設計。解決了由于測試對象復雜、測試設備多、測試資源利用率低所造成的測試系統(tǒng)的生產(chǎn)、維修成本過高,資源浪費等問題。

0 引言

傳統(tǒng)測試系統(tǒng)由于專用性強、相互不兼容、擴展性差、缺乏通用化、模塊化,不能共享軟硬件組成,不僅使開發(fā)效率低下,而且使得開發(fā)一套復雜測試系統(tǒng)的價格高昂[1]。目前,傳統(tǒng)的分析儀表正在更新?lián)Q代,向數(shù)字化,智能化方向邁進[2]。改變以往由儀器生產(chǎn)廠家定義儀器功能、用戶只能使用的局面,使用戶可自定義儀器、根據(jù)不同測試需求對儀器進行重構(gòu),已經(jīng)成為現(xiàn)代測試技術發(fā)展的一個重要方面。由于其能夠大大減少測試設備的維修成本、提高資源利用率,可重構(gòu)儀器技術已引起高度重視。

1 可重構(gòu)技術

目前對可重構(gòu)性還沒有形成公認的定義。可重構(gòu)性一般是指在一個系統(tǒng)中,其硬件模塊或(和)軟件模塊均能根據(jù)變化的數(shù)據(jù)流或控制流對結(jié)構(gòu)和算法進行重新配置(或重新設置)。

在可重構(gòu)系統(tǒng)(Reconfigurable System)中,硬件信息(可編程器件的配置信息)也可以像軟件程序一樣被動態(tài)調(diào)用或修改。這樣既保留了硬件計算的性能,又兼具軟件的靈活性。尤其是大規(guī)模可編程器件FPGA的出現(xiàn),實時電路重構(gòu)思想逐漸引起了學術界的關注[3]。可重構(gòu)的實現(xiàn)技術又很多種方式,包括DSP重構(gòu)技術、FPGA重構(gòu)、DSP+FPGA重構(gòu)、可重組算法邏輯體系結(jié)構(gòu)、可進化硬件(EHW)、本地重構(gòu)/Internet遠程重構(gòu)、SOPC/SOC重構(gòu)。

可重構(gòu)技術具有以下優(yōu)點:

1)可重構(gòu)技術能夠高效地實現(xiàn)特定功能。可重構(gòu)邏輯器件上都是硬連線邏輯,它通過改變器件的配置來改變功能。2)可重構(gòu)技術能夠動態(tài)改變器件配置,靈活滿足多種功能的需求。3)可重構(gòu)技術適合惡劣工作環(huán)境下的應用。利用可重構(gòu)邏輯器件的一個優(yōu)勢是不需要微處理器必需的散熱系統(tǒng),大大減少了電子產(chǎn)品占據(jù)的空間。4)可重構(gòu)技術具有強大的技術支持來加速產(chǎn)品開發(fā)。5)可重構(gòu)技術的使用能夠大大降低系統(tǒng)成本。另外,對于不會同時被使用的功能,可考慮利用動態(tài)重構(gòu)技術在不同的需求時段里分別實現(xiàn),做到“一片多用”,節(jié)省了資源、空間和成本。

2 可重構(gòu)智能儀器硬件設計

2.1 可重構(gòu)儀器硬件結(jié)構(gòu)

可重構(gòu)智能儀器技術將先進的微電子技術、半導體技術和微處理器技術引入儀器設計領域,通過構(gòu)建通用的硬件平臺,最終由用戶通過選擇不同的軟件來實現(xiàn)不同的儀器功能,因此軟硬件在可重構(gòu)儀器設計技術中同樣關鍵。

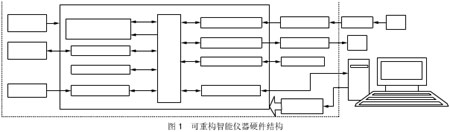

可重構(gòu)智能儀器硬件結(jié)構(gòu)由Nois II處理器系統(tǒng)(包括可重構(gòu)FPGA芯片、FPGA片外系統(tǒng))和計算機組成,其硬件結(jié)構(gòu)框圖如圖1所示。

可重構(gòu)FPGA選用Altera公司Cyclone II系列中的EP2C35F672C6芯片,片外系統(tǒng)主要包括SDRAM存儲器、Flash存儲器、模數(shù)轉(zhuǎn)換芯片、數(shù)模轉(zhuǎn)換芯片、EPC16增強型配置芯片、MAX232芯片等組成。片外系統(tǒng)實現(xiàn)數(shù)據(jù)的采集、預處理、存儲和輸出等功能。

2.2 控制核

在基于FPGA的可重構(gòu)智能儀器中,EP2C35F672C6是整個系統(tǒng)的核心,為了實現(xiàn)FPGA與其他芯片、器件的正確通信、數(shù)據(jù)交換,需要在FPGA上配置Nios II軟核處理器以及其他控制器核。

(一) Nios II嵌入式處理器的設置。首先在Quartus II下建立一個Project,在SOPC Builder中選擇組件列表中的Nios II Processor-Altera Corporation,考慮到芯片的性能以及資源利用率,選擇Nios II/s(標準型)CPU,在Cache & Tightly Coupled Memories標簽下設置Instruction Cache為4KB。在JTAG Debug Module標簽下選擇Level 3,可設置2個硬斷點、2個數(shù)據(jù)觸發(fā)、指令跟蹤和片上系統(tǒng)。整個Debug模塊將占用2400~2700個LE,4個M4K。

(二) 添加SDRAM控制器內(nèi)核。在SOPC Builder組件選擇欄中選擇Avalon Components→Memory→SDRAM Controller,加入SDRAM控制器核,。在Data Width(數(shù)據(jù)總線寬度)下拉列表框中選擇16Bits,其余設置不變,因為都滿足SDRAM芯片IS42S16400的參數(shù)要求。Timing選項卡的參數(shù)也滿足芯片要求,不必修改。

(三) 添加FLASH控制器。在對硬件系統(tǒng)進行編程控制時,F(xiàn)lash用于存儲應用程序。在SOPC Builder的組件選擇欄中選擇Avalon Components→Bridge→Avalon Tri-State Bridge,加入Avalon三態(tài)總線橋;在SOPC Builder的組件選擇欄中選擇AvalonComponents→Memery→Flash Memery(Common Flash Interface),添加CFI控制器。

( 四) 定時器設置。在SOPC Builder組件選擇欄中選擇Avalon Components→Other→Interval timer,加入定時器核。定時器的硬件配置選項會影響定時器的硬件結(jié)構(gòu),SOPC提供了簡單周期中斷配置、完全功能配置和看門狗配置三種硬件配置。

(五) 添加SPI核。采用的A/D轉(zhuǎn)換芯片和D/A轉(zhuǎn)換芯片都是基于SPI總線進行數(shù)據(jù)傳輸?shù)模獙崿F(xiàn)Nios II系統(tǒng)對轉(zhuǎn)換芯片的控制必須添加SPI核。在SOPC Builder組件選擇欄中選擇Avalon Components→Communication→SPI(3 Wire Serial),配置SPI核。由于用到的模數(shù)轉(zhuǎn)換芯片AD7810和數(shù)模轉(zhuǎn)換芯片AD5611對于Nios II系統(tǒng)來說都是從SPI器件,所以在FPGA中添加兩個主SPI核分別控制A/D和D/A轉(zhuǎn)換芯片。

2.3 可重構(gòu)配置文件生成

在完成可重構(gòu)智能儀器的各個控制器核之后,要生成相應的配置文件,才能配置FPGA芯片,使其實現(xiàn)各種功能。

配置是對FPGA的內(nèi)容進行編程的一個過程。目前大部分FPGA都是基于SRAM工藝 的,而SRAM工藝的芯片在掉電后信息就會丟失,需要外加專用配置芯片,在上電時,由這個專用配置芯片把配置數(shù)據(jù)加載到FPGA中,之后FPGA就可以正常工作了。

在被動模式(PS)方式下,F(xiàn)PGA處于完全被動的地位。FPGA接收配置時鐘、配置命令和配置數(shù)據(jù),給出配置的狀態(tài)信號以及配置完成指示信號等。PS配置時序如圖2所示:

根據(jù)SOPC Builder中對FPGA添加的各種控制器核,利用Quatus II軟件例化Nios II處理器,生成了完整的FPGA內(nèi)部頂層模塊圖,如圖3所示。然后利用引腳規(guī)劃器Pin Planner對其進行引腳分配。最后用進行Compilation,生成.sof和.pof配置文件,完成硬件設計。

2.4 外圍電路設計

外圍電路設計包括存儲器設計、AD轉(zhuǎn)換電路設計、DA轉(zhuǎn)換設計、顯示電路設計、開關量DI、DO設計和RS232通信設計等。

儀器上的存儲器包含1片8M字節(jié)的SDRAM和一片32M字節(jié)的FLASH存儲器。限于篇幅SDRAM(IS42S16400)與EP2C35F672C6連接的引腳、FLASH存儲器(AT49BV163)與EP2C35F672C6連接的引腳分配這里不再贅述。

A/D轉(zhuǎn)換電路采用了AD7810芯片、DA轉(zhuǎn)換電路采用AD5611芯片。

DI、DO均為16路,數(shù)字端口滿足標準TTL電氣特性。數(shù)字量輸入最低的高電平為2V,數(shù)字量輸入最高的低電平為0.8V;數(shù)字量輸出最低的高電平為3.4V,數(shù)字量輸出最高的低電平為0.5V。DI、DO部分的電路如圖4所示:

圖4 DI、DO部分電路

3 可重構(gòu)智能儀器軟件設計

3.1 可重構(gòu)儀器軟件結(jié)構(gòu)

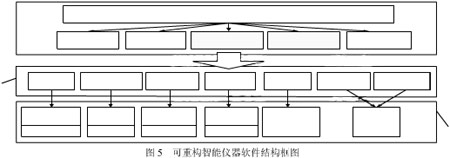

可重構(gòu)智能儀器的軟件結(jié)構(gòu)如圖5所示。

系統(tǒng)軟件模塊庫:包含軟件控制模塊、RS232通訊模塊、模數(shù)轉(zhuǎn)換模塊、數(shù)模轉(zhuǎn)換模塊、顯示模塊和DI、DO開關量模塊。通過軟件控制模塊選擇其他的模塊進行組合就可以實現(xiàn)不同的軟件功能,從而達到重構(gòu)的目的。

HAL程序庫實際上包含了各種不同的硬件驅(qū)動,包括MAX232驅(qū)動、AD轉(zhuǎn)換芯片驅(qū)動、DA轉(zhuǎn)換芯片驅(qū)動、FPGA的I/O引腳驅(qū)動等。

通過選擇軟件模塊庫中的軟件模塊,就可以調(diào)用HAL程序庫中相應的硬件驅(qū)動,從而實現(xiàn)上層應用程序?qū)Φ讓佑布目刂啤\浖K的可重構(gòu)性對應了底層硬件的可重構(gòu)性。

3.2 基于HAL的可重構(gòu)智能儀器軟件開發(fā)

硬件抽象層(HAL,Hardware Abstraction Layer),是指在應用程序和系統(tǒng)硬件之間的一個系統(tǒng)庫(System Library),為嵌入式系統(tǒng)與硬件通信的程序提供簡單的設備驅(qū)動接口。SOPC Builder是一個自動化的SOPC硬件系統(tǒng)工具。基于HAL的軟件系統(tǒng)由兩個Nios II工程所構(gòu)建,用戶的程序包含在一個工程中(用戶應用工程),該工程依賴一個獨立的系統(tǒng)庫工程(HAL系統(tǒng)庫工程)。用戶應用工程包含開發(fā)的所有代碼,編譯該工程可以產(chǎn)生可執(zhí)行文件。HAL系統(tǒng)庫工程包含涉及處理器硬件接口的所有信息。系統(tǒng)庫工程依賴于由SOPC Builder產(chǎn)生的擴展名為.ptf的Nios II處理器系統(tǒng)。

由于該工程的依賴結(jié)構(gòu),如果SOPC Builder生成的系統(tǒng)改變(即.ptf文件已修改),則Nios II IDE管理HAL系統(tǒng)庫并且修改驅(qū)動配置來正確的反應系統(tǒng)硬件。HAL系統(tǒng)庫將用戶程序與底層硬件變化分離開來,這樣,用戶可以不用考慮自己的程序是否與目標硬件匹配來開發(fā)和調(diào)試代碼,簡而言之,基于HAL系統(tǒng)庫的程序和目標硬件是同步的。

由于HAL系統(tǒng)庫中包含有各種不同的硬件驅(qū)動,用戶可以根據(jù)特定的設計需要調(diào)用HAL系統(tǒng)庫中的相應硬件驅(qū)動,從而實現(xiàn)對不同硬件系統(tǒng)的控制,來達到可重構(gòu)設計的目的。本文所設計的基于HAL系統(tǒng)庫的可重構(gòu)智能儀器軟件系統(tǒng)如6示。在系統(tǒng)軟件控制界面中選擇了某一功能后,該功能就會調(diào)用HAL程序庫中相應的一些硬件驅(qū)動,從而實現(xiàn)對硬件設備的控制。

4 系統(tǒng)分析

基于FPGA的可重構(gòu)智能儀器主要是針對目前測試儀器生產(chǎn)出來后功能不能改變、維護 費費用過高、資源浪費嚴重等問題。提出基于FPGA的可重構(gòu)智能儀器的硬件結(jié)構(gòu)和軟件結(jié)構(gòu),實現(xiàn)了八種不同的功能,借鑒虛擬儀器的思想,開發(fā)了基于FPGA的可重構(gòu)智能儀器演示系統(tǒng),該系統(tǒng)具有A/D采集、D/A輸出和開關量控制三種功能。

本文作者創(chuàng)新點:基于SOPC技術進行可重構(gòu)設計;采用了FPGA增強型配置芯片EPC16;軟件重構(gòu)采用了應用框架的復用技術。