文獻(xiàn)標(biāo)識(shí)碼: A

DOI:10.16157/j.issn.0258-7998.2015.10.005

中文引用格式: 陸振林,趙元富,蘭利東,等. 基于可重構(gòu)技術(shù)的DSP任務(wù)動(dòng)態(tài)加載方法研究[J].電子技術(shù)應(yīng)用,2015,41(10):24-26,33.

英文引用格式: Lu Zhenlin,Zhao Yuanfu,Lan Lidong,et al. Research on dynamic loading method of DSP task based on reconfigurable technology[J].Application of Electronic Technique,2015,41(10):24-26,33.

0 引言

隨著微納衛(wèi)星、片上衛(wèi)星的快速發(fā)展,對(duì)其電子系統(tǒng)的微小型化、低功耗的需求日趨明顯。傳統(tǒng)的多模塊拼裝的設(shè)計(jì)模式需要多個(gè)分離電路才能夠構(gòu)建完整的系統(tǒng),顯然,不能滿足未來(lái)的發(fā)展需求。而集成微系統(tǒng)作為扁平化設(shè)計(jì)的新模式,將信息感知、數(shù)據(jù)處理、驅(qū)動(dòng)控制等功能單元,采用MCM、SIP、TSV等封裝技術(shù),集成在一個(gè)芯片大小的封裝體內(nèi),極大地提升了系統(tǒng)的集成度。

為了支撐微系統(tǒng)芯片對(duì)實(shí)時(shí)控制、高性能運(yùn)算的要求。課題組提出了異構(gòu)多核微系統(tǒng)的解決方案。其中,DSP作為協(xié)處理器,主要負(fù)責(zé)計(jì)算任務(wù)的執(zhí)行。為了支撐運(yùn)算任務(wù)類(lèi)的靈活調(diào)度和映射的需求,DSP處理器的任務(wù)動(dòng)態(tài)加載技術(shù)已成為急需突破的關(guān)鍵技術(shù)之一。

文獻(xiàn)[1]通過(guò)SN74LVT16245A(雙向三態(tài)收發(fā)器),將ARM總線和DSP處理器HPI接口進(jìn)行互連,構(gòu)建了ARM與DSP之間視頻數(shù)據(jù)可靠傳輸通道,實(shí)現(xiàn)了大數(shù)據(jù)量的搬移,文獻(xiàn)[2]面向?qū)崟r(shí)圖像處理的運(yùn)算需求,通過(guò)DSP HPI接口,構(gòu)建PowerPC處理器與DSP處理器的通信;文獻(xiàn)[3]設(shè)計(jì)了ARM與DSP HPI的通信接口,通過(guò)162245總線隔離器進(jìn)行數(shù)據(jù)總線的互連,完成了ARM對(duì)DSP程序的動(dòng)態(tài)加載。還有其他的研究人員開(kāi)展過(guò)相似的研究[4-7]。

以上的研究成果表明,通過(guò)HPI接口能夠?qū)崿F(xiàn)ARM處理器與DSP的數(shù)據(jù)交互,但設(shè)計(jì)方案都需要額外增加總線隔離器件來(lái)解決處理器與DSP的總線干擾問(wèn)題。針對(duì)微系統(tǒng)而言,該方法存在以下問(wèn)題:首先,該方法增加了芯片設(shè)計(jì)、測(cè)試的復(fù)雜度,帶來(lái)系統(tǒng)體積和功耗的增加;其次,ARM處理器的總線時(shí)序與國(guó)產(chǎn)處理器并不相同;最后,研究中對(duì)數(shù)據(jù)總線進(jìn)行了隔離,但是ARM的地址線、總線控制信號(hào)等與HPI直連的方式,在DSP處理器出現(xiàn)異常時(shí),將有可能造成對(duì)主處理器總線信號(hào)的影響,導(dǎo)致主處理器無(wú)法正常工作。

因此,本課題提出了一種“基于可重構(gòu)技術(shù)的DSP任務(wù)動(dòng)態(tài)加載技術(shù)”的方法。該方案針對(duì)芯片級(jí)微系統(tǒng)對(duì)任務(wù)動(dòng)態(tài)加載的需求,基于可編程邏輯器件自身資源,采用可重構(gòu)技術(shù),通過(guò)突破并行配置接口設(shè)計(jì)、數(shù)據(jù)動(dòng)態(tài)加載等關(guān)鍵技術(shù),解決異構(gòu)多核芯片中DSP處理器的動(dòng)態(tài)加載的問(wèn)題。

1 基于可重構(gòu)技術(shù)的注入通路設(shè)計(jì)

異構(gòu)多核微系統(tǒng)芯片集成了國(guó)產(chǎn)SPARC V8處理器、FT-DSP處理器、FPGA、SDRAM、SRAM等器件。為了實(shí)現(xiàn)SPARC V8處理器向DSP處理器動(dòng)態(tài)注入程序,并可控制其進(jìn)行啟動(dòng)。文中利用了FT-6713的HPI接口(Host Port Interface)。HPI是一個(gè)并行端口,是外部主機(jī)(host)與DSP系統(tǒng)進(jìn)行數(shù)據(jù)交換以及host配置各個(gè)外設(shè)寄存器的接口,可實(shí)現(xiàn)高速、并行的數(shù)據(jù)通信。FT-6713的HPI是16位寬的并行接口,V8處理器可通過(guò)HPI直接訪問(wèn)FT-6713的存儲(chǔ)空間和外圍設(shè)備。HPI接口信號(hào)如表1所示。

在通過(guò)HPI接口對(duì)DSP存儲(chǔ)空間的訪問(wèn)時(shí),需要解決如下問(wèn)題:

(1)V8處理器與HPI接口互聯(lián)的設(shè)計(jì):由于V8處理器不存在與HPI接口相匹配的接口,需要采取合適的互連方法,以滿足HPI操作的時(shí)序要求;

(2)HPI總線與V8總線串?dāng)_問(wèn)題:在接口互連時(shí),需要將總線信號(hào)、控制信號(hào)與HPI接口進(jìn)行連接,當(dāng)總線都進(jìn)行操作時(shí),將無(wú)法避免地帶來(lái)數(shù)據(jù)的串?dāng)_,甚至導(dǎo)致任務(wù)執(zhí)行崩潰。

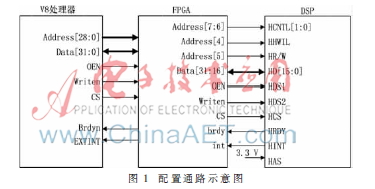

本文結(jié)合HPI接口時(shí)序和V8處理器的總線時(shí)序,提出了如下的互連方案:

(1)V8處理器具有獨(dú)立的地址和數(shù)據(jù)總線,因此,DSP的HPI接口的HAS由外部上拉至高電平。

(2)V8處理器的讀使能信號(hào)(OEN)、寫(xiě)使能信號(hào)(Writen)、IO空間片選信號(hào)(CS)分別連接到DSP的HPI接口上3個(gè)觸發(fā)信號(hào)HDS1、HDS2和HCS,而HDS1、HDS1、HCS共同產(chǎn)生HPI使能觸發(fā)信號(hào)。

(3)V8處理器的地址線ADDR[7:6]與HPI的控制信號(hào)HCNTL[1:0]互連,以決定對(duì)HPI接口進(jìn)行操作的目標(biāo)寄存器,如HPIC、HPIA或HPID。

(4)V8處理器的地址線ADDR[4]與HPI的控制信號(hào)HHWIL互連,以此來(lái)指示當(dāng)前數(shù)據(jù)總線傳輸?shù)淖止?jié)順序。

(5)V8處理器的地址線ADDR[5]與HPI的HR/W互連,用于控制當(dāng)前操作是在對(duì)DSP的HPIA、HPIC、HPID寄存器執(zhí)行何種操作。

(6)V8處理器的Brdyn信號(hào)上與HPI的HRDY互連,用于表明HPI是否已準(zhǔn)備好傳輸數(shù)據(jù)。

(7)V8處理器的外部中斷與HPI的HINT信號(hào)互連,向主機(jī)發(fā)出中斷信號(hào)。

為了避免額外增加隔離芯片所帶來(lái)的各種弊端,本課題提出了基于芯片內(nèi)部FPGA的可重構(gòu)實(shí)現(xiàn)方案。在需要進(jìn)行DSP加載時(shí),通過(guò)動(dòng)態(tài)重構(gòu)技術(shù),在FPGA中加載并實(shí)現(xiàn)DSP HPI互聯(lián)隔離邏輯,構(gòu)建DSP的配置通路,當(dāng)V8處理器完成對(duì)DSP程序加載后,V8處理器控制FPGA對(duì)隔離邏輯進(jìn)行再次重構(gòu),斷開(kāi)DSP HPI接口與V8處理器的總線互聯(lián)通路,以保證DSP處理器的異常不會(huì)對(duì)V8處理器造成影響。其連接示意圖和FPGA內(nèi)部邏輯如圖1所示。

2 DSP任務(wù)的動(dòng)態(tài)加載

2.1 動(dòng)態(tài)啟動(dòng)模式

通過(guò)HPI接口對(duì)FT-6713處理器的程序注入和啟動(dòng),需要持續(xù)對(duì)FT-6713處理器的3個(gè)寄存器進(jìn)行操作,即HPI控制寄存器(HPIC)、HPI地址寄存器(HPIA)、HPI數(shù)據(jù)寄存器(HPID)。

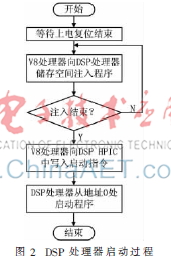

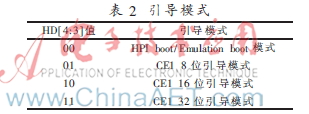

圖2顯示了HPI的啟動(dòng)流程。系統(tǒng)上電復(fù)位后,首先采樣HPI接口的HD[4:3]的狀態(tài)確定啟動(dòng)方式(即引導(dǎo)模式),如表2所示。為了能夠動(dòng)態(tài)加載和啟動(dòng),本方法選擇HPI啟動(dòng)模式,即HD[4:3]上電時(shí)默認(rèn)為低電平。

FT-6713上電后,芯片外設(shè)控制器首先啟動(dòng),內(nèi)核處于掛起狀態(tài);此時(shí)外部主機(jī)通過(guò)HPI接口對(duì)DSP進(jìn)行配置, 通過(guò)HPI初始化DSP的CPU core和EMIF,并向DSP加載程序和數(shù)據(jù),將代碼和數(shù)據(jù)加載到DSP的內(nèi)存中,在這期間DSP內(nèi)核保持掛起狀態(tài)不變;當(dāng)主機(jī)完成程序加載后,主機(jī)向HPIC寄存器中的DSPINT位寫(xiě)1,向DSP發(fā)出中斷;DSP收到中斷后,DSP內(nèi)核從掛起狀態(tài)喚醒,從0地址處啟動(dòng),開(kāi)始執(zhí)行程序。

2.2 基于軟件驅(qū)動(dòng)的程序加載

V8處理器向DSP處理器注入程序,通過(guò)HPIC、HPIA、HPID和16位數(shù)據(jù)線與DSP進(jìn)行數(shù)據(jù)交換和中斷控制。DSP處理器程序注入的實(shí)現(xiàn)流程如圖3所示。

(1)初始化HPIC

HPIC寄存器用于控制HPI的握手信號(hào)使能HRDY、字節(jié)傳輸順序控制等。初始化該配置寄存器后,使HPI控制器進(jìn)入V8所需的工作模式。

(2)初始化HPIA

通過(guò)向該地址寄存器寫(xiě)入待注入數(shù)據(jù)的地址,以便HPI控制器將相應(yīng)的數(shù)據(jù)輸出到相應(yīng)的存儲(chǔ)區(qū)。

(3)向HPID寫(xiě)入數(shù)據(jù)

HPID用于暫存由V8處理器注入的配置信息,寫(xiě)入方式具有自增寫(xiě)入模式和固定寫(xiě)入模式。由HCNTL[1:0]信號(hào)控制。本文選擇自增寫(xiě)入模式。

(4)HPI啟動(dòng)

當(dāng)數(shù)據(jù)全部寫(xiě)入DSP所屬存儲(chǔ)空間后,需要再次訪問(wèn)HPIC,并向其DSPINT位寫(xiě)入1來(lái)喚起DSP內(nèi)核的啟動(dòng)和程序的加載。

在程序啟動(dòng)過(guò)程中,DSP會(huì)從0地址處開(kāi)始執(zhí)行。對(duì)于DSP的任務(wù)程序來(lái)說(shuō),是從c_int00處開(kāi)始執(zhí)行,需要使得程序跳轉(zhuǎn)到_c_int00處。

在生成和編譯DSP待注入程序,以及通過(guò)FPGA對(duì)HPI接口操作時(shí),需要注意如下事項(xiàng):

(1)由于項(xiàng)目中使用HPI16模式,因此對(duì)HPI任何一個(gè)寄存器的訪問(wèn),主機(jī)都需在HPI總線上進(jìn)行2次半字存取。

(2)DSP的程序在下載的同時(shí)需要鏈接初始化的變量,因此需要在.cmd文件中使用-cr選項(xiàng)。

(3)FT-6713 DSP編譯器生成的文件為.out文件,構(gòu)建動(dòng)態(tài)加載數(shù)組時(shí),對(duì).out文件中有效配置信息進(jìn)行提取。

3 測(cè)試

為了驗(yàn)證所提出的動(dòng)態(tài)加載方法的功能和性能,進(jìn)行相關(guān)測(cè)試。V8處理器系統(tǒng)時(shí)鐘為80 MHz,DSP處理器內(nèi)核運(yùn)行時(shí)鐘為96 MHz。

3.1 功能測(cè)試

本文采用TEKtronix TLA7012邏輯分析儀對(duì)HPI接口的信號(hào)時(shí)序進(jìn)行了跟蹤,采樣頻率為200 MHz。如圖4所示,左側(cè)兩個(gè)橢圓圈定的32 bit數(shù)據(jù)將寫(xiě)入到HPIC寄存器,右側(cè)兩個(gè)橢圓圈定的第二個(gè)32 bit數(shù)據(jù)將寫(xiě)入到HPIA寄存器中。從測(cè)試數(shù)據(jù)可知,在HPI接口獲取了正確加載的數(shù)據(jù)和時(shí)序。

3.2 性能測(cè)試

為了獲取V8處理器發(fā)起DSP任務(wù)數(shù)據(jù)注入至DSP處理器正確啟動(dòng)的時(shí)間,設(shè)計(jì)了測(cè)試用例:V8發(fā)起程序注入后,拉高GPIO,DSP處理器在正確啟動(dòng)后,所屬GPIO信號(hào)由低到高,兩個(gè)GPIO信號(hào)間的間隔即可認(rèn)為DSP程序注入及啟動(dòng)時(shí)間。如圖5所示為2個(gè)GPIO信號(hào)電平變化的情況。

V8處理器通過(guò)FPGA連接到DSP的HPI接口,并向其注入了大小為280 KB的程序數(shù)據(jù),從圖中可見(jiàn),整個(gè)動(dòng)態(tài)加載和DSP運(yùn)行時(shí)間僅為135 ms。

4 結(jié)論

針對(duì)系統(tǒng)級(jí)異構(gòu)多核芯片的特點(diǎn),協(xié)同工作的設(shè)計(jì)要求,提出了“基于可重構(gòu)技術(shù)的”實(shí)現(xiàn)方法。該方法在無(wú)需增加總線隔離芯片和外部集成電路的情況下,通過(guò)構(gòu)建的映射通路,V8處理器能夠?qū)⑷蝿?wù)正確的注入到DSP處理器存儲(chǔ)空間,并啟動(dòng)DSP處理器內(nèi)核,完成任務(wù)的動(dòng)態(tài)加載。

測(cè)試結(jié)果表明,對(duì)于一個(gè)大小為280 KB的代碼,從代碼注入到DSP內(nèi)核啟動(dòng)完成,所需時(shí)間僅為135 ms,能夠滿足系統(tǒng)的實(shí)時(shí)性要求。本文提出的方法滿足了系統(tǒng)級(jí)芯片任務(wù)動(dòng)態(tài)映射的需求。

參考文獻(xiàn)

[1] 張力,劉正熙.ARM與DSP之間視頻數(shù)據(jù)可靠傳輸?shù)脑O(shè)計(jì)與實(shí)現(xiàn)[J].計(jì)算機(jī)應(yīng)用,2009(29);198-200.

[2] 余躍,孟慶東,李兆麟.一種面向?qū)崟r(shí)圖像處理應(yīng)用的基于非共享存儲(chǔ)的多DSP系統(tǒng)設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2009,35(3):29-32.

[3] 趙建波,胡文若,習(xí)勇,等.基于ARM的TMS320C6455-DSPHPI的動(dòng)態(tài)程序加載設(shè)計(jì)與實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2013,39(6):14-16.

[4] OU S H,LIN T J,DENG X S,et al.Multithreaded copro-cessor interface for multi-core multimedia SoC[C].Design Automation Conference,2008.Asia and South Pacific,2008:115-116.

[5] Yao Yiyong,Zhao Liping,Li Xin,et al.Dual-core embeddedreal-time inspection and analysis platform for field quality control and application[M].Intelligent Robotics and Applica-tions.Springer Berlin Heidelberg,2008.

[6] FAN H,CHEN W,LIU J,et al.The application of HPI in laser scanning system based on dual-DSP[C].4th IEEE Conference on Industrial Electronics and Applications,2009:484-488.

[7] SHANG Q,DU C.A novel measurement system of electric power parameters based on DSP and ARM[C].2009 Inter-national Conference on Measuring Technology and Mecha-tronics Automation,2009:353-356.