1 引言

閃速存儲(chǔ)器(FLASH Memory)以其集成度高,、成本低、使用方便等許多優(yōu)點(diǎn),,廣泛應(yīng)用于通訊設(shè)備,、辦公設(shè)備,、家用電器、醫(yī)療設(shè)備等領(lǐng)域,。利用其保存信息的非易失性和在線更新數(shù)據(jù)參數(shù)的特性,,可將其作為具有一定靈活性的只讀存儲(chǔ)器(ROM)使用。

現(xiàn)在的數(shù)字電路應(yīng)用系統(tǒng)設(shè)計(jì)中,,經(jīng)常遇到大容量的數(shù)據(jù)存儲(chǔ)問(wèn)題,。Flash由于容量大、存儲(chǔ)速度快,、體積小,、功耗低等諸多優(yōu)點(diǎn),而成為應(yīng)用系統(tǒng)中數(shù)據(jù)存儲(chǔ)器件的首選,。由于在研制實(shí)時(shí)信號(hào)處理系統(tǒng)時(shí),,需要一塊大容量的Flash來(lái)存儲(chǔ)坐標(biāo)變換的數(shù)據(jù)作查找表,因此面臨一個(gè)如何對(duì)Flash進(jìn)行編程,,將數(shù)據(jù)寫(xiě)入Flash的問(wèn)題,。由于我們選用的Flash芯片為SST39SF010/020,是最新生產(chǎn)的型號(hào),,需要自己開(kāi)發(fā)編程器來(lái)滿足設(shè)計(jì)需要,,達(dá)到既經(jīng)濟(jì)又實(shí)用的目的。這一型號(hào)的Flash采用的是標(biāo)準(zhǔn)的5V電壓供電,,器件在命令控制下自己產(chǎn)生內(nèi)部的擦除電壓Vpp,,從而完成數(shù)據(jù)的寫(xiě)入和芯片的擦除等各種功能。而FPGA這種大規(guī)模的可編程器件十分適合邏輯電路的設(shè)計(jì),,能方便地控制和產(chǎn)生 Flash編程操作中的各種控制命令,,實(shí)現(xiàn)編程器的功能。

2 Flash的性能參數(shù)和操作時(shí)序

以最新的Flash芯片型號(hào)SST39SF010/020為例,,容量為1/2Mbit(×8),。 它的主要性能有:

● 單一的5.0V電壓讀寫(xiě)操作;

● 高可靠性,,超過(guò)100年的數(shù)據(jù)保持能力,;

● 快速擦除和字節(jié)編程功能

——扇區(qū)擦除時(shí)間典型值只需7ms;

——片擦除時(shí)間典型值只需15ms,;

——字節(jié)編程需時(shí)間典型值只需20微秒,;

——片重寫(xiě)時(shí)間需3ms(SST39SF010)

● 片內(nèi)部產(chǎn)生Vpp編程電壓,實(shí)現(xiàn)自動(dòng)讀寫(xiě)時(shí)序,;

● I/O兼容TTL,;

各引腳功能:

Ams~A0:地址輸入 ——提供存儲(chǔ)器地址;

DQ7~DQ0:數(shù)據(jù)輸入/輸出 ——在讀時(shí)序時(shí)輸出數(shù)據(jù),,在寫(xiě)時(shí)序時(shí)接收輸入的數(shù)據(jù),;

CE#:片選使能——當(dāng)CE#為低電平有效,;

OE#:輸出使能——選通輸出緩存器;

WE#:寫(xiě)使能——控制寫(xiě)時(shí)序,;

VDD:接5V電源,;

VSS:接地。

在對(duì)Flash進(jìn)行編程操作前,,必須保證存儲(chǔ)單元為空,。如果不為空,就必須先對(duì)Flash芯片進(jìn)行擦除操作,。由于Flash采用了模塊分區(qū)的陣列結(jié)構(gòu),,使得各個(gè)存儲(chǔ)模塊既可以整個(gè)芯片一齊被擦除,還可以使各個(gè)存儲(chǔ)模塊被獨(dú)立的分別擦除,。只需在地址和數(shù)據(jù)端寫(xiě)入不同的操作命令即可實(shí)現(xiàn)不同的擦除操作,。

SST39SF010的編程操作分三步驟:第一步是連續(xù)載入三字節(jié)命令的軟件數(shù)據(jù)保護(hù)操作,第二步是寫(xiě)入字節(jié)地址和字節(jié)數(shù)據(jù),,在編程操作過(guò)程中,,地址是在CE#或WE#的下降沿時(shí)有效,而數(shù)據(jù)則是在CE#或WE#的上升沿時(shí)有效,;第三步是芯片內(nèi)部的編程操作,,該操作在CE#或WE#的第四個(gè)上升沿有效,隨后該內(nèi)部編程操作在30微秒內(nèi)即可完成,。

FLASH的編程操作是自動(dòng)字節(jié)操作,,編程時(shí)要特別注意編程時(shí)間參數(shù)和使用的命令集。編程和擦除時(shí)鐘周期的定時(shí)參數(shù)如表所示,。3 FPGA實(shí)現(xiàn)Flash編程器的設(shè)計(jì)

Flash編程器的關(guān)鍵是要保證Flash地址和數(shù)據(jù)信號(hào)在時(shí)序上的嚴(yán)格要求,由SST39SF010的編程和擦除周期時(shí)序參數(shù)得知,,它的地址或數(shù)據(jù)信號(hào)的建立和保持時(shí)間的最小時(shí)鐘周期僅為30ns,。為此,我們采用了40MHz的晶振作為FPGA的驅(qū)動(dòng)時(shí)鐘,,它的最小時(shí)鐘周期為25ns,,完全可滿足最小的時(shí)間周期要求。

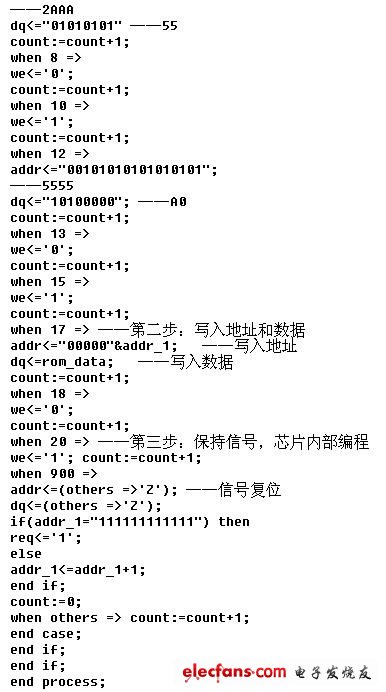

采用FPGA來(lái)實(shí)現(xiàn)Flash編程器,,主要是如何對(duì)Flash進(jìn)行寫(xiě)操作,,利用VHDL語(yǔ)言編寫(xiě)的寫(xiě)操作進(jìn)程表示如下:

實(shí)現(xiàn)一個(gè)控制功能,可以用有限狀態(tài)機(jī)實(shí)現(xiàn),,也可以用CPU實(shí)現(xiàn),,二者相比,前者性能遠(yuǎn)高于后者,。因?yàn)?,在Von Neumann結(jié)構(gòu)的CPU中,,需要許多操作(例如取數(shù)和執(zhí)行)和部件(例如數(shù)據(jù)通路和ALU寄存器)。而狀態(tài)機(jī)中,,狀態(tài)存儲(chǔ)在多個(gè)觸發(fā)器中,,表示行為的代碼存儲(chǔ)在門(mén)級(jí)網(wǎng)絡(luò)中。對(duì)于通常的一條選擇判斷語(yǔ)句,,如果用CPU實(shí)現(xiàn),,一般需要10~20條機(jī)器指令,其執(zhí)行時(shí)間與CPU的速度有關(guān),。如果由門(mén)和觸發(fā)器實(shí)現(xiàn),,則執(zhí)行時(shí)間為一個(gè)時(shí)鐘周期。因此用VHDL實(shí)現(xiàn)的狀態(tài)機(jī)的控制性能要優(yōu)于CPU實(shí)現(xiàn)的方案,。

如上述程序,,在編程器的寫(xiě)操作進(jìn)程中,我們使用Moore型狀態(tài)機(jī),,它最大的特點(diǎn)是輸出僅是狀態(tài)向量的函數(shù),,即Moore狀態(tài)機(jī)的輸出僅和當(dāng)前狀態(tài)(現(xiàn)態(tài))有關(guān)。在寄存器轉(zhuǎn)移級(jí)的有限狀態(tài)機(jī)中包括狀態(tài)進(jìn)程和組合進(jìn)程兩部分,。

狀態(tài)進(jìn)程:狀態(tài)進(jìn)程對(duì)狀態(tài)機(jī)的時(shí)鐘信號(hào)敏感,,當(dāng)時(shí)鐘發(fā)生有效跳變時(shí),狀態(tài)機(jī)的狀態(tài)發(fā)生變化,,由次態(tài)變?yōu)楝F(xiàn)態(tài),。本例中,將寫(xiě)操作分成900個(gè)狀態(tài),,狀態(tài)0初始化各輸出信號(hào),,狀態(tài)1~5執(zhí)行第一個(gè)控制命令,狀態(tài)7—10執(zhí)行如第二個(gè)控制命令,,狀態(tài)12~15執(zhí)行第三個(gè)控制命令,,狀態(tài)17~ 20給出要寫(xiě)入的地址和數(shù)據(jù),狀態(tài)21~900保持控制信號(hào),,是芯片內(nèi)部編程時(shí)間,。 組合進(jìn)程:組合進(jìn)程就根據(jù)當(dāng)前狀態(tài)(現(xiàn)態(tài))給輸出信號(hào)賦值,并決定下一狀態(tài)(次態(tài)),。在本例中,,狀態(tài)機(jī)根據(jù)不同的狀態(tài)對(duì)CE#、OE#,、 WE,、地址、數(shù)據(jù)等Flash控制信號(hào)進(jìn)行賦值,從而實(shí)現(xiàn)對(duì)Flash的控制功能,。

但是每執(zhí)行一次寫(xiě)操作,,只能寫(xiě)入一個(gè)地址單元里的8bit數(shù)據(jù),如果按照這個(gè)方法,,完成整個(gè)Flash芯片1Mbit數(shù)據(jù)的寫(xiě)入就需要重復(fù)執(zhí)行寫(xiě)操作 128K次,,這樣既麻煩又浪費(fèi)時(shí)間。我們選用的Xilinx公司SpartanⅡ系列FPGA,,提供片上雙端口同步讀/寫(xiě)RAM塊,,每塊RAM容量為4096bit。塊RAM的每個(gè)端口可獨(dú)立配置為讀/寫(xiě)端口,、讀端口或?qū)懚丝?,同時(shí)還能配置為任何想要的數(shù)據(jù)帶寬。因此塊RAM可使FPGA設(shè)計(jì)者的設(shè)計(jì)更加簡(jiǎn)單,,可以把塊RAM配置成ROM,、RAM、FIFO等多種元件,,具有使用方便,、性能優(yōu)越等特點(diǎn),是一種十分高效的內(nèi)部存儲(chǔ)器解決方案,。因此我們采用FPGA的塊RAM作為內(nèi)部數(shù)據(jù)緩沖器,,以提高 Flash寫(xiě)操作的速度和效率。

在本例中,,使用內(nèi)部塊RAM產(chǎn)生一個(gè)32Kbit 的ROM 元件,,程序當(dāng)中直接引用和映射該元件,將要寫(xiě)入Flash的數(shù)據(jù)先寫(xiě)入該ROM元件中,,然后在每次寫(xiě)操作中將ROM中的數(shù)據(jù)按地址順序逐一寫(xiě)入Flash中的一個(gè)連續(xù)32Kbit的扇區(qū)當(dāng)中,,這樣編程器的一次寫(xiě)操作就可以寫(xiě)入32Kbit數(shù)據(jù),因?yàn)?2K×32=1Mbit,,則依次改變Flash的高5位地址,,重復(fù)32次上述的寫(xiě)操作,這樣1Mbit的數(shù)據(jù)就寫(xiě)入了整片F(xiàn)lash中,,大大提高了編程器寫(xiě)操作的效率。至于ROM元件中的數(shù)據(jù),,則以ASCⅡ碼的形式存在以.

CoeGenerator是一個(gè)元件生成軟件,,它給用戶提供了一個(gè)通用化的設(shè)計(jì)界面,提供RAM,、ROM,、乘法器、各種標(biāo)準(zhǔn)接口等許多設(shè)計(jì)中常用的元件模型,,這樣設(shè)計(jì)者不必自己動(dòng)手編寫(xiě),,而采用CoeGenerator即可生成自己需要的各種元件,。這些元件都是經(jīng)過(guò)了最優(yōu)化設(shè)計(jì),占用資源最少,,性能最優(yōu),,還大大節(jié)省了設(shè)計(jì)時(shí)間,方便了設(shè)計(jì)者,。產(chǎn)生的ROM元件將存儲(chǔ)在設(shè)計(jì)工程之中,,需要在程序中加入引用語(yǔ)句,才可以使用,。 VHDL程序中使用CoreGenerator產(chǎn)生的元件需要加入兩段語(yǔ)句,,一是在實(shí)體部分對(duì)要引用的ROM元件進(jìn)行說(shuō)明,二是在結(jié)構(gòu)體中對(duì)ROM元件例化,,映射例化元件的輸入/輸出信號(hào),。 由于FPGA具有在線可再編程性能,因此當(dāng)系統(tǒng)中FLASH 直接由FPGA存取時(shí),,我們可以用FPGA實(shí)現(xiàn)對(duì)Flash的編程,,在編程操作之后,對(duì)FPGA 進(jìn)行再配置,,實(shí)現(xiàn)其它

系統(tǒng)功能,,達(dá)到一個(gè)FPGA器件實(shí)現(xiàn)多種應(yīng)用的目的。

4 結(jié)束語(yǔ)

使用VHDL語(yǔ)言,,由FPGA來(lái)實(shí)現(xiàn)Flash編程器的功能,,不僅節(jié)約了專用編程器的采購(gòu)開(kāi)支,更重要的是可以靈活,、快速地實(shí)現(xiàn)專用Flash編程器的功能,。隨著微電子技術(shù)的發(fā)展,可編程器件的容量已經(jīng)達(dá)到千萬(wàn)門(mén)級(jí),,越來(lái)越多的過(guò)去必須由專用芯片或器件才能完成的工作現(xiàn)在都可以通過(guò)設(shè)計(jì)軟件,,由FPGA來(lái)實(shí)現(xiàn)了。硬件的軟件化已經(jīng)成為電子行業(yè)中不可阻擋的趨勢(shì),。