1.引言

隨著電子產(chǎn)品功能的日益復(fù)雜和性能的提高,印刷電路板的密度和其相關(guān)器件的頻率都不斷攀升,保持并提高系統(tǒng)的速度與性能成為設(shè)計者面前的一個重要課題。信號頻率變高,邊沿變陡,印刷電路板的尺寸變小,布線密度加大等都使得串?dāng)_在高速PCB設(shè)計中的影響顯著增加。串?dāng)_問題是客觀存在,但超過一定的界限可能引起電路的誤觸發(fā),導(dǎo)致系統(tǒng)無法正常工作。設(shè)計者必須了解串?dāng)_產(chǎn)生的機(jī)理,并且在設(shè)計中應(yīng)用恰當(dāng)?shù)姆椒ǎ勾當(dāng)_產(chǎn)生的負(fù)面影響最小化。

2.高頻數(shù)字信號串?dāng)_的產(chǎn)生及變化趨勢

串?dāng)_是指當(dāng)信號在傳輸線上傳播時,相鄰信號之間由于電磁場的相互耦合而產(chǎn)生的不期望的噪聲電壓信號,即能量由一條線耦合到另一條線上。

如圖1所示,為便于分析,我們依照離散式等效模型來描述兩個相鄰傳輸線的串?dāng)_模型,傳輸線AB和CD的特性阻抗為Z0,且終端匹配電阻R=Z0。如果位于A 點的驅(qū)動源為干擾源,則A—B間的線網(wǎng)稱為干擾源網(wǎng)絡(luò)(Aggressor line),C—D之間的線網(wǎng)被稱為被干擾網(wǎng)絡(luò)(Victim line),被干擾網(wǎng)絡(luò)靠近干擾源網(wǎng)絡(luò)的驅(qū)動端的串?dāng)_稱為近端串?dāng)_(也稱后向串?dāng)_),而靠近干擾源網(wǎng)絡(luò)接收端方向的串?dāng)_稱為遠(yuǎn)端串?dāng)_(也稱前向串?dāng)_)。串?dāng)_主要源自兩相鄰導(dǎo)體之間所形成的互感Lm和互容Cm。

2.1感性耦合

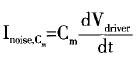

在圖1中,先只考慮互感Lm引起的感性耦合。線路A到B上傳輸?shù)男盘柕拇艌鲈诰€路C到D上感應(yīng)出電壓,磁耦合的作用類似一個變壓器,由于這是個分布式的傳輸線,所以互感也變成一連串的變壓器分布在兩個相鄰的并行傳輸線上。當(dāng)一個電壓階躍信號從A移動到B,每個分布在干擾線上的變壓器會依序感應(yīng)一個干擾尖脈沖出現(xiàn)在被干擾網(wǎng)絡(luò)上。互感在被干擾網(wǎng)絡(luò)上疊加的這個電壓噪聲,其大小跟干擾網(wǎng)絡(luò)上驅(qū)動電流的變化成正比。由互感產(chǎn)生的噪聲計算公式為

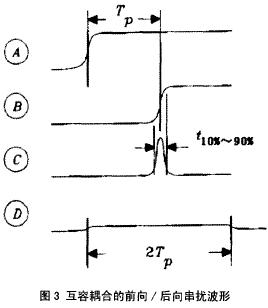

值得注意的是,耦合變壓器每一段的互感耦合的極性是不同的,這些感應(yīng)到被干擾網(wǎng)路的干擾能量依序前向和后向,但極性相反,沿著傳輸線CD分別往C和D點行進(jìn)。

如圖2所示,往C方向的前向干擾能量,是和入射電壓及每個互感分量Lm成正比,因為所有前向干擾能量幾乎同時抵達(dá)C點,所以前向干擾能量與兩傳輸線的互感總量成正比,傳輸線平行的長度越長,所產(chǎn)生的互感總量就越大,前向干擾能量也隨即增加;然而往D點的后向干擾能量與往C點的前向干擾能量不同的是,雖然兩者耦合的總區(qū)域是一樣的,但每個互感變壓器所感應(yīng)的干擾分量是依序到達(dá)D,后向干擾能量的有效時間長達(dá)2Tp(Tp為傳播延時),隨著線路平行長度的延長 (即互感增加),后向串?dāng)_的幅度大小是不會變化的,而持續(xù)時間會增加。

2.2容性耦合

互容是產(chǎn)生串?dāng)_的另一個機(jī)制。互容Cm會對被干擾網(wǎng)絡(luò)產(chǎn)生一個感應(yīng)電流,該電流正比于干擾網(wǎng)絡(luò)上電壓的變化速率,由互容Cm產(chǎn)生的噪聲計算公式為:

分布式耦合電容的耦合機(jī)制和分布式電感耦合相類似,區(qū)別在于耦合的極性。如圖3所示,互容耦合的前向和后向干擾能量的極性都是正的。

2.3互感和互容的合成效應(yīng)

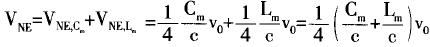

通常,容性串?dāng)_和感性串?dāng)_是同時發(fā)生的。由文獻(xiàn)[1],我們可以分別得到近端和遠(yuǎn)端的總串?dāng)_的計算公式,它們是分別由容性耦合和感性耦合疊加而成的。

近端串?dāng)_總噪聲為:

遠(yuǎn)端串?dāng)_總噪聲為:

其中,Z0,C,l,Cm,Lm,L,V0分別為傳輸線的特征阻抗、單位長度電容、單位長度電感,兩傳輸線之間耦合電容、耦合電感,兩傳輸線平行長度和電壓峰值。

其中,Z0,C,l,Cm,Lm,L,V0分別為傳輸線的特征阻抗、單位長度電容、單位長度電感,兩傳輸線之間耦合電容、耦合電感,兩傳輸線平行長度和電壓峰值。

由以上兩式,我們可以看出遠(yuǎn)端串?dāng)_總噪聲由于容性和感性耦合的極性關(guān)系而相互消減,即遠(yuǎn)端串?dāng)_是可以消除的。在PCB布線中,帶狀線(Stripline) 電路更能夠顯示感性和容性耦合之間很好的平衡,其前向耦合能量極小;而對于微帶線(Microstfip),與串?dāng)_相關(guān)的電場大部分穿過的是空氣,而不是其它的絕緣材料,因此容性串?dāng)_比感性串?dāng)_小,導(dǎo)致其前向耦合是一個小的負(fù)數(shù)。這也就是通常設(shè)計中,常忽略遠(yuǎn)端串?dāng)_的干擾,而較著重于近端串?dāng)_改善的原因。

在實際設(shè)計中,PCB的有關(guān)參數(shù)(如厚度,介電常數(shù)等)以及線長、線寬、線距、傳輸線與地平面的位置和電流流向都會影響c、l、Cm、Lm、L、的大小,而信號頻率和器件的上升/下降時間決定了 。

在這里我們不做這些參數(shù)對串?dāng)_影響的定量分析,有關(guān)這些參數(shù)的相互關(guān)系及對串?dāng)_影響的程度,詳見其它相關(guān)參考文獻(xiàn)。

2.4串?dāng)_的變化趨勢

互感與互容的大小影響著串?dāng)_的大小,從而等價地改變傳輸線特征阻抗與傳播速度。同樣,傳輸線的幾何形狀在很大程度上影響著互感與互容的變化,因此傳輸線本身的特征阻抗對這些參數(shù)也有影響。在同一介質(zhì)中,相對低阻抗的傳輸線與參考平面(地平面)間的耦合更加強(qiáng)烈,相對地與鄰近傳輸線的耦合就會弱一些,因而低阻抗傳輸線對串?dāng)_引起的阻抗變化更小一些。

3 串?dāng)_導(dǎo)致的幾種影響

在高速、高密度PCB設(shè)計中一般提供一個完整的接地平面,從而使每條信號線基本上只和它最近的信號線相互影響,來自其它較遠(yuǎn)信號線的交叉耦合是可以忽略的。盡管如此,在模擬系統(tǒng)中,大功率信號穿過低電平輸入信號或當(dāng)信號電壓較高的元件(如TTL)與信號電壓較低的元件(如ECL)接近時,都需要非常高的抗串?dāng)_能力。在PCB設(shè)計中,如果不正確處理,串?dāng)_對高速PCB的信號完整性主要有以下兩種典型的影響。

3.1串?dāng)_引起的誤觸發(fā)

信號串?dāng)_是高速設(shè)計所面臨的信號完整性問題中一個重要內(nèi)容,由串?dāng)_引起的數(shù)字電路功能錯誤是最常見的一種。

圖 4是一種典型的由串?dāng)_脈沖引起的相鄰網(wǎng)絡(luò)錯誤邏輯的傳輸。干擾源網(wǎng)絡(luò)上傳輸?shù)男盘柾ㄟ^耦合電容,在被干擾網(wǎng)絡(luò)和接收端引起一個噪聲脈沖,結(jié)果導(dǎo)致一個不希望的脈沖發(fā)送到接受端。如果這個脈沖強(qiáng)度超過了接收端的觸發(fā)值,就會產(chǎn)生無法控制的觸發(fā)脈沖,引起下一級網(wǎng)絡(luò)的邏輯功能混亂。

3.2串?dāng)_引起的時序延時

在數(shù)字設(shè)計中,時序問題是一個重要考慮的問題。圖5顯示了由串?dāng)_噪聲引起的時序問題。圖下半部分是干擾源網(wǎng)絡(luò)產(chǎn)生的兩種噪聲脈沖(Helpful圖5串?dāng)_噪聲導(dǎo)致的延時glitch和Unhelpful glitch),當(dāng)噪聲脈沖(helpful glitch)疊加到被干擾網(wǎng)絡(luò),就引起被干擾網(wǎng)絡(luò)信號傳輸延時減少;同樣,當(dāng)噪聲脈沖(Unhelpful glitch)疊加到被干擾網(wǎng)絡(luò)時,就增加了被干擾網(wǎng)絡(luò)正常傳輸信號的延時。盡管這種減少網(wǎng)絡(luò)傳輸延時的串?dāng)_噪聲對改善PCB時序是有幫助的,但在實際 PCB設(shè)計中,由于干擾源網(wǎng)絡(luò)的不確定性,這種延時是無法控制的,因而對這種串?dāng)_引起的延時必須要加以抑制。

4.串?dāng)_最小化

串?dāng)_在高速高密度的PCB設(shè)計中普遍存在,串?dāng)_對系統(tǒng)的影響一般都是負(fù)面的。為減少串?dāng)_,最基本的就是讓干擾源網(wǎng)絡(luò)與被干擾網(wǎng)絡(luò)之間的耦合越小越好。在高密度復(fù)雜PCB設(shè)計中完全避免串?dāng)_是不可能的,但在系統(tǒng)設(shè)計中設(shè)計者應(yīng)該在考慮不影響系統(tǒng)其它性能的情況下,選擇適當(dāng)?shù)姆椒▉砹η蟠當(dāng)_的最小化。結(jié)合上面的分析,解決串?dāng)_問題主要從以下幾個方面考慮:

在布線條件允許的條件下,盡可能拉大傳輸線間的距離;或者盡可能地減少相鄰傳輸線間的平行長度(累積平行長度),最好是在不同層間走線。

相鄰兩層的信號層(無平面層隔離)走線方向應(yīng)該垂直,盡量避免平行走線以減少層間的串?dāng)_。

在確保信號時序的情況下,盡可能選擇轉(zhuǎn)換速度低的器件,使電場與磁場的變化速率變慢,從而降低串?dāng)_。

在設(shè)計層疊時,在滿足特征阻抗的條件下,應(yīng)使布線層與參考平面(電源或地平面)間的介質(zhì)層盡可能薄,因而加大了傳輸線與參考平面間的耦合度,減少相鄰傳輸線的耦合。

由于表層只有一個參考平面,表層布線的電場耦合比中間層的要強(qiáng),因而對串?dāng)_較敏感的信號線盡量布在內(nèi)層。

通過端接,使傳輸線的遠(yuǎn)端和近端終端阻抗與傳輸線匹配,可大大減小串?dāng)_的幅度。

5.結(jié)束語

數(shù)字系統(tǒng)設(shè)計已經(jīng)進(jìn)入了一個新的階段。許多過去處于次要地位的高速設(shè)計問題,現(xiàn)在已經(jīng)對于系統(tǒng)性能具有關(guān)鍵的影響。包括串?dāng)_在內(nèi)的信號完整性問題帶來了設(shè)計觀念、設(shè)計流程及設(shè)計方法的變革。面對新的挑戰(zhàn),對于串?dāng)_噪聲而言,最關(guān)鍵的就是找出那些對系統(tǒng)正常運行真正有影響的網(wǎng)絡(luò),而不是盲目的對所有網(wǎng)絡(luò)進(jìn)行串?dāng)_噪聲的抑制,這也是和有限的布線資源相矛盾的。本文所討論的串?dāng)_問題對于高速高密度電路設(shè)計中解決串?dāng)_問題具有十分重要的意義。