1 引言

隨著同防工業(yè)對(duì)精確制導(dǎo)武器要求的不斷提高,武器系統(tǒng)總體設(shè)計(jì)方案的日趨復(fù)雜,以及電子元器件水平的飛速發(fā)展。導(dǎo)引頭信號(hào)處理器的功能越來(lái)越復(fù)雜,硬件規(guī)模越來(lái)越大.處理速度也越來(lái)越高.而且產(chǎn)品的更新速度加快,生命周期縮短。實(shí)現(xiàn)功能強(qiáng)、性能指標(biāo)高、抗干擾能力強(qiáng)、工作穩(wěn)定可靠、體積小、功耗低、結(jié)構(gòu)緊湊合理符合彈載要求的導(dǎo)引頭信號(hào)處理器已經(jīng)勢(shì)在必行。過(guò)去單一采用DSP處理器搭建信號(hào)處理器已經(jīng)不能滿足要求.FPGA+DSP的導(dǎo)引頭信號(hào)處理結(jié)構(gòu)成為當(dāng)前以及未來(lái)一段時(shí)間的主流。

FPGA和DSP處理器具有截然不同的架構(gòu),在一種器件上非常有效的算法.在另一種器件上可能效率會(huì)非常低。如果目標(biāo)要求大量的并行處理或者最大的多通道流量,那么單純基于DSP的硬件系統(tǒng)就可能需要更大的面積,成本或功耗。一個(gè)FPGA僅在一個(gè)器件上就能高提供多達(dá)550個(gè)并行乘法和累加運(yùn)算,從而以較少的器件和較低的功耗提供同樣的性能。但對(duì)于定期系數(shù)更新,決策控制任務(wù)或者高速串行處理任務(wù),F(xiàn)PGA的優(yōu)化程度遠(yuǎn)不如DSP。

FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點(diǎn),兼顧了速度和靈活性。本文以導(dǎo)引頭信號(hào)處理系統(tǒng)為例說(shuō)明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)。

2 系統(tǒng)組成

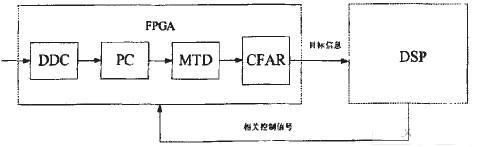

本系統(tǒng)南一片F(xiàn)PGA和一片DSP來(lái)組成,F(xiàn)PGA在實(shí)時(shí)并行計(jì)算實(shí)現(xiàn)標(biāo)準(zhǔn)數(shù)字信號(hào)處理算法的能力遠(yuǎn)強(qiáng)于DSP,因此數(shù)字接收系統(tǒng)信號(hào)處理要用到的FIR濾波、FFT、IFFT等算法,在FPGA中實(shí)現(xiàn)要遠(yuǎn)快于用DSP,且FPGA廠商提供了非常豐富易用的能實(shí)現(xiàn)數(shù)字信號(hào)處理的參數(shù)Core.可以大大簡(jiǎn)化開(kāi)發(fā)過(guò)程。而且,F(xiàn)PGA支持丁程師設(shè)計(jì)高度并行的架構(gòu)以及有大量乘法器和存儲(chǔ)器資源,因此將數(shù)字下變頻(DDC),脈壓(PC),動(dòng)目標(biāo)檢測(cè)(MTD),恒虛警處理(CFAR)等也在FPGA中實(shí)現(xiàn),可有效提高實(shí)時(shí)性,集成度和穩(wěn)定性。而DSP用來(lái)進(jìn)行其他復(fù)雜信號(hào)處理,比如自動(dòng)目標(biāo)識(shí)別、抗干擾等。

FPGA和DSP的通信通過(guò)32位的數(shù)據(jù)總線聯(lián)通。FPGA通過(guò)此數(shù)據(jù)總線把柃測(cè)得到的目標(biāo)信息傳遞給DSP做后續(xù)處理,DSP則通過(guò)數(shù)據(jù)總線傳遞控制信息。

圖1 FPGA+DSP的系統(tǒng)組成框圖

3 FPGA設(shè)計(jì)中的關(guān)鍵技術(shù)

3.1 跨時(shí)鐘域的設(shè)計(jì)

3.1.1基礎(chǔ)

只有最初級(jí)的邏輯電路才使用單一的時(shí)鐘。大多數(shù)與數(shù)據(jù)傳輸相關(guān)的應(yīng)用都有與牛俱來(lái)的挑戰(zhàn),即跨越多個(gè)時(shí)鐘域的數(shù)據(jù)移動(dòng),例如磁盤控制器、CDROM/DVD控制器、調(diào)制解調(diào)器、網(wǎng)卡以及網(wǎng)絡(luò)處理器等。當(dāng)信號(hào)從一個(gè)時(shí)鐘域傳送到另一個(gè)時(shí)鐘域時(shí),出現(xiàn)在新時(shí)鐘域的信號(hào)是異步信號(hào)。

在現(xiàn)代IC、ASIC以及FPGA設(shè)計(jì)中,許多軟件程序可以幫助工程師建立幾百萬(wàn)門的電路。但這些程序都無(wú)法解決信號(hào)同步問(wèn)題。設(shè)計(jì)者需要了解可靠的設(shè)計(jì)技巧,以減少電路在跨時(shí)鐘域通信時(shí)的故障風(fēng)險(xiǎn)。

從事多時(shí)鐘設(shè)計(jì)的第一步是要理解信號(hào)穩(wěn)定性問(wèn)題。當(dāng)一個(gè)信號(hào)跨越某個(gè)時(shí)鐘域時(shí).對(duì)新時(shí)鐘域的電路來(lái)說(shuō)它就是一個(gè)異步信號(hào)。接收該信號(hào)的電路需要對(duì)其進(jìn)行同步。同步可以防止第一級(jí)存儲(chǔ)單元(觸發(fā)器)的亞穩(wěn)態(tài)在新的時(shí)鐘域里傳播蔓延。

亞穩(wěn)態(tài)是指觸發(fā)器無(wú)法在某個(gè)規(guī)定時(shí)間段內(nèi)達(dá)到一個(gè)可確認(rèn)的狀態(tài)。當(dāng)一個(gè)觸發(fā)器進(jìn)入亞穩(wěn)態(tài)時(shí),既尤法預(yù)測(cè)該單元的輸}}{電平,也無(wú)法預(yù)測(cè)何時(shí)輸出才能穩(wěn)定在某個(gè)正確的電平上。在這個(gè)穩(wěn)定期問(wèn),觸發(fā)器輸出一些中間級(jí)電平,或者可能處于振蕩狀態(tài),并且這種尤用的輸出電平可以滑信號(hào)通道上的各個(gè)觸發(fā)器級(jí)聯(lián)式傳播下去。

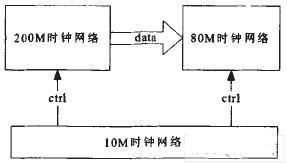

由于數(shù)據(jù)率比較低,而FPGA的工作頻率可以很高,所以在雷達(dá)信號(hào)處理機(jī)的FPGA設(shè)計(jì)中,勢(shì)必要引入跨時(shí)鐘域的設(shè)計(jì),例如在某項(xiàng)口中,控制網(wǎng)絡(luò)為10M.脈沖壓縮工作時(shí)鐘為200M,MTD、CFAR為80M,是個(gè)典型的跨時(shí)鐘域設(shè)計(jì)。

圖2時(shí)鐘域示意圖

3.1.2跨R寸鐘域的處理

現(xiàn)代IC與FPGA設(shè)計(jì)巾使用的綜合工具可以保證設(shè)計(jì)能滿足每個(gè)數(shù)字電路觸發(fā)器對(duì)建立與保持時(shí)間的要求。然而,異步信號(hào)卻給軟件提出了難題。對(duì)新的時(shí)鐘域米說(shuō).從其它時(shí)鐘域傳柬的信號(hào)是異步的。大多數(shù)綜合丁具在判定算步信號(hào)是否滿足觸發(fā)器時(shí)序要求時(shí)遇到了麻煩。因?yàn)樗鼈儾荒艽_定觸發(fā)器處于非穩(wěn)態(tài)的時(shí)間,所以它們也就不能確定從一個(gè)觸發(fā)器通過(guò)組合邏輯到達(dá)下一個(gè)觸發(fā)器的總延遲時(shí)間。所以,最好的辦法是使用一些電路來(lái)減輕異步信號(hào)的影響。

同步措施歸納起來(lái)主要有兩方面,

1)對(duì)于跨越時(shí)鐘域控制信號(hào),用同步器來(lái)實(shí)現(xiàn)同步;

為了使同步。工作能正常進(jìn)行,從某個(gè)時(shí)鐘域傳來(lái)的信號(hào)應(yīng)先通過(guò)原時(shí)鐘域上的一個(gè)觸發(fā)器,然后不經(jīng)過(guò)兩個(gè)時(shí)鐘域間的任何組合邏輯,直接進(jìn)入同步器的第一個(gè)觸發(fā)器中(圖3)。這一要求非常重要,因?yàn)橥狡鞯牡谝患?jí)觸發(fā)器對(duì)組合邏輯所產(chǎn)生的毛刺非常敏感。如果一個(gè)足夠長(zhǎng)的信號(hào)毛刺正好滿足建立一保持時(shí)問(wèn)的要求,則同步器的第一級(jí)觸發(fā)器會(huì)將其放行,給新時(shí)鐘域的后續(xù)邏輯送出一個(gè)虛假的信號(hào)。

圖3同步器示意

一個(gè)經(jīng)同步后的信號(hào)在兩個(gè)時(shí)鐘沿以后就成為新時(shí)鐘域中的有效信號(hào)。信號(hào)的延遲是新時(shí)鐘域中的一到兩個(gè)時(shí)鐘周期。一種粗略的估算方法是同步器電路在新時(shí)鐘域中造成兩個(gè)時(shí)鐘周期的延遲,設(shè)計(jì)者需要考慮同步延遲將對(duì)跨時(shí)鐘域的信號(hào)時(shí)序造成的影響。

2)對(duì)于跨越時(shí)鐘域的數(shù)據(jù)總線,要通過(guò)FIFO或RAM達(dá)到同步的目的。

數(shù)據(jù)在時(shí)鐘域之間的傳遞是多個(gè)隨機(jī)變化的控制信號(hào)在時(shí)鐘域之間傳遞的一種實(shí)例。這種情況下,用同步器米處理同步問(wèn)題往往不能收到滿意的效果,因?yàn)槎辔粩?shù)據(jù)的變化將會(huì)使同步器的采樣錯(cuò)誤率大大增加。常用的數(shù)據(jù)同步方法有兩種:一種是用握手信號(hào);另一種是用FIFO,一個(gè)時(shí)鐘存數(shù)據(jù)。另一個(gè)時(shí)鐘取數(shù)據(jù)。

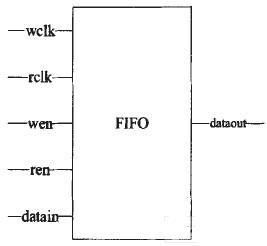

時(shí)鐘域之間的數(shù)據(jù)傳輸用得最多的是FIFO,采用Xilinx自帶的FIFO核來(lái)實(shí)現(xiàn)比較簡(jiǎn)單方便,圖4足Xilinx提供的FIFO核的一個(gè)簡(jiǎn)單的示意圖.wclk為寫(xiě)時(shí)鐘,rclk為讀時(shí)鐘,F(xiàn)IFO深度通過(guò)讀寫(xiě)使能wen和ren控制。

圖4 FIFO核示意圖

3.2、FPGA與DSP數(shù)據(jù)交互

實(shí)際應(yīng)用過(guò)程中,DSP和FPGA程序設(shè)計(jì)往往是由不同的設(shè)計(jì)人員分工完成,在最后系統(tǒng)聯(lián)調(diào)時(shí),這兩者之間的數(shù)據(jù)傳輸經(jīng)常占用大量的調(diào)試時(shí)間,成為約束工程進(jìn)度的關(guān)鍵兇素。因此,DSP與FPGA間接口和傳輸方式的選擇與設(shè)計(jì),是系統(tǒng)設(shè)計(jì)中必須要考惑的問(wèn)題。

導(dǎo)引頭信號(hào)處理的一個(gè)特點(diǎn)是,F(xiàn)PGA要傳輸給DSP的數(shù)據(jù)比較多,需要傳遞幅度信息,和差支路數(shù)據(jù)等十幾組數(shù)據(jù).每組數(shù)據(jù)長(zhǎng)度在512~2K,而且讀取速度要求也比較高,一般要求百兆以上的讀取頻率。經(jīng)過(guò)工程實(shí)踐表明,采用通過(guò)EDMA通道同步讀取FIFO的方式實(shí)現(xiàn)通信是非常有效的方法。但是接口處的FIFO比較多,而且讀取速度有比較高,這勢(shì)必導(dǎo)致FPGA內(nèi)部對(duì)接口處資源的競(jìng)爭(zhēng),甚至?xí)?dǎo)致時(shí)序的不滿足。在實(shí)際工程調(diào)試中表現(xiàn)在DSP接收到的數(shù)據(jù)亂序,周期循環(huán)甚至亂碼。

要解決好FPGA和DSP的數(shù)據(jù)交互問(wèn)題,要注意以下兩個(gè)方面。

3.2.1 三態(tài)門的設(shè)計(jì)

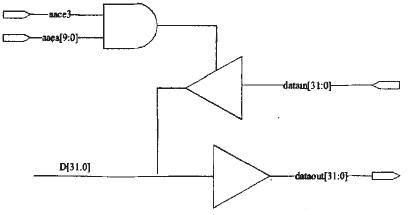

在本設(shè)計(jì)中,DSP和FPGA的互連采用了總線連接的方式,數(shù)據(jù)交互是通過(guò)一個(gè)32位的雙向數(shù)據(jù)總線來(lái)完成的,而要實(shí)現(xiàn)雙向總線,就需要使用FPGA構(gòu)造三態(tài)總線了,使用三態(tài)緩沖器實(shí)現(xiàn)高、低電平和高阻三個(gè)狀態(tài)。

圖5雙向數(shù)據(jù)總線的三態(tài)門設(shè)計(jì)

本設(shè)計(jì)當(dāng)中,F(xiàn)PGA給DSP發(fā)中斷信號(hào),DSP在中斷信號(hào)到來(lái)時(shí),根據(jù)系統(tǒng)要求,將不同的控制字寫(xiě)入數(shù)據(jù)總線,然后通過(guò)數(shù)據(jù)總線從FPGA中不同的FIFO中讀取數(shù)據(jù),這一切都通過(guò)DSP在地址線上給出不同的地址來(lái)完成。為了合理分配總線的使用,設(shè)計(jì)當(dāng)中使用這樣的策略:利用片選信號(hào)aace3,地址aaea[9:0]作為三態(tài)緩沖器的控制信號(hào),由于DSP對(duì)FPGA的讀寫(xiě)地址都不同,當(dāng)片選信號(hào)aace3有效時(shí),F(xiàn)PGA根據(jù)地址來(lái)確定湊寫(xiě)方式以及讀寫(xiě)那些信息,否則置為高阻態(tài),這樣就避免了可能產(chǎn)生的的總線阻塞現(xiàn)象,使DSP和FPGA之間的數(shù)據(jù)交互能夠順利進(jìn)行,示意圖如圖5所示。

3.2.2 加有效的時(shí)序約束

由于接口FIFO比較多,為了合理分配FPGA內(nèi)部接口處的資源,滿足系統(tǒng)的時(shí)序要求,需要加必要的時(shí)序約束。因?yàn)楸驹O(shè)計(jì)采用Xilinx公司芯片,所以需要加偏移約束2。

偏置約束可以優(yōu)化以下時(shí)延路徑:從輸入管腳到同步元件偏置輸入;從同步元件到輸出管腳偏置輸出。為了確保芯片數(shù)據(jù)采樣可靠和下級(jí)芯片之間正確交換數(shù)據(jù),需要約束外部時(shí)鐘和數(shù)據(jù)輸入輸出引腳問(wèn)的時(shí)序關(guān)系。偏置約束的內(nèi)容告訴綜合器,布線器輸入數(shù)據(jù)到達(dá)的時(shí)刻或者輸出數(shù)據(jù)穩(wěn)定的時(shí)刻,從而保證與下一級(jí)電路的時(shí)序關(guān)系。更多關(guān)于約束的內(nèi)容請(qǐng)參閱文獻(xiàn)。

4 結(jié)束語(yǔ)

FPGA+DSP是同前導(dǎo)引頭信號(hào)處理器中運(yùn)用的最廣泛的系統(tǒng)組成形式,對(duì)速度以及靈活性的要求都能夠很好的滿足,文中所涉及到的跨時(shí)鐘域設(shè)計(jì)以及數(shù)據(jù)接口方面的問(wèn)題是這樣的系統(tǒng)中FPGA設(shè)計(jì)存在的關(guān)鍵技術(shù),文中提出了詳實(shí)的解決方法,而且工程應(yīng)用已經(jīng)證明了其有效性。

本文作者創(chuàng)新點(diǎn):依據(jù)工程實(shí)踐經(jīng)驗(yàn),總結(jié)了在FPGA+DSP結(jié)構(gòu)的雷達(dá)導(dǎo)引頭信號(hào)處理中FPGA的關(guān)鍵問(wèn)題,并提出了詳細(xì)的解決方案,并得到了工程驗(yàn)證。