摘 要: 設(shè)計(jì)了基于FPGA的片上網(wǎng)絡(luò)系統(tǒng)硬件平臺(tái)。系統(tǒng)由大容量的FPGA、存儲(chǔ)器、高速A/D與D/A、通信接口和一個(gè)擴(kuò)展的ARM9系統(tǒng)組成。完成了集高速數(shù)字信號(hào)處理、視頻編解碼和網(wǎng)絡(luò)傳輸功能與一體的多核系統(tǒng)設(shè)計(jì)。針對(duì)典型的3×3 2D Mesh結(jié)構(gòu)的NoC系統(tǒng)應(yīng)用進(jìn)行了探討,闡述了NoC系統(tǒng)設(shè)計(jì)過(guò)程中的關(guān)鍵技術(shù),并使用SigXplorer軟件對(duì)系統(tǒng)的信號(hào)完整性解決方案進(jìn)行了PCB的反射與串?dāng)_仿真。

關(guān)鍵詞: 片上網(wǎng)絡(luò);信號(hào)完整性;驗(yàn)證平臺(tái);片上端接

中圖分類號(hào):TN47 文獻(xiàn)標(biāo)識(shí)碼:B 文章編號(hào):0258-7998(2012)02-0117-03

IC制造技術(shù)的發(fā)展推動(dòng)著芯片向更高集成度方向前進(jìn),從而能夠?qū)⒄麄€(gè)系統(tǒng)設(shè)計(jì)到單個(gè)芯片中構(gòu)成片上系統(tǒng)SoC(System on Chip)。SoC采用全局同步型共享總線通信結(jié)構(gòu)。這類系統(tǒng)由于掛在總線上的設(shè)備在通信時(shí)對(duì)總線的獨(dú)占性以及單一系統(tǒng)總線對(duì)同步時(shí)鐘的要求,使得在片上IP核越來(lái)越多的芯片中,不可避免地存在通信效率低下、全局同步時(shí)鐘開銷大等問(wèn)題。

片上網(wǎng)絡(luò)NoC(Network on Chip)的提出有效地解決了上述問(wèn)題。該系統(tǒng)借鑒了計(jì)算機(jī)網(wǎng)絡(luò)中分組交換的通信方法,可以根據(jù)應(yīng)用靈活地采用多種網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)互連片上IP核[1]。各IP核間有多條鏈路可以進(jìn)行并行通信,由FIFO跨接處于異步時(shí)鐘域中的IP核,實(shí)現(xiàn)全局異部局部同步時(shí)鐘系統(tǒng)。具有可擴(kuò)展性好、低互連功耗和低延遲等特點(diǎn)。

然而目前NoC還處于研究階段,國(guó)內(nèi)許多科研機(jī)構(gòu)和院校圍繞著網(wǎng)絡(luò)拓?fù)浣Y(jié)構(gòu)、映射算法、路由算法、測(cè)試方法、路由節(jié)點(diǎn)的設(shè)計(jì)等展開研究[2]。各種基礎(chǔ)理論的驗(yàn)證通常依賴于軟件建模和硬件仿真。但針對(duì)NoC具體的應(yīng)用系統(tǒng)少有報(bào)道。本文闡述了一個(gè)小型NoC系統(tǒng)的硬件實(shí)現(xiàn),對(duì)系統(tǒng)的硬件實(shí)現(xiàn)方案、通信接口及信號(hào)完整性等問(wèn)題進(jìn)行了細(xì)致地研究。通過(guò)對(duì)完整系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn),探索了NoC系統(tǒng)應(yīng)用過(guò)程中的關(guān)鍵技術(shù)與難點(diǎn),同時(shí)驗(yàn)證了NoC相關(guān)理論算法與結(jié)構(gòu)、路由節(jié)點(diǎn)的設(shè)計(jì)和FPGA的多核技術(shù)等。

1 硬件平臺(tái)的設(shè)計(jì)

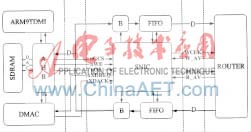

NoC應(yīng)用的最終目標(biāo)是將大型的多核系統(tǒng)設(shè)計(jì)到單芯片中,使得片內(nèi)可以容納大量處理器核、專用IP核、存儲(chǔ)器、數(shù)據(jù)通信單元等。然而這類龐大的系統(tǒng)在流片之前都需要合適的硬件平臺(tái)來(lái)進(jìn)行仿真、驗(yàn)證工作。另外某些場(chǎng)合的NoC系統(tǒng)更可能會(huì)直接選擇使用FPGA作為其最終的硬件實(shí)現(xiàn)方案。因此基于FPGA的NoC應(yīng)用系統(tǒng)設(shè)計(jì)具有實(shí)用性。考慮到FPGA的資源限制與NoC系統(tǒng)特點(diǎn),針對(duì)3×3 的2D Mesh結(jié)構(gòu)設(shè)計(jì)了基于FPGA的NoC應(yīng)用系統(tǒng)框架,如圖1所示。

圖1 NoC平臺(tái)的FPGA系統(tǒng)結(jié)構(gòu)圖

圖中NoC系統(tǒng)包含9個(gè)資源節(jié)點(diǎn),分為3行3列排列,每個(gè)資源節(jié)點(diǎn)有一個(gè)相鄰的路由節(jié)點(diǎn)R與其相連。9個(gè)路由節(jié)點(diǎn)按規(guī)則的二維網(wǎng)狀排列,由并行互連線連接構(gòu)成通信網(wǎng)絡(luò)。資源節(jié)點(diǎn)包括資源網(wǎng)絡(luò)接口SNI(Source Network Interface)、片內(nèi)存儲(chǔ)器M和IP核等。其中IP核可以是處理器核NIOS、專用IP核、DSP核,也可以是用戶設(shè)計(jì)的專用電路,而處理器核運(yùn)行所需的存儲(chǔ)任務(wù)在驗(yàn)證過(guò)程中由片外存儲(chǔ)器SDRAM和Flash實(shí)現(xiàn);通信網(wǎng)絡(luò)包括路由節(jié)點(diǎn)R和并行互連線,路由節(jié)點(diǎn)實(shí)現(xiàn)與本節(jié)點(diǎn)相連的資源節(jié)點(diǎn)的數(shù)據(jù)收發(fā)和相鄰路由節(jié)點(diǎn)的數(shù)據(jù)轉(zhuǎn)發(fā)功能。互連線構(gòu)成路由節(jié)點(diǎn)間信息傳輸?shù)妮d體,F(xiàn)PGA內(nèi)部大量的可編程互連線可以保障路由節(jié)點(diǎn)間足夠的通信帶寬。

1.1 NoC系統(tǒng)設(shè)計(jì)

NoC系統(tǒng)中資源節(jié)點(diǎn)使用的IP核、路由節(jié)點(diǎn)所需的FIFO緩沖器以及大量的互連線, 對(duì)平臺(tái)的核心器件FPGA提出了嚴(yán)峻的挑戰(zhàn)。以目前最先進(jìn)的FPGA來(lái)構(gòu)建大型的NoC系統(tǒng)仍顯不足,解決的方法通常由多片F(xiàn)PGA組合實(shí)現(xiàn)系統(tǒng)功能。考慮到本平臺(tái)主要由一個(gè)小型應(yīng)用系統(tǒng)的實(shí)現(xiàn),以及算法和路由的驗(yàn)證等組成,采用了單片大容量器件構(gòu)成獨(dú)立的系統(tǒng)平臺(tái),并設(shè)計(jì)了擴(kuò)展接口,可進(jìn)行多片組合實(shí)現(xiàn)更大的應(yīng)用系統(tǒng)。

目前,大容量可編程器件的供應(yīng)商主要有Xilinx公司、Altera公司和Actel公司。各大供應(yīng)商都提供了大容量與高速度的產(chǎn)品、完善的開發(fā)工具支持和常用IP核。綜合應(yīng)用的速度、軟核的開放性、器件的定購(gòu)周期與性價(jià)比,最終選定了Altera公司Cyclone IV 系列的EP4CE115F29芯片。該器件具有115 KLE,432 個(gè)M9K存儲(chǔ)塊,4個(gè)鎖相環(huán),20個(gè)全局同步時(shí)鐘網(wǎng)絡(luò),780腳的BGA封裝內(nèi)提供528個(gè)用戶I/O端口[3]。

處理器核是多核系統(tǒng)中應(yīng)用功能實(shí)現(xiàn)的常用部件。作為一款32位RISC處理器,Altera提供的軟核NIOS II在僅占用3 KLE的情況下提供超過(guò)200 DMIPS的性能,并提供了豐富的外設(shè)接口IP和高性能的AVLEN總線。開發(fā)工具SoPC Builder軟件支持單芯片內(nèi)多個(gè)獨(dú)立NIOS核的定制,同時(shí)NIOS II IDE軟件提供了多核的程序開發(fā)與調(diào)試環(huán)境。因此NIOS II可以作為NoC應(yīng)用系統(tǒng)中的軟核處理器。

路由節(jié)點(diǎn)負(fù)責(zé)NoC的通信工作,其通信帶寬與可靠性直接影響著系統(tǒng)的性能。許多研究人員深入研究了路由節(jié)點(diǎn)的設(shè)計(jì),并針對(duì)多種應(yīng)用設(shè)計(jì)進(jìn)行了優(yōu)化[4]。這類優(yōu)化大多圍繞著提高通信吞吐量、減少通信延遲,解決擁塞等問(wèn)題。路由的改進(jìn)給節(jié)點(diǎn)的RTL綜合提出了新的要求。例如一個(gè)緩沖式快速蟲孔交換路由節(jié)點(diǎn),片內(nèi)設(shè)計(jì)有10個(gè)以上獨(dú)立的32×16 FIFO,然而許多的小FIFO在綜合時(shí)都會(huì)各自占用一個(gè)包含32×256 的M9K單元。造成內(nèi)部存儲(chǔ)單元的使用效率低下、資源緊缺的問(wèn)題。另外由于片上網(wǎng)絡(luò)全局異步時(shí)鐘的特點(diǎn),現(xiàn)代FPGA越來(lái)越豐富的全局時(shí)鐘樹網(wǎng)絡(luò)顯得多余而浪費(fèi)。器件供應(yīng)商們?nèi)绻茉贔PGA的設(shè)計(jì)過(guò)程中引入對(duì)這些問(wèn)題的解決方案,必然會(huì)極大地推動(dòng)未來(lái)NoC應(yīng)用系統(tǒng)的FPGA實(shí)現(xiàn)。

1.2 基于ARM的資源網(wǎng)絡(luò)節(jié)點(diǎn)設(shè)計(jì)

ARM(Advanced RISC Machines)系列處理器因其高性能、低功耗、開放性好等優(yōu)點(diǎn),在許多領(lǐng)域廣泛應(yīng)用。長(zhǎng)期的應(yīng)用開發(fā)形成了許多相關(guān)的軟硬件資源。例如三星公司的S3C24XX系列處理器,不僅提供了豐富的外設(shè)接口,移植了成熟的ARM-Linux,更可以提供完整的TCP/IP協(xié)議支持和相當(dāng)豐富的外設(shè)驅(qū)動(dòng),加速了應(yīng)用的開發(fā)速度。NoC系統(tǒng)如能將片外的ARM處理器作為片上多核系統(tǒng)中的片外資源節(jié)點(diǎn),充分利用現(xiàn)有軟硬件資源,將給NoC系統(tǒng)帶來(lái)巨大的應(yīng)用空間。片外硬核與NoC系統(tǒng)的信息交換,即ARM同路由節(jié)點(diǎn)的通信由專用資源網(wǎng)絡(luò)接口SNI完成。針對(duì)ARM 處理器AHB總線時(shí)序,設(shè)計(jì)了基于DMA通信的SNI單元,如圖2所示。圖中ARM的數(shù)據(jù)總線為雙向數(shù)據(jù)總線,需要通過(guò)SNIC(Source NetworkInterface Controller)的控制實(shí)現(xiàn)分時(shí)復(fù)用。數(shù)據(jù)傳輸由SNIC發(fā)起,經(jīng)過(guò)nXDREQ向DMAC發(fā)送請(qǐng)求信號(hào),DMAC在獲得總路控制權(quán)后發(fā)出nXDACK信號(hào)[5]。隨后AHB總線將產(chǎn)生源和目的地址的讀寫信號(hào)進(jìn)行數(shù)據(jù)傳送,最終完成一次DMA傳輸。

圖2 ARM通信接口結(jié)構(gòu)圖

1.3 外圍電路及電源設(shè)計(jì)

系統(tǒng)為實(shí)現(xiàn)各類功能驗(yàn)證提供了大量的外圍電路,包括多套NIOS軟核運(yùn)行所需的存儲(chǔ)器、雙通道高速模擬信號(hào)輸入與輸出單元、攝像頭模組接口、VGA視頻輸出單元、10 M/100 M以太網(wǎng)接口單元和音頻接口單元。

電壓要求的多樣化需要多組的電源設(shè)計(jì),其中FPGA由1.2 V核心電壓、3.3 V與2.5 V I/O Buffer電壓、2.5 V模擬PLL電壓以及1.2 V數(shù)字PLL電壓組成。模擬PLL電壓需選用線性整流降壓得到,以獲得低紋波輸出的穩(wěn)定電壓源;其他數(shù)字部分電源適合采用開關(guān)型整流器電路供應(yīng)。例如TI的TPS54550器件,具有輸出電流大、效率高、外圍器件少等優(yōu)點(diǎn)。值得一提的是,CYCLONE IV 內(nèi)部具有電壓檢測(cè)與電源管理功能,沒有上電順序要求,簡(jiǎn)化了電源的設(shè)計(jì)。

2 信號(hào)完整性分析

大量高速器件的采用、FPGA的高密度封裝、敏感的A/D和D/A轉(zhuǎn)換芯片和許多開關(guān)整流器的噪聲,這些都決定著需要對(duì)信號(hào)完整性分析予以足夠的重視。設(shè)計(jì)過(guò)程中對(duì)疊層、電源隔離、地線處理做了細(xì)致的工作。采用Cyclone片內(nèi)端接OCT(On-Chip Termination)的源端端接方案,并通過(guò)精心的布局布線,有效地克服了各種信號(hào)干擾。最后使用SigXplorer 軟件提取PCB模型對(duì)信號(hào)的反射和串?dāng)_進(jìn)行仿真,驗(yàn)證了系統(tǒng)的信號(hào)完整性設(shè)計(jì)。

2.1 疊層設(shè)計(jì)

疊層設(shè)計(jì)涉及電源與信號(hào)層的規(guī)劃、走線的密度與層數(shù)的折衷等問(wèn)題。本系統(tǒng)中29×29的BGA780封裝的扇出是決定信號(hào)層層數(shù)的重要因素,假設(shè)1 mm球間距間扇出一根導(dǎo)線,在沒有考慮頂層扇出限制和扇出線物理連接限制的情況下,可以計(jì)算出528個(gè)用戶I/O端口加上少量配置線至少需要5個(gè)信號(hào)層,加上電源層后的總層數(shù)將達(dá)到8~12層,導(dǎo)致層數(shù)過(guò)大。結(jié)合加工工藝和串?dāng)_分析等情況,在允許的范圍內(nèi)盡可能降低層數(shù)的原則,最終確定間距39.37 mils扇出2根導(dǎo)線, 其中包括14 mils 的扇出過(guò)孔、5 mils的線寬和扇出線間距。采用信號(hào)1-電源-信號(hào)2-信號(hào)3-地-信號(hào)4的層疊方案。信號(hào)線線寬為5mils時(shí)的特征阻抗控制為50 ?贅。

2.2 阻抗匹配設(shè)計(jì)與仿真

輸出緩沖的源端內(nèi)阻、高速系統(tǒng)中傳輸線的特征阻抗以及輸入緩沖的輸入電阻間的差距帶來(lái)了信號(hào)傳輸過(guò)程中的反射。當(dāng)輸出門的信號(hào)在傳輸介質(zhì)上往返時(shí)間大于信號(hào)最小邊沿時(shí)間時(shí),電路需采取端接來(lái)實(shí)現(xiàn)阻抗匹配,端接可采用末端并接電阻或源端串接電阻等方式。

末端端接將電阻放置于接收器端一側(cè),驅(qū)動(dòng)波形沿傳輸線以滿幅度傳播,到達(dá)末端時(shí)由端接電阻吸收,接收電壓等于傳輸電壓。末端端接具有上升時(shí)間快的優(yōu)點(diǎn),但對(duì)輸出門的驅(qū)動(dòng)電流有一定的要求,這也帶來(lái)了較大的功率消耗。

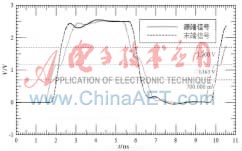

源端端接采取控制輸出端的反射系數(shù)的方法。通過(guò)在源端串接一個(gè)電阻,使得串接電阻加上源端緩沖器的內(nèi)阻接近傳輸線的特征阻抗。Cyclone IV系列產(chǎn)品均設(shè)計(jì)了OCT功能,可以選擇使用片內(nèi)串接電阻。使用SigXplorer軟件首先提取PCB上AD9765數(shù)據(jù)線的傳輸線模型,然后與Altera提供的TTL 2.5 V串接50 ?贅電阻的IBIS模型進(jìn)行125 MHz信號(hào)的反射仿真,仿真結(jié)果如圖3所示。源端信號(hào)波形的幅度由于端接電阻的分壓,在傳輸介質(zhì)上的初始信號(hào)幅度降至滿幅度信號(hào)的1/2,這1/2幅度的信號(hào)大約經(jīng)過(guò)1 ns后到達(dá)末端。由于末端數(shù)字電路輸入阻抗非常大,反射系數(shù)接近+1,從而得到1/2幅度的反射信號(hào),與原1/2幅度信號(hào)疊加后在末端得到完整幅度的信號(hào)。反射信號(hào)再經(jīng)過(guò)1 ns延遲后回到源端,被源端端接衰減,此類端接具有靜態(tài)功率小等優(yōu)點(diǎn)。

圖3 TTL 2.5 V 串接50 Ω電阻模型仿真圖

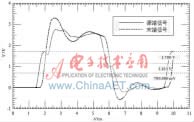

同時(shí)對(duì)未串接50 Ω電阻的TTL 2.5 V 模型進(jìn)行了仿真,其它仿真參數(shù)均不變的情況下,發(fā)現(xiàn)電路末端信號(hào)具有明顯過(guò)沖現(xiàn)象,如圖4所示。因而Cyclone IV的OCT技術(shù)是簡(jiǎn)化高速線路PCB板設(shè)計(jì)、提高信號(hào)完整性最簡(jiǎn)便實(shí)用的途徑。實(shí)驗(yàn)表明,測(cè)量結(jié)果與仿真波形接近,AD9765在最高理論速度125 MHz下工作穩(wěn)定。

圖4 TTL 2.5 V 未串接50 Ω電阻模型仿真圖

2.3 串?dāng)_仿真

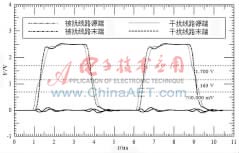

互感、互容使得相鄰傳輸線間信號(hào)相互耦合從而形成串?dāng)_,傳輸線的間距是其中最關(guān)鍵的因素。本系統(tǒng)中大多數(shù)走線間距為15 mils,無(wú)需擔(dān)心串?dāng)_問(wèn)題,而BGA的扇出采用的是5 mils的間距, 并且存在許多長(zhǎng)度在1 000 mils以上的平行線,串?dāng)_的仿真與降低串?dāng)_的影響成為設(shè)計(jì)過(guò)程中不可缺少的一個(gè)環(huán)節(jié)。采用SigXplorer對(duì)相鄰BGA扇出微帶線的模型進(jìn)行了仿真,結(jié)果如圖5所示。干擾源是125 MHz的時(shí)鐘信號(hào),被干擾線路為相距干擾線路5 mils的弱下拉平行微帶線。可見在被擾線路的源端和末端產(chǎn)生了接近200 mV的串?dāng)_,屬于電路正常工作可以接受的范圍。

設(shè)計(jì)了基于FPGA的NoC系統(tǒng)硬件平臺(tái),在此基礎(chǔ)上完成了一個(gè)小型的片上網(wǎng)絡(luò)系統(tǒng)。設(shè)計(jì)過(guò)程中充分考慮了片上網(wǎng)絡(luò)系統(tǒng)的應(yīng)用特點(diǎn),針對(duì)典型3×3的2D Mesh結(jié)構(gòu)進(jìn)行設(shè)計(jì)。實(shí)踐表明,系統(tǒng)達(dá)到了設(shè)計(jì)要求,可以滿足NoC系統(tǒng)的硬件要求,同時(shí)系統(tǒng)也將作為后續(xù)NoC映射、路由及測(cè)試算法的驗(yàn)證與仿真平臺(tái)。

圖5 串?dāng)_信號(hào)仿真圖

NoC仍然有著廣闊的研究空間,許多新的結(jié)構(gòu)或算法將會(huì)不斷涌現(xiàn),以及更復(fù)雜應(yīng)用系統(tǒng)的驗(yàn)證需求對(duì)硬件平臺(tái)會(huì)有更高的要求。本文對(duì)平臺(tái)設(shè)計(jì)中一些重要的問(wèn)題進(jìn)行了探討, 對(duì)于后續(xù)相關(guān)硬件平臺(tái)的開發(fā)及FPGA應(yīng)用系統(tǒng)的設(shè)計(jì)具有一定的借鑒意義。

參考文獻(xiàn)

[1] AXEL J,HANNU T. 網(wǎng)絡(luò)化芯片[M]. 王忠,孫繼銀,等譯.西安:西安交通大學(xué)出版社,2007.

[2] 周干民.基于通訊的NoC 設(shè)計(jì)[J].微電子學(xué)與計(jì)算機(jī),2006,23(4):11-14.

[3] Altera Inc. Cyclone IV device handbook[Z]. http://www.altera.com,2010.2

[4] 蔡志翔,沈海斌.片上網(wǎng)絡(luò)的一種共享緩存的多路徑路由方法[J].機(jī)電工程,2010,6(6):96-99.

[5] Samsung. S3C2440 32-Bit Microcontroller User′s ManualZ].http://www.samsung.com,2004.12.