Critical Link公司的某客戶需要針對多個應(yīng)用開發(fā)一個擴(kuò)頻無線電收發(fā)器。該客戶已經(jīng)開發(fā)出一套算法,準(zhǔn)備用于對信號進(jìn)行調(diào)制和解調(diào),但他們卻缺少構(gòu)建完整系統(tǒng)的資源和專業(yè)知識。客戶希望利用軟件定義無線電(SDR)系統(tǒng)的靈活性優(yōu)勢。本文將探討如何基于德州儀器(TI)的OMAP-L138 DSP+ARM處理器與FPGA來實(shí)現(xiàn)該系統(tǒng)。

平臺

Critical Link選擇其MityDSP-L138F嵌入式系統(tǒng)模塊作為SDR的基礎(chǔ),因?yàn)樵撃K不僅具有很強(qiáng)的處理能力,而且可以為客戶節(jié)省大量的預(yù)先設(shè)計(jì)成本。MityDSP-L138F模塊具有一個TI的OMAP-L138DSP+ARM處理器,該處理器集成了一個456MHz ARM9處理內(nèi)核和一個456MHz TMS320C674x DSP內(nèi)核。此外,該模塊還包含了FPGA、NAND和NOR閃存以及DDR2存儲器。

出于原型考慮,該設(shè)計(jì)使用了TI針對無線電的高速ADC與DAC評估套件。此外,它還需要能夠在60MHz采樣頻率轉(zhuǎn)換的數(shù)據(jù)轉(zhuǎn)換器。

針對A/D轉(zhuǎn)換器,該設(shè)計(jì)選用了TI的ADS5562。該轉(zhuǎn)換器具有16位精度,可以以80Msps采樣速率進(jìn)行轉(zhuǎn)換。因?yàn)閿U(kuò)頻無線電需要將信號從背景噪聲中抽離,所以高動態(tài)范圍對于這種無線電來說非常重要。

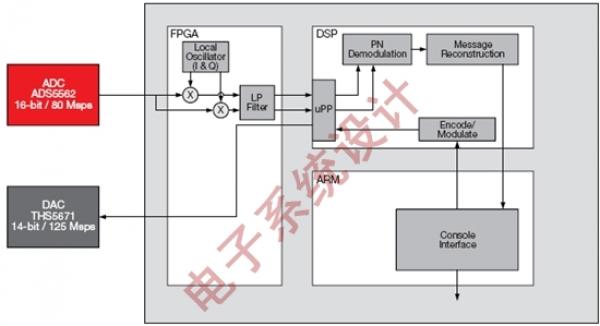

對于DAC,該平臺選用了TI的THS5671。這是一款14位125Msps差分電流輸出DAC。負(fù)責(zé)本項(xiàng)目的客戶為該系統(tǒng)提供的前端設(shè)計(jì)如圖所示。

圖:客戶提供的前端設(shè)計(jì)。

圖:客戶提供的前端設(shè)計(jì)。

數(shù)據(jù)傳送問題

許多基于DSP的應(yīng)用要求具有高速數(shù)據(jù)傳輸功能,以使系統(tǒng)能夠采集和處理數(shù)據(jù),或者將數(shù)據(jù)傳送到外設(shè)。通常,數(shù)字信號處理器都包含了異步地址/數(shù)據(jù)總線,以使處理器能夠讀寫外設(shè)。這些接口可以滿足低速傳送數(shù)據(jù)的要求,但是在高速情況下卻會成為瓶頸。

OMAP-L138 DSP+ARM處理器具有一個稱為外部存儲器接口A(EMIFA)的地址/數(shù)據(jù)總線。EMIFA允許對外部存儲器或設(shè)備進(jìn)行異步尋址,并含有若干控制引腳,以滿足不同等待狀態(tài)和傳輸寬度等等要求。因?yàn)樵摻涌诰哂泻軓?qiáng)的通用性,所以每次事務(wù)處理都可以利用多個時鐘周期來完成。例如,最小的讀取周期需要每16位3個周期。在100MHz下運(yùn)行EMIFA,假設(shè)總線上沒有其他數(shù)據(jù),可得到的數(shù)據(jù)傳輸速率最大為66MB/s。在總線上進(jìn)行交錯讀寫會顯著地降低傳輸速率,因?yàn)檫@必須增加額外的轉(zhuǎn)換周期。

OMAP-L138處理器還包括了一個更為專用的接口,即通用并行端口(uPP)。該接口專門用來將大量數(shù)據(jù)連續(xù)送入處理器內(nèi)存或從其中讀出。uPP的傳輸速率為每時鐘周期1個數(shù)據(jù)字(8位或16位);或者針對雙數(shù)據(jù)速率為每時鐘周期2個數(shù)據(jù)字,但是時鐘速率必須減半。uPP時鐘速率可以高達(dá)處理器時鐘速率的一半。對于在300MHz下運(yùn)行的OMAP-L138處理器,uPP時鐘可以達(dá)到75MHz。這使吞吐量可以達(dá)到150MB/s。

OMAP-L138處理器實(shí)際包括2個uPP接口,每個都可以單獨(dú)配置。這允許我們?yōu)閼?yīng)用建立一個傳輸端口和一個接收端口,從而消除單一總線上的資源爭用問題。

從硬件角度看,uPP接口是一種非常簡單的同步數(shù)據(jù)接口。它包含一個時鐘引腳、數(shù)據(jù)引腳和若干控制引腳,用于指明有效數(shù)據(jù)和起始/等待條件。事實(shí)上,該接口可以與一些并行ADC和DAC實(shí)現(xiàn)無縫連接。

架構(gòu)

因?yàn)槲覀兊腟DR需要與DSP之間進(jìn)行高速數(shù)據(jù)傳送,所以我們選擇使用uPP端口來實(shí)現(xiàn)FPGA接口。我們使用一個端口作為接口的發(fā)送端,使用另一端口作為接收端。事實(shí)上,該處理系統(tǒng)可以同時進(jìn)行發(fā)送和接收,盡管這并非系統(tǒng)要求。這個功能的優(yōu)勢在于,它允許我們在發(fā)送器和接收器之間建立循環(huán),以進(jìn)行大量的測試和調(diào)試工作。

對于一個10MHz載波來說,這種調(diào)制所需的處理特性,使系統(tǒng)過多地將全部處理任務(wù)在OMAP-L138處理器的DSP中完成。在速度較慢的應(yīng)用中,DSP可以單獨(dú)滿足數(shù)據(jù)速率的要求,但由于客戶要求以更高的速率發(fā)送數(shù)據(jù),所以我們需要使用FPGA來執(zhí)行部分處理任務(wù)。

FPGA尤其擅長以非常高的頻率執(zhí)行重復(fù)任務(wù),因此,我們選擇在FPGA中執(zhí)行初始解調(diào)和基帶處理。這樣,我們就可以大量減少DSP中的數(shù)據(jù)并降低DSP的數(shù)據(jù)速率。在發(fā)送側(cè),DSP可以預(yù)先計(jì)算最終的射頻信號,以便將有效負(fù)載數(shù)據(jù)的編碼時間降至最短。因此,F(xiàn)PGA僅僅將發(fā)送波形數(shù)據(jù)從uPP端口發(fā)送到DAC。事實(shí)上,不使用FPGA也可以完成這項(xiàng)工作,但是我們在設(shè)計(jì)系統(tǒng)時仍將FPGA加入,以便在需要時使用。

FPGA的雙端口RAM中包含一個正弦或余弦查找表,用于合成接收機(jī)的本機(jī)振蕩器信號。FPGA中的乘法器/累加器用于根據(jù)要求解調(diào)信號。

發(fā)送處理鏈

當(dāng)ARM微處理器上的軟件向DSP發(fā)出傳輸消息包時,發(fā)送過程將會啟動。DSP對數(shù)據(jù)進(jìn)行編碼,使其成為擴(kuò)頻調(diào)制序列,并將其編入一個預(yù)先計(jì)算的已調(diào)制正弦波查找表。然后,DSP使用uPP的內(nèi)置DMA引擎建立一個DMA傳輸,用以將數(shù)據(jù)從DSP存儲器傳送到DAC。FPGA則起到中間調(diào)解作用,負(fù)責(zé)向DAC和uPP提供可編程時鐘,用于設(shè)置發(fā)送采樣率。

接收處理鏈

接收流程連續(xù)運(yùn)行。ADC樣本被同步送入FPGA——通過將輸入樣本與正交正弦和余弦波形相乘并積分,對數(shù)據(jù)進(jìn)行基帶處理,從而以較低的數(shù)據(jù)速率向DSP提供同相和正交樣本。這些樣本被uPP DMA引擎以DMA方式送入DSP存儲器,再由DSP處理剩余的擴(kuò)頻解調(diào)處理步驟。一旦信號被解調(diào),得到的數(shù)據(jù)包將使用TI的DSPLink處理器之間通信庫傳送回ARM處理器。ARM軟件接收解碼數(shù)據(jù),并通過命令接口將數(shù)據(jù)呈現(xiàn)給用戶。

使用FPGA執(zhí)行接收器初始基帶處理能夠釋放足夠的DSP處理能力,從而輕松完成剩余的解調(diào)和解碼工作。如果系統(tǒng)中的輸入信號采樣率顯著低于60MHz,則DSP可不借助FPGA的力量,獨(dú)自執(zhí)行基帶處理任務(wù)。

該系統(tǒng)的初始工作使用了一個低頻段(幾十或幾百kHz)的載頻。在初始實(shí)施過程中,F(xiàn)PGA僅負(fù)責(zé)將數(shù)據(jù)發(fā)送至DSP,由DSP執(zhí)行所有的解調(diào)功能。這種方式很奏效,但是無法達(dá)到更高采樣率應(yīng)用的要求。通過在FPGA中實(shí)施基帶處理,我們可以在全采樣率下進(jìn)行數(shù)字基帶處理和濾波,從而改善系統(tǒng)的噪聲性能:這在欠采樣下是無法做到的。

本文小結(jié)

該項(xiàng)目實(shí)現(xiàn)的原型系統(tǒng)已經(jīng)為多個應(yīng)用實(shí)施過概念驗(yàn)證。與理想擴(kuò)頻無線電的理論性能相比,該系統(tǒng)的性能非常優(yōu)異。TI OMAP-L138 DSP+ARM處理器與FPGA的結(jié)合,實(shí)現(xiàn)了具有出色性能的高性價(jià)比解決方案。將DSP的部分處理負(fù)載分配給FPGA,使系統(tǒng)可以使用低成本、低功耗的處理器來構(gòu)建,而不是由GHz級的DSP處理所有工作。uPP接口支持簡單的FPGA接口功能,并且與其他可用的DSP接口相比,具有明顯的性能優(yōu)勢。使用uPP中的DMA進(jìn)行數(shù)據(jù)傳送,可以進(jìn)一步釋放DSP資源,將DSP周期用于更加重要的工作。

在OMAP-L1x平臺中加入ARM處理器后,便可使用嵌入式Linux提供通信基礎(chǔ)設(shè)施,來管理系統(tǒng)中的用戶界面和所有的內(nèi)務(wù)處理功能。此外,使用SD卡、USB驅(qū)動器或者以太網(wǎng)連接,可以對系統(tǒng)軟件(ARM、DSP和FPGA)進(jìn)行現(xiàn)場升級。因此,SDR系統(tǒng)的靈活性可以充分滿足處理算法的發(fā)展要求。