作者:郭盛杰,尹 帥

1 ispPAC10的結(jié)構(gòu)與原理

1.1 ispPAC10的結(jié)構(gòu)特點

ispPAC10器件的結(jié)構(gòu)由四個相同的信號處理塊(PAC塊),模擬布線池,配置存儲器,參考電壓,自動校正單元和ISP接口所組成,如圖1。

ispPAC10引腳如圖2。

其封裝形式是:

28引腳的DIP或SOIC封裝。

引腳功能如下:

輸入:3,4,11,12,17,18,25,26

輸出:1,2,13,14,15,16,27,28

數(shù)字L/O:5,6,8,9,10,20

電源引腳:7,21

CMVIN引腳:19

測試引腳:23,24

(電源電壓為5 V;電源引腳用一個10μF的鉭電容和一個1μF的陶瓷電容旁路到地上可獲取最佳性能)。

1.2 ispPAC10的工作原理

ispPAC10器件有4個相同的基本單元電路。每個PACblock含有兩個獨立可編程的輸入放大器、一個差分輸出放大器、一個電阻反饋元件(可開路)和一個可調(diào)的反饋電容器。PACblock的輸入端為兩對差分輸入,增益可在±1~±10以整數(shù)步長調(diào)節(jié)。輸出求和放大器的反饋回路由一個電阻和一個電容并聯(lián)組成。

每個PACblock的輸入阻抗為109 Ω。輸入放大器可建模為一個可編程的增益模塊(K1和K2)和一個求和電阻器。輸入放大器提供的電流在一個運算放大器的反相輸入端被累加。輸出放大器的反饋網(wǎng)絡(luò)可建模為一個定值電阻元件并聯(lián)一個可調(diào)電容器(可調(diào)電容值為120個在1pF至62pF之間的值)。電阻反饋通路可以被禁用。運算放大器的輸出為差分電壓。

2 iSpPAC10功能及應(yīng)用

2.1 整數(shù)增益的設(shè)置

2.1.1 增益值為4的PACblock配置

通常情況下,PACblock中單個輸入放大器的增益可在±1~±10的范圍內(nèi)按整數(shù)步長進行調(diào)整。IA1和IA2是求和的關(guān)系,如果所求的增益在±10之間,那就只需用其中一個。如圖3所示,將IA1的增益設(shè)置為4,則可得到輸出電壓VOUT1相對于輸入電壓VIN1為4的增益。

2.2 小數(shù)增益的設(shè)置

2.2.1 精度為0.1的增益設(shè)置

為設(shè)置一個40.7的增益,可以由增益值為40開始,從輸入到輸出增加一個0.7的額外增益。有兩種方法給一個ispPAC10設(shè)計增加0.7的增益。

2.2.1.1 外部電阻分壓增益設(shè)置法

該方法是由輸入除以10,也就是(0.1 x Vin)。然后在另一個PACblock中把該電壓放大7倍,結(jié)果為(0.7×Vin)。

為了讓Vin除以10,需添加一個外部電阻器網(wǎng)絡(luò),同時為避免加載輸入,應(yīng)選用電阻值加起來≥100 kΩ的電阻器。

2.2.1.2 整數(shù)比率增益技術(shù)設(shè)置法

該方法是:當(dāng)反饋元件OA為開路狀態(tài),IA2輸入被連接到OA輸出時,IA1和IA2可以用來提供與它們增益值成比率的增益即IA1/IA2。

為了正確地實現(xiàn)這種技術(shù),IA2的增益必須設(shè)置成負(fù)數(shù)。為獲取0.7的增益,需設(shè)置IA1為7,IA2為-10。表1列出了所有增益列表。采用這種技術(shù)不必使用外部電阻分壓器,維持了輸入阻抗1×109Ω。

2.2.2 精度為0.01的增益設(shè)置

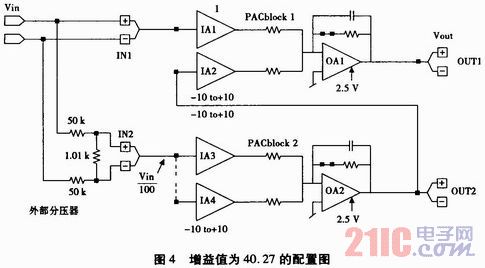

如果需要小于1的增益,而在表1里沒有找到,或者需要一個小于0.1的增益,就必須采用外部電阻分壓增益設(shè)置法,并通過改變電阻值來推導(dǎo)出一個小分?jǐn)?shù)輸入信號。如果需要一個40.27的增益,采用電阻分壓器的方法推導(dǎo)出除以100的輸入(見圖4)。用一個1.01 kΩ電阻器和兩個50 kΩ電阻器得到精度為0.01的數(shù)值(Vin×0.01),并乘以27得到(0.27×Vin),然后把產(chǎn)生的電壓加到增益為40的分級。如圖4已經(jīng)被化簡成主要顯示(Vin×0.27)增益區(qū)域。此種設(shè)計方案的增益精度依賴于電阻分壓器網(wǎng)絡(luò)的精度。

4 結(jié)論

系統(tǒng)可編程模擬電路ispPAC能夠在單個芯片上實現(xiàn)信號的增益調(diào)整,無需使用一大堆的運算放大器、電阻、電容等模擬器件,其設(shè)計過程就是利用開發(fā)軟件PAC—Designer在計算機上進行電路原理圖設(shè)計,原理圖設(shè)計完成后,可利用開發(fā)軟件提供的仿真功能對所設(shè)計的電路進行增益仿真,然后下載到器件中,即完成設(shè)計。整個設(shè)計過程簡便、直觀、快捷、準(zhǔn)確,且具有可反復(fù)編程、開發(fā)設(shè)計周期短、穩(wěn)定可靠、成本和功耗低等特點。