1、異步FIFO介紹

在現(xiàn)代的集成電路芯片中,隨著設(shè)計規(guī)模的不斷擴大,一個系統(tǒng)中往往含有數(shù)個時鐘。多時鐘域帶來的一個問題就是,如何設(shè)計異步時鐘之間的接口電路。異 步 FIFO(First In First Out)是解決這個問題一種簡便、快捷的解決方案。使用異步FIFO可以在兩個不同時鐘系統(tǒng)之間快速而方便地傳輸實時數(shù)據(jù)。在網(wǎng)絡(luò)接口、圖像處理等方面, 異步FIFO得到了廣泛的應(yīng)用。

異步FIFO是一種先進先出的電路,使用在需要產(chǎn)時數(shù)據(jù)接口的部分,用來存儲、緩沖在兩個異步時鐘之間的數(shù)據(jù)傳輸。在異步電路中,由于時鐘之間周期 和相位完全獨立,因而數(shù)據(jù)的丟失概率不為零。如何設(shè)計一個高可靠性、高速的異步FIFO電路便成為一個難點。本文介紹解決這一問題的一種方法。

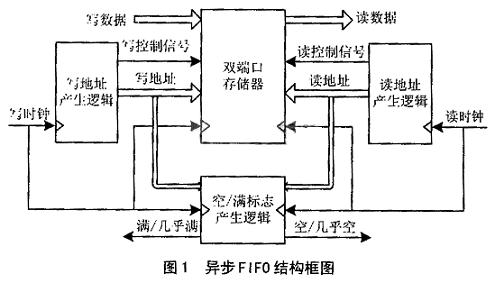

由圖1可以看出:整個系統(tǒng)分為兩個完全獨立的時鐘域——讀時鐘域和寫時間域;FIFO的存儲介質(zhì)為一塊雙端口RAM,可以同時進行讀寫操作。在寫時 鐘域部分,由寫地址產(chǎn)生邏輯產(chǎn)生寫控制信號和寫地址;讀時鐘部分由讀地址產(chǎn)生邏輯產(chǎn)生讀控制信號和讀地址。在空/滿標志產(chǎn)生部分,由讀寫地址相互比較產(chǎn)生 空/滿標志。

2、異步FIFO的設(shè)計難點

設(shè)計異步FIFO有兩個難點:一是如何同步異步信號,使觸發(fā)器不產(chǎn)生亞穩(wěn)態(tài);二是如何正確地設(shè)計空、滿以及幾乎滿等信號的控制電路。

下面闡述解決問題的具體方法。

2.1 亞穩(wěn)態(tài)問題的解決

在數(shù)字集成電路中,觸發(fā)器要滿足setup/hold的時間要求。當一個信號被寄存器鎖存時,如果信號和時鐘之間不滿足這個要求,Q端的值是不確定 的,并且在未知的時刻會固定到高電平或低電平。這個過程稱為亞穩(wěn)態(tài)(Metastability)。圖2所示為異步時鐘和亞穩(wěn)態(tài),圖中clka和clkb 為異步時鐘。

亞穩(wěn)態(tài)必定會發(fā)生在異步FIFO中。圖中在異步FIFO中,電路外部的輸入和內(nèi)部的時鐘之間是毫無時間關(guān)系的,因此setup/hold沖突是必然的;同在電路內(nèi)部的兩個沒有關(guān)系的時鐘域之間的信號傳遞,也必須會導致setup/hold沖突。

雖然亞穩(wěn)態(tài)是不可避免的,但是,下面的設(shè)計改進可以將其發(fā)生的概率降低到一個可以接受的程度。

①對寫地址/讀地址采用格雷碼。由實踐可知,同步多個異步輸入信號出現(xiàn)亞穩(wěn)態(tài)的概率遠遠大于同步一個異步信號的概率。對多個觸發(fā)器的輸出所組成的寫地址/讀地址可以采用格雷碼。由于格雷碼每次只變化一位,采用格雷碼可以有效地減少亞穩(wěn)態(tài)的產(chǎn)生。

②采用觸發(fā)器來同步異步輸入信號,如圖3中的兩極觸發(fā)器可以將出現(xiàn)亞穩(wěn)態(tài)的幾率降低到一個很小的程度。但是,正如圖3所示,這種方法同時帶來了對輸入信號的一級延時,需要在設(shè)計時鐘的時候加以注意。

2.2 空/滿標志的產(chǎn)生

空/滿標志的產(chǎn)生FIFO的核心部分。如何正確設(shè)計此部分的邏輯,直接影響到FIFO的性能。

空/ 滿標志產(chǎn)生的原則是:寫滿不溢出,讀空不多讀。即無論在什么進修,都不應(yīng)出現(xiàn)讀寫地址同時對一個存儲器地址操作的情況。在讀寫地址相等或相差一個或多個地 址的時候,滿標志應(yīng)該有效,表示此時FIFO已滿,外部電路應(yīng)對FIFO發(fā)數(shù)據(jù)。在滿信號有效時寫數(shù)據(jù),應(yīng)根據(jù)設(shè)計的要求,或保持、或拋棄重發(fā)。同理,空 標志的產(chǎn)生也是如此,即:

空標志<=(|寫地址-讀地址|<=預(yù)定值)AND(寫地址超前讀地址)

滿標志<=(|寫地址-讀地址|<=預(yù)定值)AND(讀地址超前寫地址)

最直接的做法是,采用讀寫地址相比較來產(chǎn)生空滿標志。如圖4所示,當讀寫地址的差值等于一個預(yù)設(shè)值的時候,空/滿信號被置位。這種實現(xiàn)方法邏輯簡 單,但它是減法器形成的一個比較大的組合邏輯,因而限制了FIFO的速度。所以,一般只采用相等不相等的比較邏輯,避免使用減法器。

圖5 是另外一種常用的設(shè)計,比較器只對讀寫地址比較是否相等。在讀寫地址相等的時候有兩種情況:滿或者空。所以,附加了一個并行的區(qū)間判斷邏輯來指示是空還是 滿。這個區(qū)間判斷邏輯將整個地址空間分為幾個部分,以指示讀寫地址的相對位置。這種做法提高了整個電路的速度,但是也有其缺點。主要是直接采用讀寫地址等 于不等于的比較邏輯來進行空/滿標志的判斷,可以帶來誤判。

3、新穎的FIF0空/滿標志控制邏輯

3.1 對讀寫地址的分析

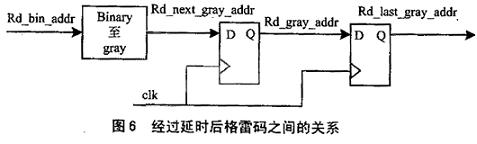

由以上對FIFO的分析可以看出,由地址直接相減和將地址相互比較產(chǎn)生空/滿標志都不可取。如何簡單地進行直接比較,又不提高邏輯的復雜程度呢?對 地址加延時可以做到這一點。設(shè)讀地址為Rd_bin_addr,用讀地址Rd_addr產(chǎn)生讀地址的格雷碼Rd_next_gray_addr,將 Rd_next_gray_addr延一拍得到Rd_gray_addr,再將Rd_gray_addr延一拍得到Rd_last_gray_addr。 在絕對時間上,Rd_next_gray_addr、Rd_gray_addr、Rd_last_gray_addr這些地址先后關(guān)系,從大到小排列,并 且相差一個地址,如圖6所示。

圖6 經(jīng)過延時后格雷碼之間的關(guān)系

寫地址的格雷碼的產(chǎn)生也與此類似,即:Wt_next_gray_addr、Wt_gray_addr、Wt_last_gray_addr。利用這6個格雷碼進行比較,同時加上讀寫使能,就能方便而靈活地產(chǎn)生空/滿標志。

以空標志Empty的產(chǎn)生為例,當讀寫格雷碼地址相等或者FIFO內(nèi)還剩下一個深度的字,并且正在不空的情況下執(zhí)行讀操作,這時Emptr標志應(yīng)該置為有效(高電平有效)。

即EMPTY<=(Rd_gray_addr=Wt_gray_addr)and(Read_enable=1)或EMPTY<=(Rd_next_gray_addr=Wt_gray_addr)and(Read_enable=1)

同理可類推滿標志的產(chǎn)生邏輯。

3.2 基于延時格雷碼的FIFO標志產(chǎn)生邏輯

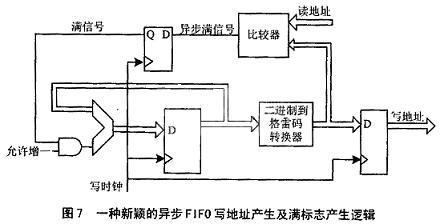

圖 7 是使用上述思想設(shè)計的地址產(chǎn)生和標志產(chǎn)生的邏輯。首先,在地址產(chǎn)生部分,將產(chǎn)生的格雷碼地址加一級延時,利用其前一級地址與當前的讀地址作比較。其次,在 空/滿標志有效的時候,采用了內(nèi)部保護機制,不使讀/寫地址進一步增加而出現(xiàn)讀寫地址共同對一個存儲單元操作的現(xiàn)象。

3.3 仿真信號波形

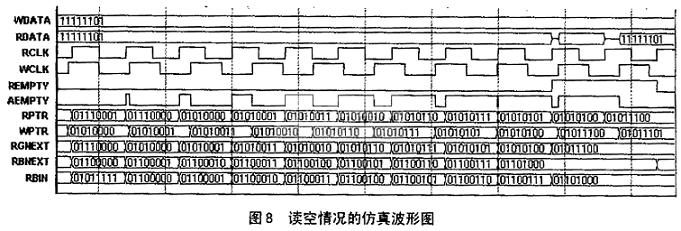

利用圖7電路設(shè)計的思想構(gòu)造了一個256×8的FIFO,用MODELSIM進行仿真。圖8為系統(tǒng)中主要信號對讀空情況的仿真波形。

圖8 讀空情況的仿真波形圖

圖8 中,WDATA為寫數(shù)據(jù),RDATA為讀數(shù)據(jù),WCLK為寫時鐘,RCLK為讀時鐘,REMPTY為空信號,AEMPTY的幾乎空信號,RPTR為讀地址 WPTR為寫地址,RGNEXT為下一位讀地址格雷碼,RBIN讀地址二進制,RBNEXT為下一位讀地址的二進制碼。

由圖8可以看出,由于讀時鐘高于寫時鐘,讀地址逐漸趕上寫地址,其中由AEMPTY信號指示讀地址和寫地址的接近程度。當這個信號足夠長而被觸發(fā)器捕捉到時,真正的空信號REMPTY有效。

4、電路優(yōu)點的分析

由圖7可見,該電路最大的瓶頸為二進制到格雷碼和比較器的延時之和。由于這兩個組合邏輯的延時都很小,因此該電路的速度很高。經(jīng)測試,在Xilinx的FPGA中,時鐘頻率可達140MHz。另外,由于將異步的滿信號加了一級鎖存,從而輸出了可靠而穩(wěn)定的標志。

5、總結(jié)

在實際工作中,分別用圖4、圖5與圖7中所示的邏輯實現(xiàn)了一個256×8的FIFO。綜合工具為SYNPLIFY7.0,由Foundation Series 3.3i布局布線后燒入Xilinx公司的WirtexEV100ECS144。三者的性能指標比較見表1。

表1 三種不同設(shè)計的比較

| 邏輯設(shè)計方式 | 時鐘頻率/MHz | 有效結(jié)果輸出頻率/MHz | slice數(shù)目/個 |

| 圖4所示邏輯 | 160 | 78.9 | 17 |

| 圖5所示邏輯 | 160 | 92 | 15 |

| 圖7所示邏輯 | 160 | 140 | 13 |

由表1可知,圖7所示的異步FIFO的電路速度高,面積小,從而降低了功耗,提高了系統(tǒng)的穩(wěn)定性。