一,、 概述

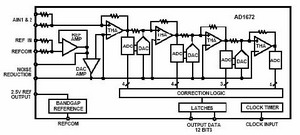

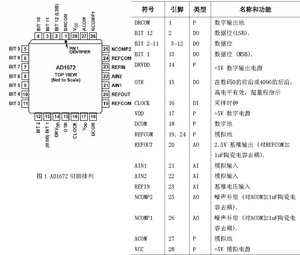

?????? ad1672是美國(guó)adi公司最近推向市場(chǎng)的一種新型單片式模數(shù)轉(zhuǎn)換器(adc)。片上含有4個(gè)高性能采樣保持放大器(sha)和4個(gè)閃爍式adc及電壓基準(zhǔn),。它采用4級(jí)流水線(xiàn)結(jié)構(gòu),,輸出帶有誤差修正邏輯電路,并采用bicmos工藝,,從而保證在3msps采樣速度下12位精度,,在整個(gè)工作溫度范圍內(nèi)不失碼。由于ad1672輸入sha具有快速建立特性,所以它既適合從負(fù)滿(mǎn)度到正滿(mǎn)度電壓逐次切換多通道系統(tǒng),,又適合輸入頻率高達(dá)奈奎斯特速率的單通道采樣,。 ad1672具有寬頻帶輸入、單電源供電,、低功耗和低價(jià)格等特點(diǎn),,非常適用于通信、圖象處理和醫(yī)療設(shè)備新電路設(shè)計(jì),。 ad1672采用28腳plcc封裝,,工作溫度范圍為-40~+85°c,其引腳排列見(jiàn)圖1,,引腳功能說(shuō)明見(jiàn)表1,。

4級(jí)閃爍式adc的分辨率分別為4,4,,3和4位,,其中每?jī)杉?jí)之間重疊1位用來(lái)誤差修正。用低噪聲sha采集滿(mǎn)度值,,單端輸入在167ns內(nèi)具有12位精度,。ad1672的工作過(guò)程,首先第一級(jí)閃爍式adc對(duì)輸入信號(hào)" title="輸入信號(hào)">輸入信號(hào)進(jìn)行4位近似轉(zhuǎn)換,,同時(shí)利用第1級(jí)數(shù)模轉(zhuǎn)換器(dac) 將這4位數(shù)字量轉(zhuǎn)換成對(duì)應(yīng)的精確模擬量,。再?gòu)牡?級(jí)sha輸出的模擬量減去第1級(jí)dac產(chǎn)生的模擬量得到一個(gè)殘差。然后,,第2級(jí)sha對(duì)這個(gè)殘差進(jìn)行采樣和保持,,第2級(jí)adc對(duì)此進(jìn)行4位近似轉(zhuǎn)換,同樣利用第2個(gè)dac得到第2級(jí)殘差,。一但第2級(jí)sha進(jìn)入保持方式,,第1級(jí)sha便返回到采樣方式,以采集新的輸入信號(hào),。第3級(jí)轉(zhuǎn)換與第1級(jí)和第2級(jí)類(lèi)似,,也由一個(gè)sha,一個(gè)adc和一個(gè)dac構(gòu)成,,不同之處分辨率不是4位而是3位,。第4級(jí),即最后一級(jí)轉(zhuǎn)換僅由1個(gè)4位閃爍式adc構(gòu)成,,完成最終殘差的模數(shù)轉(zhuǎn)換,。最后在修正邏輯單元,累計(jì)4級(jí)閃爍式adc構(gòu)成15位輸出,,但由于在累計(jì)過(guò)程中采用了適當(dāng)?shù)恼`差修正方法,,使最終輸出字為12位,。數(shù)字輸出" title="數(shù)字輸出">數(shù)字輸出連同超量程指示(otr)都被鎖存到輸出緩沖器以驅(qū)動(dòng)輸出引腳。

由于ad1672結(jié)構(gòu)的每一級(jí)都有一個(gè)附加的sha,,所以允許流水線(xiàn)轉(zhuǎn)換,。實(shí)際上這種模數(shù)轉(zhuǎn)換器是由多級(jí)輸入,同時(shí)轉(zhuǎn)換,,通過(guò)串行鏈方式完成四級(jí)轉(zhuǎn)換過(guò)程,。這表明,雖然這種轉(zhuǎn)換器在每個(gè)時(shí)鐘周期都具有捕獲新輸入信號(hào)的能力,,但要完成全部轉(zhuǎn)換并且在輸出端呈現(xiàn)數(shù)字量,,實(shí)際上只用2 1/2個(gè)時(shí)鐘周期。這種“流水線(xiàn)延遲(pipeline delay)”在許多應(yīng)用中它并不引人注意,,只是在有些情況下才考慮這個(gè)問(wèn)題,。例如,在高速反饋環(huán)路要求使用adc的一些場(chǎng)合,,只有提供一個(gè)理想的數(shù)字輸出結(jié)果,,才能對(duì)其輸入信號(hào)進(jìn)行補(bǔ)償(例如,視頻應(yīng)用中的失調(diào)校準(zhǔn)或零點(diǎn)恢復(fù)),。在這種情況下,在計(jì)算環(huán)路穩(wěn)定性時(shí),,必須考慮通過(guò)流水線(xiàn)引起的時(shí)鐘延時(shí),。另外,由于轉(zhuǎn)換器同時(shí)在3個(gè)轉(zhuǎn)換器上工作,,所以在轉(zhuǎn)換過(guò)程的主要交接處(例如,,電源或基準(zhǔn)引起的大的尖峰毛刺)會(huì)使3個(gè)采樣數(shù)據(jù)變壞。最后應(yīng)當(dāng)說(shuō)明,,ad1672存在一個(gè)最小的時(shí)鐘速率,,低于這個(gè)最小值,sha的頂降率會(huì)使流水線(xiàn)信號(hào)變壞,,這個(gè)最小時(shí)鐘速率在25°c 時(shí)為20khz,。通常時(shí)鐘速率選取3mhz。

ad1672的內(nèi)部定時(shí)控制電路利用了時(shí)鐘的上升沿" title="上升沿">上升沿和下降沿,。ad1672在時(shí)鐘輸入的上升沿對(duì)模擬輸入信號(hào)采樣,。當(dāng)時(shí)鐘處于低電平期間(處于時(shí)鐘下降沿和上升沿之間),輸入sha處于采樣方式;當(dāng)時(shí)鐘處于高電平期間,,則sha處于保持方式,。由于這種器件利用時(shí)鐘上升沿和下降沿定時(shí),所以?xún)H在時(shí)鐘上升沿,,抖動(dòng)才很明顯,。

三,、應(yīng)用

1.模擬輸入

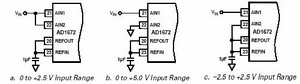

ad1672等效模擬輸入電路如圖3所示,其中輸入sha及其輔助電阻網(wǎng)絡(luò)很容易接成單極性(0~2.5v或0~5.0v)或雙極性(- 2.5~+2.5v),,見(jiàn)圖4,。ad1672標(biāo)稱(chēng)輸入電阻rin,對(duì)于 2.5 v輸入范圍為2kω,,對(duì)于5.0v輸入范圍為4kω,。圖3 等效模擬輸入電路

圖4 輸入范圍選擇 ad1672雖然是單電源+5v供電,但同樣可用于交流輸入信號(hào),,見(jiàn)圖5,。由于耦合電容器與ad1672的輸入阻抗構(gòu)成一階高通濾波器,-3db轉(zhuǎn)折頻率f?3db計(jì)算公式為f?3db= 1

(2 ×π × rin × ceq )

其中rin 為不同接法時(shí)的輸入阻抗;ceq 為耦合電容器c1與c2的并聯(lián)值,。應(yīng)當(dāng)注意的是,,c1一般使用大的電解電容或鉭電容,有利于在高頻段導(dǎo)通,。又并聯(lián)一個(gè)小陶瓷電容c2,,使其在很寬的頻率范圍內(nèi)在低頻段仍然保持低阻抗特性。一般c1取10μf,,c2取0.1~1.0μf,。在直流耦合應(yīng)用中,推薦使用緩沖放大器驅(qū)動(dòng)ad1672的輸入,。一般選用高速,、寬頻帶視頻運(yùn)算放大器。由于緩沖放大器與ad1672的輸入電阻的相互作用,,任何源電阻都要對(duì)增益誤差" title="增益誤差">增益誤差和失調(diào)誤差" title="失調(diào)誤差">失調(diào)誤差有影響,。在直流精密測(cè)量應(yīng)用中,調(diào)整電路實(shí)例請(qǐng)見(jiàn)ad1672的產(chǎn)品說(shuō)明,。對(duì)于使用電源電壓大于6.5v的放大器,,在ad1672的輸入端推薦使用箝位電路。當(dāng)出現(xiàn)故障時(shí),,它可使輸入電壓箝位到6.5v,。

圖5 交流耦合輸入接線(xiàn)圖

基準(zhǔn)電壓 ad1672的標(biāo)稱(chēng)基準(zhǔn)輸出電壓相對(duì)基準(zhǔn)地(refcom)為2.5v?;鶞?zhǔn)輸入(refin)引腳可以接到基準(zhǔn)輸出(refout)引腳,,也可接到高精度2.5v外部基準(zhǔn)電壓源(例如ad780b,ref192e,,ref43b),。ad1672內(nèi)部含有+2.5v曲率補(bǔ)償帶隙基準(zhǔn),雖然其絕對(duì)值和溫漂系數(shù)都經(jīng)過(guò)激光修整,,但在refout與refcom引腳之間必須接一個(gè)1μf以上的補(bǔ)償電容器,。該基準(zhǔn)源可提供最大負(fù)載電流為500μa,,對(duì)于外接負(fù)載電流大于500μa情況下,需要外接緩沖放大器或上拉電阻器,。

數(shù)字輸出 ad1672在不同的輸入方式下輸出的數(shù)據(jù)形式不同:對(duì)于單極性輸入,,輸出數(shù)據(jù)是直接的二進(jìn)制碼;對(duì)于雙極性輸入,輸出數(shù)據(jù)是偏移二進(jìn)制碼,。當(dāng)數(shù)字輸出驅(qū)動(dòng)電源(drvdd)引腳分別接+5v或+3.3v時(shí),,可使ad1672cmos數(shù)字輸出驅(qū)動(dòng)器接口分別適合+5v或3.3v邏輯電路。雖然ad1672可以提供足夠大的輸出電流來(lái)驅(qū)動(dòng)范圍很寬的邏輯電路,,但是大的驅(qū)動(dòng)電流會(huì)產(chǎn)生電源引起的毛刺,,影響s/(n+d)性能。當(dāng)ad1762驅(qū)動(dòng)大的容性負(fù)載或大的扇出時(shí),,在drvdd 與v dd 引腳上都應(yīng)外接去耦電容,。在數(shù)據(jù)終端,需要外部緩沖器或鎖存器,,例如sn74hc541,,74hc541。

超量程

當(dāng)模擬輸入電壓超過(guò)輸出范圍(0~+2.5v,,0~+5.0v,,±2.5v)時(shí),會(huì)產(chǎn)生超量程現(xiàn)象,。ad1672提供超量程(otr)輸出引腳,,指示超量程,利用otr引腳和最高位(msb)的與非邏輯結(jié)果可確定欠量程(低電平)和超量程(高電平)狀態(tài),。增益誤差和失調(diào)誤差調(diào)整ad1672的增益誤差、失調(diào)誤差和線(xiàn)性誤差出廠(chǎng)時(shí)已經(jīng)調(diào)整到最小,,但是有些應(yīng)用仍需要通過(guò)外部調(diào)整將增益誤差和失調(diào)誤差調(diào)整到零,。因?yàn)檫@兩種誤差相互影響,所以需要反復(fù)調(diào)整,。利用otr引腳,,監(jiān)控它的輸出可分別在負(fù)滿(mǎn)度-fs和正滿(mǎn)度+fs兩種情況下將其調(diào)整到1/2 lsb范圍內(nèi),具體調(diào)整電路請(qǐng)見(jiàn)ad1672產(chǎn)品說(shuō)明,。 接地與電源去耦適當(dāng)?shù)亟拥嘏c去耦是高速,、高分辯率數(shù)據(jù)采集系統(tǒng)的基本設(shè)計(jì)要求。ad1672的特點(diǎn)是將模擬電源,、數(shù)字電源和地都分開(kāi),,使系統(tǒng)模擬地和數(shù)字地電路電流得到最佳管理。通常模擬電源和數(shù)字電源都應(yīng)分別對(duì)地接去耦電容,,并應(yīng)盡量靠近接地端,。對(duì)于數(shù)字輸出端呈現(xiàn)大的容性負(fù)載(通常每引腳為20pf),,在drvdd引腳對(duì)數(shù)字地應(yīng)接一個(gè)0.1μf陶瓷電容器。有關(guān)ad1672的詳細(xì)應(yīng)用情況,,包括模數(shù)轉(zhuǎn)換接口板的電路設(shè)計(jì)和印制線(xiàn)路板的布線(xiàn),,請(qǐng)參見(jiàn)ad1672產(chǎn)品說(shuō)明。