測(cè)頻是最基本的電子測(cè)量技術(shù)。常用的測(cè)頻方法有較大的局限性,其測(cè)量精度是隨被測(cè)信號(hào)頻率的下降而降低的,并且被測(cè)信號(hào)計(jì)數(shù)則產(chǎn)生±1個(gè)數(shù)字誤差。而采用等精度頻率測(cè)量方法測(cè)量精確,測(cè)量精度保持恒定;并且與CPLD(復(fù)雜可編程邏輯器件)相結(jié)合可使測(cè)頻范圍達(dá)到0.1 Hz~100 MHz,測(cè)頻全域相對(duì)誤差恒為1/1000。

智能化儀器通常以單片機(jī)為核心,而一般單片機(jī)自身計(jì)數(shù)器/定時(shí)器的計(jì)數(shù)/定時(shí)范圍或精度有時(shí)無(wú)法滿足系統(tǒng)要求。以89C51單片機(jī)為例,當(dāng)其內(nèi)部?jī)蓚€(gè)16位計(jì)數(shù)器/定時(shí)器T0和T1工作在計(jì)數(shù)方式時(shí),對(duì)T0(P3.4)或T1(P3.5)的外部脈沖進(jìn)行計(jì)數(shù)。當(dāng)T0或T1引腳上發(fā)生負(fù)跳變時(shí),計(jì)數(shù)器加1。由于識(shí)別引腳的負(fù)跳變需2個(gè)機(jī)器周期,即24個(gè)時(shí)鐘振蕩周期。T0/T1的最高頻率為1/24fosc,當(dāng)晶體振蕩器頻率為12MHz時(shí),其最高計(jì)數(shù)頻率為500 kHz。要求高測(cè)量頻率時(shí),則需對(duì)被測(cè)信號(hào)預(yù)處理以擴(kuò)展測(cè)頻范圍。

2 測(cè)量原理

要求測(cè)量頻率較高時(shí),則需對(duì)高頻和低頻采用不同的測(cè)量方法,提高測(cè)量精度。

2.1高頻測(cè)量

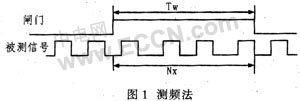

采用測(cè)頻法測(cè)量高頻。在確定的閾值時(shí)間Tw內(nèi),記錄被測(cè)信號(hào)的變化周期數(shù)(或脈沖數(shù))Nx,則被測(cè)信號(hào)的頻率:fx=Nx/Tw。測(cè)頻法原理如圖1。由于被測(cè)頻率較高,單片機(jī)難以測(cè)量,8051所測(cè)量最高頻率為500 kHz,因此采用CPLD和8051的內(nèi)部計(jì)數(shù)器組成32位計(jì)數(shù)器。CPLD的計(jì)數(shù)器為低16位,其進(jìn)位脈沖再向8051計(jì)數(shù)。CPLD延時(shí)為10 ns,因此,CPLD與8051按測(cè)頻原理可以精確測(cè)量50 Mz的頻率。

2.2低頻測(cè)量

采用測(cè)周法測(cè)量低頻。測(cè)周期法需用標(biāo)準(zhǔn)信號(hào)的頻率fs,待測(cè)信號(hào)的一個(gè)周期Tx內(nèi),記錄標(biāo)準(zhǔn)頻率的周期數(shù)為Ns,則被測(cè)信號(hào)的頻率為:fx=fs/Ns,其原理如圖2所示。由于被測(cè)頻率較低,故可采用8051測(cè)量。首先要將被測(cè)信號(hào)轉(zhuǎn)換成門控信號(hào),其轉(zhuǎn)換電路原理如圖3所示。

2.3脈寬測(cè)量

由于被測(cè)頻率較低,故可采用8051實(shí)現(xiàn)。將脈寬信號(hào)直接送人8051計(jì)數(shù)器,采用測(cè)周法來(lái)測(cè)量脈寬,標(biāo)準(zhǔn)信號(hào)頻率fs記錄標(biāo)準(zhǔn)頻率的周期數(shù)為Ns,則被測(cè)信號(hào)的脈寬為:Tx=Ns/fs。

3系統(tǒng)硬件電路設(shè)計(jì)

3.1單片機(jī)設(shè)計(jì)部分

快速測(cè)量的要求必須保證高精度測(cè)頻,必須采用高精度的標(biāo)準(zhǔn)頻率信號(hào)。由于單片機(jī)受本身時(shí)鐘頻率和指令運(yùn)算限制,因此,測(cè)頻速度較慢,無(wú)法滿足高速、高精度測(cè)頻要求。采用高集成度、高速可編程門陣列CPLD可實(shí)現(xiàn)快速、高精度測(cè)頻。其硬件電路如圖4所示。

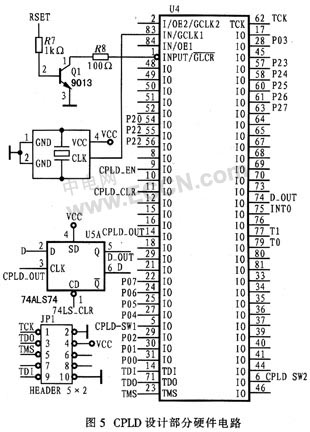

3.2 CPLD設(shè)計(jì)部分

利用CPLD作為計(jì)數(shù)器的低16位,而89S51內(nèi)部計(jì)數(shù)器作為計(jì)數(shù)器的高16位,在門控時(shí)間內(nèi)分別對(duì)被測(cè)信號(hào)和標(biāo)準(zhǔn)信號(hào)進(jìn)行計(jì)數(shù)。由于單片機(jī)具有程序運(yùn)算能力,且頻率為周期的倒數(shù)(f=1/T),則測(cè)頻法與測(cè)周法互通。CPLD設(shè)計(jì)部分的硬件電路如圖5所示。

4系統(tǒng)軟件設(shè)計(jì)

系統(tǒng)軟件設(shè)計(jì)采用Keil C51編寫(xiě)。由于單片機(jī)能夠完成大量運(yùn)算,且包含浮點(diǎn)數(shù)據(jù)處理。因此,并采用Keil C51便于運(yùn)行。并采用Keil C51自帶的軟件仿真器對(duì)所編寫(xiě)的程序進(jìn)行仿真。

系統(tǒng)軟件設(shè)計(jì)流程為:?jiǎn)纹瑱C(jī)初始化、LCD初始化、計(jì)數(shù)器清零、單片機(jī)發(fā)出啟動(dòng)脈沖,來(lái)啟動(dòng)CPLD的兩個(gè)低16位計(jì)數(shù)器和單片機(jī)的兩個(gè)高16位計(jì)數(shù)器。此時(shí),計(jì)數(shù)器并不開(kāi)始計(jì)數(shù),直到下一個(gè)Tx上升沿到來(lái),計(jì)數(shù)器才開(kāi)始計(jì)數(shù),軟件延時(shí)1 s后,發(fā)出結(jié)束脈沖來(lái)結(jié)束CPLD的兩個(gè)低16位計(jì)數(shù)器計(jì)數(shù),但此時(shí),計(jì)數(shù)器并不停止計(jì)數(shù),而是直到下一個(gè)Fx上升沿兩個(gè)計(jì)數(shù)器才都停止計(jì)數(shù),隨后關(guān)閉單片機(jī)的兩個(gè)計(jì)數(shù)器。CPLD發(fā)送結(jié)束信號(hào),單片機(jī)響應(yīng)中斷。中斷函數(shù)分兩次讀取CPLD的兩個(gè)計(jì)數(shù)器值。進(jìn)而單片機(jī)處理兩個(gè)32位計(jì)數(shù)器值。調(diào)用顯示函數(shù)顯示頻率,從而完成一次測(cè)頻。圖6為系統(tǒng)軟件設(shè)計(jì)流程圖。

5 結(jié)語(yǔ)

本系統(tǒng)設(shè)計(jì)經(jīng)系統(tǒng)測(cè)試,測(cè)試數(shù)據(jù)符合要求。因此,該信號(hào)測(cè)量?jī)x具有電路簡(jiǎn)單、體積小巧、便于攜帶、功能強(qiáng)大,中文液晶顯示等特點(diǎn)。其頻率測(cè)量范圍可達(dá)0.1 Hz~100MHz,并可隨意切換被測(cè)信號(hào)的頻率、周期和脈寬,具有較強(qiáng)的實(shí)用價(jià)值。