引言

由于系統(tǒng)帶寬不斷的增加,因此針對(duì)更高的速度和性能,設(shè)計(jì)人員對(duì)存儲(chǔ)技術(shù)進(jìn)行了優(yōu)化。下一代雙數(shù)據(jù)速率(DDR)SDRAM芯片是DDR3 SDRAM。 DDR3 SDRAM具有比DDR2更多的優(yōu)勢(shì)。這些器件的功耗更低,能以更高的速度工作,有更高的性能(2倍的帶寬),并有更大的密度。與DDR2相比,DDR3器件的功耗降低了30%,主要是由于小的芯片尺寸和更低的電源電壓(DDR3 1.5V而DDR2 1.8V)。 DDR3器件還提供其他的節(jié)約資源模式,如局部刷新。與DDR2相比,DDR3的另一個(gè)顯著優(yōu)點(diǎn)是更高的性能/帶寬,這是由于有更寬的預(yù)取緩沖(與4位的DDR2相比,DDR3為8位寬),以及更高的工作時(shí)鐘頻率。然而,設(shè)計(jì)至DDR3的接口也變得更具挑戰(zhàn)性。在FPGA中實(shí)現(xiàn)高速、高效率的DDR3控制器是一項(xiàng)艱巨的任務(wù)。直到最近,只有少數(shù)高端(昂貴)的FPGA有支持與高速的DDR3存儲(chǔ)器可靠接口的塊。然而,現(xiàn)在新一代中檔的FPGA提供這些塊、高速FPGA架構(gòu)、時(shí)鐘管理資源和需要實(shí)現(xiàn)下一代DDR3控制器的I/O結(jié)構(gòu)。本文探討設(shè)計(jì)所遇到的挑戰(zhàn),以及如何用一個(gè)特定的FPGA系列LatticeECP3實(shí)現(xiàn)DDR3存儲(chǔ)器控制器。

DDR3存儲(chǔ)器控制器的挑戰(zhàn)

針對(duì)存儲(chǔ)器控制器,DDR3器件面臨一系列的挑戰(zhàn)。DDR3的工作頻率起始于DDR2的更高的工作頻率,然后趨于更高的頻率。 DDR3接口需要的時(shí)鐘速度超過(guò)400 MHz。這是對(duì)FPGA架構(gòu)的一個(gè)重大挑戰(zhàn)。針對(duì)DDR3存儲(chǔ)器控制器的架構(gòu),fly-by結(jié)構(gòu)和讀寫(xiě)調(diào)整變得更加復(fù)雜。

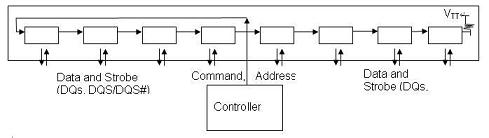

不同于DDR2的T型分支拓?fù)浣Y(jié)構(gòu),DDR3采用了fly-by拓?fù)浣Y(jié)構(gòu),以更高的速度提供更好的信號(hào)完整性。fly-by信號(hào)是命令、地址,控制和時(shí)鐘信號(hào)。如圖1所示,源于存儲(chǔ)器控制器的這些信號(hào)以串行的方式連接到每個(gè)DRAM器件。通過(guò)減少分支的數(shù)量和分支的長(zhǎng)度改進(jìn)了信號(hào)完整性。然而,這引起了另一個(gè)問(wèn)題,因?yàn)槊恳粋€(gè)存儲(chǔ)器元件的延遲是不同的,取決于它處于時(shí)序的位置。通過(guò)按照DDR3規(guī)范的定義,采用讀調(diào)整和寫(xiě)調(diào)整技術(shù)來(lái)補(bǔ)償這種延遲的差異。fly-by拓?fù)浣Y(jié)構(gòu)在電源開(kāi)啟時(shí)校正存儲(chǔ)器系統(tǒng)。這就要求在DDR3控制器中有額外的信息,允許校準(zhǔn)工作在啟動(dòng)時(shí)自動(dòng)完成。

圖1 針對(duì)DDR3的Fly-by結(jié)構(gòu)

讀和寫(xiě)調(diào)整

在寫(xiě)調(diào)整期間,存儲(chǔ)器控制器需要補(bǔ)償額外的跨越時(shí)間偏移(對(duì)每個(gè)存儲(chǔ)器器件,信號(hào)延遲是不同的),這是由于fly-by拓?fù)浣Y(jié)構(gòu)及選通和時(shí)鐘引入的。如圖2所示,源CK和DQS信號(hào)到達(dá)目的地有延遲。對(duì)于存儲(chǔ)器模塊的每個(gè)存儲(chǔ)器元件,這種延遲是不同的,必須逐個(gè)芯片進(jìn)行調(diào)整,如果芯片有多于一個(gè)字節(jié)的數(shù)據(jù),甚至要根據(jù)字節(jié)來(lái)進(jìn)行調(diào)整。該圖說(shuō)明了一個(gè)存儲(chǔ)器元件。存儲(chǔ)器控制器延遲了DQS,一次一步,直到檢測(cè)到CK信號(hào)從0過(guò)渡到到1。這將再次對(duì)齊DQS和CK,以便DQ總線上的目標(biāo)數(shù)據(jù)可以可靠地被捕獲。由于這是由DDR3存儲(chǔ)器控制器自動(dòng)做的,電路板設(shè)計(jì)人員無(wú)須擔(dān)心實(shí)施的細(xì)節(jié)。設(shè)計(jì)人員會(huì)從額外的裕度中得到好處,這是由DDR3存儲(chǔ)器控制器中的寫(xiě)調(diào)整的特性所創(chuàng)建的。

圖2 寫(xiě)調(diào)整的時(shí)序圖

DDR3存儲(chǔ)器時(shí)鐘資源和接口模塊

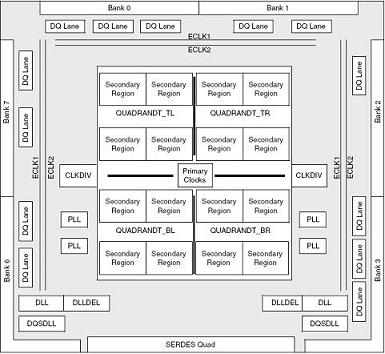

LatticeECP3 FPGA的I/O有專(zhuān)門(mén)的電路支持高速存儲(chǔ)器接口,包括DDR、DDR2和DDR3 SDRAM存儲(chǔ)器接口。如圖3所示,ECP3系列還有專(zhuān)用的時(shí)鐘資源,以支持下一代DDR3高速存儲(chǔ)器控制器。邊緣時(shí)鐘(ECLK1,ECLK2)是高速,低相偏的時(shí)鐘,用于時(shí)鐘控制數(shù)據(jù)高速地進(jìn)出器件。在DQS的通道提供時(shí)鐘輸入(DQS)和與該時(shí)鐘相關(guān)的多達(dá)10個(gè)輸入數(shù)據(jù)位。DQSBUF服務(wù)于每個(gè)DQS通道,以控制時(shí)鐘訪問(wèn)和延遲。DQSDLL支持DQS通道(每個(gè)器件的左側(cè)和右側(cè)都有一個(gè))。DQSDLL是專(zhuān)門(mén)用于構(gòu)建90度時(shí)鐘延遲的DLL。

圖3 LatticeECP3 DDR存儲(chǔ)器時(shí)鐘資源

萊迪思的DQS電路包括一個(gè)自動(dòng)時(shí)鐘轉(zhuǎn)換電路,簡(jiǎn)化了存儲(chǔ)器接口設(shè)計(jì),并確保了可靠的操作。此外,DQS的延遲塊提供了針對(duì)DDR存儲(chǔ)器接口所需的時(shí)鐘對(duì)齊。通過(guò)DQS的延遲單元至專(zhuān)用的DQS布線資源,向PAD提供DQS信號(hào)。溫度,電壓和工藝變化對(duì)專(zhuān)用DQS延遲塊產(chǎn)生的差異由設(shè)置的校準(zhǔn)信號(hào)來(lái)補(bǔ)償(7位延遲控制),校準(zhǔn)信號(hào)源于器件對(duì)邊的兩個(gè)DQSDLL。在器件的一半,每個(gè)DQSDLL彌補(bǔ)各自邊的DQS延遲。通過(guò)系統(tǒng)時(shí)鐘和專(zhuān)用反饋環(huán)路,對(duì)DLL環(huán)進(jìn)行了補(bǔ)償。

LatticeECP3 FPGA的鎖相環(huán)用于生成針對(duì)DDR3存儲(chǔ)器接口時(shí)鐘。例如,對(duì)于一個(gè)400 MHz的DDR3接口,通用鎖相環(huán)用于生成三個(gè)時(shí)鐘:400 MHz的時(shí)鐘,有90 °相移的400 MHz時(shí)鐘和200 MHz時(shí)鐘。有90 °相移的400 MHz時(shí)鐘用于生成DQ和DQS輸出。沒(méi)有相移的400 MHz時(shí)鐘用于產(chǎn)生時(shí)鐘(CLKP和CLKN)到DDR3存儲(chǔ)器。200 MHz時(shí)鐘用于生成地址和命令(ADDR/CMD)信號(hào)。該時(shí)鐘的實(shí)現(xiàn)對(duì)客戶(hù)是透明的,可用萊迪思的設(shè)計(jì)工具自動(dòng)地實(shí)現(xiàn)。

DDR3所需的寫(xiě)調(diào)整是通過(guò)使用動(dòng)態(tài)延遲輸入至專(zhuān)門(mén)的DDR3存儲(chǔ)器接口的模塊,這稱(chēng)為DQSBUFD模塊。這個(gè)DQSBUFD模塊包含了DQS延遲塊,時(shí)鐘極性控制邏輯和數(shù)據(jù)有效模塊。DDR3所需的寫(xiě)調(diào)整是通過(guò)使用動(dòng)態(tài)延遲(DYNDELAY)輸入DQSBUFD模塊。根據(jù)寫(xiě)調(diào)整的要求,可以延遲每個(gè)DQS組的輸出。

對(duì)于DDR3存儲(chǔ)器讀接口,當(dāng)存儲(chǔ)器件驅(qū)動(dòng)DQS為低電平時(shí),DQS轉(zhuǎn)換檢測(cè)塊檢測(cè)DQS的過(guò)渡情況,并生成讀時(shí)鐘來(lái)傳輸數(shù)據(jù)至FPGA。

萊迪思的IPexpress工具可用于生成上面闡述的DDR3存儲(chǔ)器接口塊。通過(guò)提供與高速DDR3存儲(chǔ)器接口所需的合適塊,這些在LatticeECP3中預(yù)制的塊使設(shè)計(jì)人員減少了設(shè)計(jì)的復(fù)雜性。

DDR3存儲(chǔ)器控制器

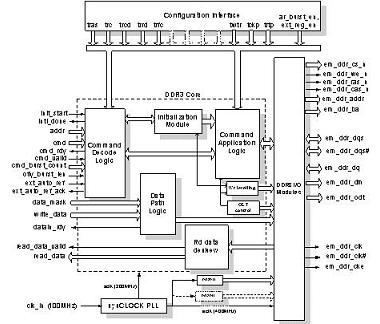

萊迪思提供一個(gè)全功能的DDR3存儲(chǔ)器控制器IP核,接口至符合行業(yè)標(biāo)準(zhǔn)的DDR3元件和DIMM。萊迪思的DDR3存儲(chǔ)器控制器的框圖如圖4所示。萊迪思的存儲(chǔ)器控制器連接到LatticeECP3 的DDR3存儲(chǔ)器接口模塊(IO模塊)和時(shí)鐘電路,針對(duì)接口至DDR3存儲(chǔ)器元件和DIMM,為客戶(hù)提供現(xiàn)成的解決方案。這個(gè)控制器實(shí)現(xiàn)了一些功能,以改善整個(gè)吞吐量。例如,實(shí)現(xiàn)命令流水線,以改善整體吞吐量。該IP使用有效的分組(bank)管理技術(shù)來(lái)并行管理多個(gè)分組。這可以使訪問(wèn)延遲最小,有利于提高存儲(chǔ)器的帶寬。

圖4 萊迪思DDR3存儲(chǔ)器控制器框圖

使用萊迪思的IPexpress工具,可以生成LatticeECP3 的DDR3存儲(chǔ)器控制器。基于GUI的工具使設(shè)計(jì)人員能夠指定存儲(chǔ)器控制器的參數(shù)(時(shí)鐘頻率、數(shù)據(jù)總線寬度、配置等)以生成DDR3存儲(chǔ)器控制器IP核。設(shè)計(jì)人員可以通過(guò)圖形用戶(hù)界面定制參數(shù)。例如,圖形用戶(hù)界面允許用戶(hù)定制存儲(chǔ)器的時(shí)序參數(shù),并用新的時(shí)序值重新生成存儲(chǔ)器控制器。除了DDR3存儲(chǔ)器控制器IP核之外,還提供仿真模型和測(cè)試平臺(tái),這樣設(shè)計(jì)人員可以在將它按裝到電路板上之前,對(duì)設(shè)計(jì)進(jìn)行測(cè)試。

LatticeECP3 DDR3存儲(chǔ)器控制器已經(jīng)用DDR3存儲(chǔ)器元件和DIMM做了充分的驗(yàn)證。萊迪思還提供了多種硬件評(píng)估板,客戶(hù)可用于檢查L(zhǎng)atticeECP3 DDR3存儲(chǔ)器控制器的操作,接口至任何DIMM的 DDR3元件。LatticeECP3系列是業(yè)界唯一支持DDR3存儲(chǔ)器接口的中檔FPGA,從而針對(duì)下一代的系統(tǒng)設(shè)計(jì),為設(shè)計(jì)人員提供了低成本,低功耗的解決方案。

結(jié)論

系統(tǒng)帶寬的需求繼續(xù)以指數(shù)形式增長(zhǎng)。由于DDR3 SDRAM的價(jià)格下降了,DDR3 SDRAM芯片將更廣泛地用于網(wǎng)絡(luò)應(yīng)用。這些增加系統(tǒng)帶寬的要求正在推動(dòng)著存儲(chǔ)器的接口速度增加,同時(shí)繼續(xù)使成本降低。用中檔的FPGA促進(jìn)穩(wěn)定的高速存儲(chǔ)器接口設(shè)計(jì)是LatticeECP3系列FPGA的主要目標(biāo)。針對(duì)下一代存儲(chǔ)器控制器的需要,ECP3的專(zhuān)用、靈活的DDR功能意味著現(xiàn)在設(shè)計(jì)人員有了一個(gè)節(jié)約成本的解決方案。LatticeECP3 DDR3基元與萊迪思的DDR3存儲(chǔ)器控制器IP核的結(jié)合大大降低了DDR3存儲(chǔ)器接口的復(fù)雜性,針對(duì)用DDR3實(shí)現(xiàn)下一代系統(tǒng)設(shè)計(jì),促進(jìn)更快地將產(chǎn)品推向市場(chǎng)。