Design Calculations for Robust I2C Communications

■ Microchip Technology Inc.存儲器產(chǎn)品部資深應(yīng)用工程師 Chris Parris和Jonathan Dillon

許多系統(tǒng)需要可靠的非易失性存儲,對于這些系統(tǒng),可選擇EEPROM存儲器技術(shù)。EEPROM技術(shù)具有穩(wěn)定可靠的架構(gòu),供應(yīng)商較多,并且經(jīng)過了多年的改進(jìn)。EEPROM器件可用于各種工業(yè)標(biāo)準(zhǔn)串行總線,包括I2C™、SPI、Microwire和UNI/O®總線。其中,I2C總線在單片機(jī)和其他芯片組中具有廣泛的硬件支持,并且信號傳遞方式簡單,可采用極小的硅片有效實(shí)現(xiàn),因此占據(jù)了非易失性存儲器市場約70%的份額。但是,I2C總線拓?fù)湟蕾囉谧柚岛线m的上拉電阻才能實(shí)現(xiàn)穩(wěn)定可靠的通信。電阻值選擇錯(cuò)誤不僅會造成電能浪費(fèi),還可能導(dǎo)致總線狀態(tài)和傳輸過程由于噪聲、溫度變化、工作電壓變化以及器件間的制造差異而出錯(cuò)。

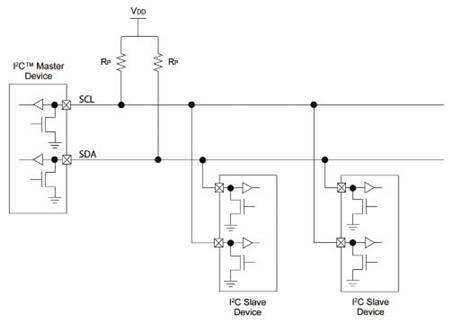

I2C是二線同步總線,使用總線主器件SCL線上產(chǎn)生的信號作為時(shí)鐘。SDA線用于雙向數(shù)據(jù)傳輸。當(dāng)時(shí)鐘處于特定狀態(tài)時(shí)可修改數(shù)據(jù)線,以指示傳輸?shù)拈_始和停止,從而避免使用更多的線。I2C總線以集電極開路輸出為基礎(chǔ),其中,器件可通過接地晶體管拉低線的電平,如圖1所示。這樣便可輕松對總線控制進(jìn)行仲裁,從而在一條數(shù)據(jù)線上實(shí)現(xiàn)雙向通信以及多主器件支持。如圖1所示,每條線都有一個(gè)外部電阻連接至Vdd,該電阻可在釋放總線或總線空閑時(shí)拉高線的電平。

圖1 I2C™總線拓?fù)?br />

確定上拉電阻值(Rp)時(shí)需要考慮三個(gè)因素:

• 電源電壓(Vdd)

• 總線總電容(CBUS)

• 高電平總輸入電流(IIH)

以下面的條件為例計(jì)算理想的上拉電阻值:

• 電源電壓(Vdd)為5V

• 時(shí)鐘頻率為400kHz

• 總線電容為100pF

電源電壓(Vdd)

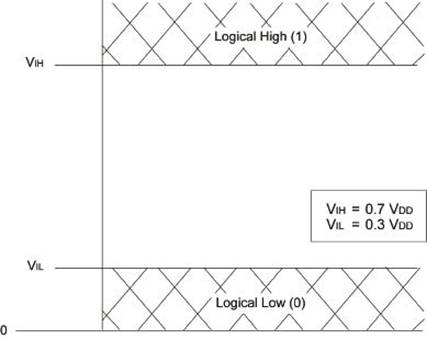

I2C規(guī)范將低于VIL或低于電源電壓30%的電壓定義為邏輯低電平,同樣,將高于VIH或高于電源電壓70%的電壓定義為邏輯高電平,如圖2所示。這兩個(gè)電平之間的電壓屬于不明確的邏輯電平。實(shí)際上,引腳會將該范圍內(nèi)的電平讀為邏輯高電平或邏輯低電平,但在器件間可能不同,因?yàn)闇囟取㈦妷骸⒃肼曉春推渌h(huán)境因素會影響邏輯電平。

圖2 指定為邏輯高電平和邏輯低電平的電壓電平

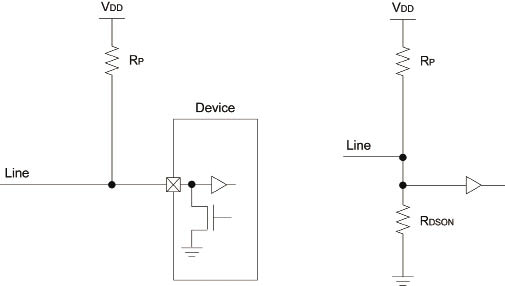

電源電壓限制了可允許總線拉低的最小Rp值。過強(qiáng)的上拉會阻止器件充分拉低線的電平,導(dǎo)致無法確保邏輯低電平能被檢測到。這是由上拉電阻與接地晶體管的導(dǎo)通電阻之間形成的分壓器產(chǎn)生的,如圖3所示。通常不會指定晶體管的導(dǎo)通電阻。相反,會給定使晶體管上的電壓降低于輸出邏輯低電壓電平(VOL)的最大灌電流(IOL)。使用歐姆定律得出公式1。

圖3 集電極開路拓?fù)浜偷刃щ娐?br />

對于Microchip的I2C EEPROM器件,規(guī)定在IOL為3mA時(shí),VOL最大為0.4V,其他制造商的器件的范圍與其相似。

公式1:允許總線電壓拉低的最小上拉電阻。

![]()

![]()

![]()

如果總線上有多個(gè)器件,最小Rp由灌電流最低的器件決定。

總線總電容(CBUS)

在SCL和SDA線上,所有引腳、連接、PCB走線和導(dǎo)線都會引入電容。這些電容結(jié)合在一起稱為總線電容,對于長走線和長連接來說,總線電容可能很大。集電極開路拓?fù)湫枰獠侩娮璨拍茉诳偩€釋放時(shí)拉高線的電平。上拉電阻(與總線電容耦合)具有一個(gè)RC時(shí)間常數(shù),該常數(shù)限制了上升時(shí)間。隨著時(shí)鐘頻率的增加,該常數(shù)愈發(fā)重要,因?yàn)樾枰俚臅r(shí)間升高線的電平。如果所選電阻值過高,線的電平在下一次拉低之前可能無法上升到邏輯高電平。對于一條總線上具有多個(gè)器件的設(shè)計(jì)(通常具有較大的總線電容)來說,這是重要的考慮因素。

總線電容可通過PCB走線長度和引腳分布電容計(jì)算,也可以使用電容探頭或智能鑷子量表進(jìn)行測量。如果不能準(zhǔn)確計(jì)算或測量總線電容,應(yīng)高估最壞情況讀數(shù)以提供安全的最大電阻值。

公式2是用于確定充電電容負(fù)載兩端電壓(與時(shí)間成函數(shù)關(guān)系)的一般公式。這可以計(jì)算在特定上拉電阻和總線電容下,總線電壓上升到特定值所需的時(shí)間。

公式2:通過電阻對電容進(jìn)行充電的一般公式。

![]() 重新排列

重新排列![]()

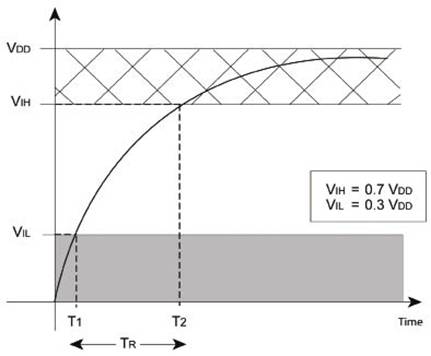

之后,我們可計(jì)算電壓上升至VIL的時(shí)間(T1)、上升至VIH的時(shí)間(T2)以及精確計(jì)算這兩個(gè)電平之間的時(shí)間(TR),如圖4所示。由于VIL和VIH都是由Vdd產(chǎn)生的,因此該公式與電源電壓無關(guān),因?yàn)閂dd項(xiàng)已抵消。

圖4 邏輯低電平轉(zhuǎn)換為邏輯高電平的充電時(shí)間

求解![]()

求解![]()

![]()

各種工作電壓的最大上升時(shí)間由I2C標(biāo)準(zhǔn)指定,并通過上拉電阻確定。根據(jù)該時(shí)間和總線電容,我們可以計(jì)算允許的最大上拉電阻(Rp)。當(dāng)電壓為5V,時(shí)鐘頻率為400kHz時(shí),給定總線電容CBUS為100pF,則規(guī)定的最大上升時(shí)間(TR)為300ns。

公式3:符合I2C上升時(shí)間標(biāo)準(zhǔn)的最小上拉電阻。

![]()

![]()

![]()

![]()

![]()

![]()

高電平總輸入電流(IIH)

即使沒有器件拉低線的電平,線仍處于邏輯高電平時(shí),電流仍會繼續(xù)流過上拉電阻。該電流由總線上器件的數(shù)字輸入的泄漏產(chǎn)生,也可能是質(zhì)量較差的PCB材料以及焊接殘留物所導(dǎo)致。其中一些因素是無法預(yù)見的,但采用高質(zhì)量材料和良好的制造工藝時(shí),輸入引腳泄漏是主要原因。

根據(jù)圖2,沒有器件拉低總線電平時(shí),線的電平需要高于VIH才能被視為邏輯高電平。泄漏電流會限制Rp的最大值,這樣其兩端的電壓降不會阻止線的電平被拉高至VIH以上。對于VIH規(guī)范,還應(yīng)謹(jǐn)慎留出一些保護(hù)裕量,以防止噪聲尖峰將電壓拉低至VIH電平以下。要在高噪聲環(huán)境下穩(wěn)定工作,I2C規(guī)范建議采用0.2 Vdd作為高出VIH的適當(dāng)裕量。

公式4:邏輯高輸入電平上的額外裕量。

![]()

![]()

![]()

通常會在器件的數(shù)據(jù)手冊中給出數(shù)字輸入的泄漏電流,對于Microchip的I2C EEPROM器件,最大輸入泄漏電流(IlIEE)為1µA。組成系統(tǒng)的最少元件是單片機(jī)I2C主器件和I2C從器件。對于本例,采用一個(gè)輸入泄漏電流(IlIMCU)為1µA的單片機(jī)和四個(gè)I2C EEPROM器件,允許100%裕量,IIH為10µA。

公式5:已定義總線的引腳泄漏產(chǎn)生的泄漏電流。

![]()

![]()

![]()

應(yīng)用歐姆定律,我們可以確定符合這些規(guī)范的Rp最大值。

公式6:確保邏輯高電平的最小上拉電阻值。

![]()

![]()

![]()

![]()

![]()

![]()

電阻值計(jì)算

通過計(jì)算電源電壓、總線電容和泄漏電流,我們可以得出RP值的范圍。

![]()

![]()

![]()

![]()

![]()

![]()

可以忽略由泄漏電流產(chǎn)生的 50KΩ(最大值),因?yàn)榭偩€電容起主導(dǎo)作用。因此,可接受的電阻值的范圍為:

![]()

![]()

設(shè)計(jì)人員應(yīng)選擇范圍中間附近的值,以盡可能提供較大的保護(hù)帶。對于本例,2.2KΩ的上拉電阻較為理想。

總線速度與功耗

當(dāng)提高總線速度或存在較大總線電容時(shí),必須減小上拉電阻。阻值較低的電阻會導(dǎo)致電流消耗增加,因?yàn)榭偩€上的每個(gè)邏輯低電平都會產(chǎn)生對地通路,從而對功耗造成負(fù)面影響。快速完成任務(wù)并使系統(tǒng)恢復(fù)到低功耗空閑狀態(tài),與較高總線速度要求所產(chǎn)生的額外電流消耗存在矛盾,總線速度可成為兩者之間的權(quán)衡因素。對于功耗預(yù)算非常低的應(yīng)用,SPI可能是更合適的總線協(xié)議,因?yàn)槠涫褂抿?qū)動線路,而不是集電極開路。