基于ASIC設計的手工綜合研究

摘要: 詳細介紹手工綜合RTL級代碼的理論依據和實用方法,重點介紹時序邏輯綜合的實現(xiàn)方法,將時序邏輯綜合的實現(xiàn)方法歸納出各種描述的一般特征,將用戶多種多樣的描述歸整為五種形式,避免了綜合過程中的盲目性,使得整個綜合過程有據可依,從而提高綜合的效率和準確性,并對手工綜合進行深入的研究。

Abstract:

Key words :

隨著專用集成電路(Application Specific Integrat-ed Circuit)設計的迅速發(fā)展,將寄存器傳輸級(RTL)描述的手工綜合成門級網表,是IC前端設計中的關鍵技術。在當前IC設計中,通常在行為級功能驗證后,采用軟件進行自動綜合的方式。這種方式雖然縮短了ASIC設計的周期,但是利用軟件綜合的門級電路存在很大的冗余,從而影響到整個芯片的版圖面積和延時。如果采用手工綜合,則會得到最簡的電路結構和最少的線路延時。在總體上,手工邏輯綜合可分為時序邏輯綜合和組合邏輯綜合。

在此,以成功開發(fā)的無線發(fā)碼遙控編碼芯片為實例,詳細介紹手工綜合RTL級代碼的理論依據和實用方法,重點介紹時序邏輯綜合的實現(xiàn)方法,將時序邏輯綜合的實現(xiàn)方法歸納出各種描述的一般特征,將用戶多種多樣的描述歸整為五種形式,避免了綜合過程中的盲目性,使得整個綜合過程有據可依,從而提高綜合的效率和準確性,并對手工綜合進行深入的研究。

1 組合邏輯綜合

組合邏輯綜合的功能是對組合邏輯函數的描述形式進行一系列轉換和優(yōu)化,求取實現(xiàn)該邏輯函數性能最佳的組合邏輯結構形式,并生成與邏輯功能描述相等價的優(yōu)化的邏輯級結構描述。由于行為級描述或寄存器傳輸級描述經轉換后所得到的邏輯級的邏輯函數表示通常都是非優(yōu)化的表示,因此就需要使用邏輯優(yōu)化工具對其進行綜合和優(yōu)化。

組合邏輯綜合的目標通常有:其一是為了在滿足延遲的約束下將面積最小化;其二是為了提高電路的可測試性。

組合邏輯電路設計是數字電路設計的基礎。相對時序邏輯電路而言其綜合過程要簡單,可參考上面的手工綜合步驟,在這里設計了兩個電路對ASIC的手工綜合進行具體研究。

1.1 單增量加法器(4位)

所謂單增量加法器,就是在二進制計算中,行使代碼換算的任務,即二進制計算中若輸出有N值存在,接下來的數值就是N+1,為了把輸出值從N變?yōu)镹+1就必須做一個電路。若其Verilog HDL描述語言為:

counter_disp<=counter_disp+4'd1;

則綜合步驟為:

(1)列出真值表(略);

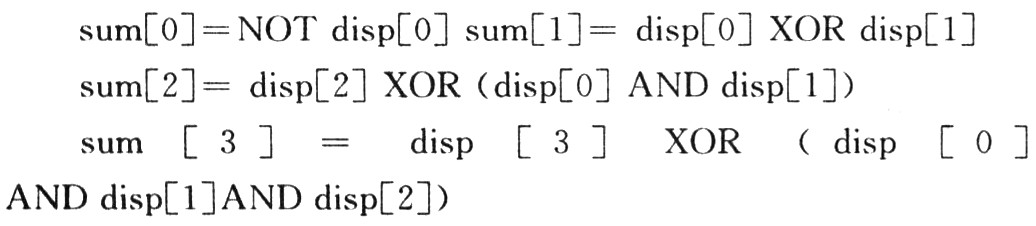

(2)從真值表可以得出其邏輯表達式為:

(3)綜合后的電路圖如圖1所示。

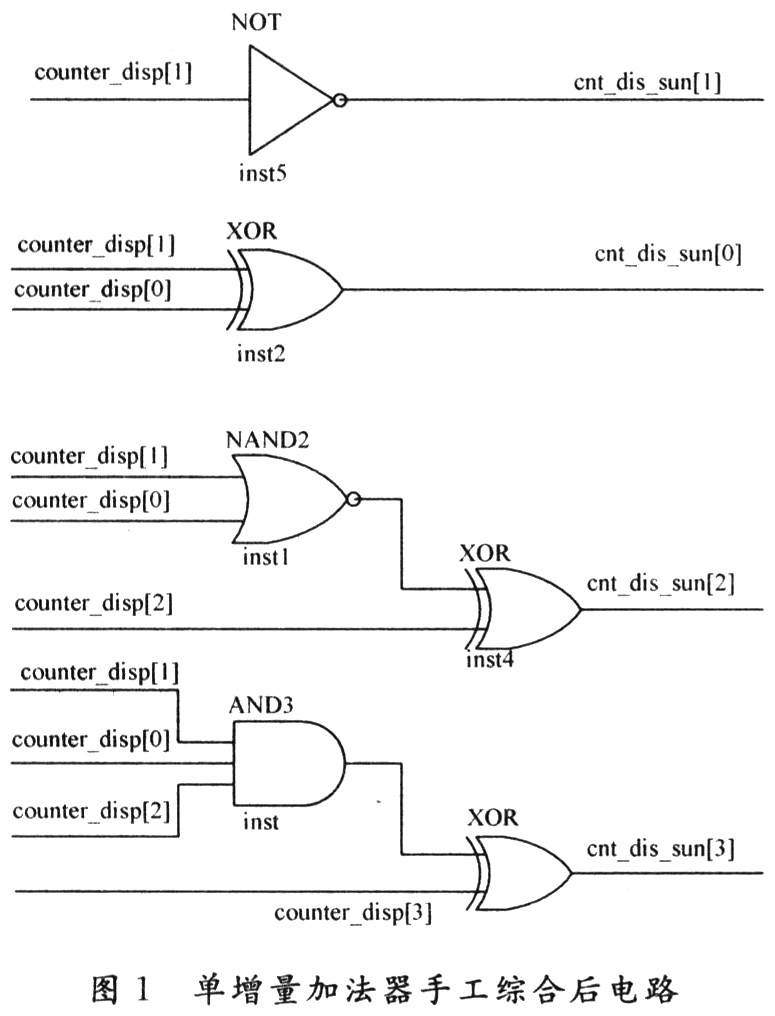

1.2 數值比較器(4位)

完成A<B的檢測功能,其中:A=counter disp[3:0],B=number light[3:0],其原理為:兩個4位數的比較是先從A的最高位A3和B的最高位B3進行比較,如果A3<B3,則該位的比較結果作為兩數的比較結果,若最高位A3=B3,則再比較次高位A2和B2,以此類推。

對應的描述語言為:

if(counter disp<number light)

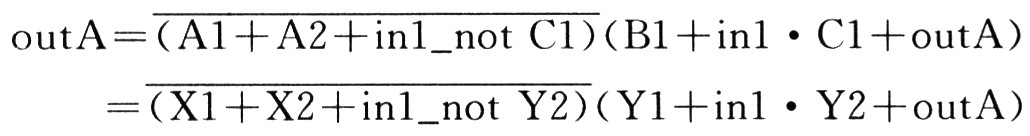

(1)列出真值表(見表1)。其中“X”表示任意值。

(2)從真值表寫出比較結果的邏輯表達式,再通過化簡得到最簡表達式為:

A_small_B=A3n·B3+(B2⊙82)A2n·B2+(A3⊙83)(A2⊙B2)A1n·B1+(A3⊙B3)(A2⊙B2)(A1⊙B1)·A0n·B0

(3)畫出綜合后的電路圖(見圖2)。

2 時序邏輯綜合

時序邏輯綜合的主要研究集中于同步時序電路的設計綜合。異步時序電路由于其設計和控制過程的復雜性,自動綜合十分困難。同步時序電路邏輯綜合研究的內容主要有:同步時序電路的綜合方法(即有限狀態(tài)機的綜合)、時序的優(yōu)化以及時鐘系統(tǒng)的設計優(yōu)化等。有限狀態(tài)機綜合的主要任務是根據給定的邏輯功能,選取觸發(fā)器和鎖存器等時序元件,尋求優(yōu)化的時序狀態(tài)激勵函數。同步時序電路綜合的目標是獲得芯片面積優(yōu)化的高性能電路結構形式,其中包括時序重構和時序邏輯優(yōu)化等方面。時序優(yōu)化與時鐘系統(tǒng)的優(yōu)化通過分析時序電路的數據傳輸行為,設置合理的參數,提高系統(tǒng)的效率,消除時序錯誤,解決時序沖突。優(yōu)化電路,得到最終的門級電路網表。

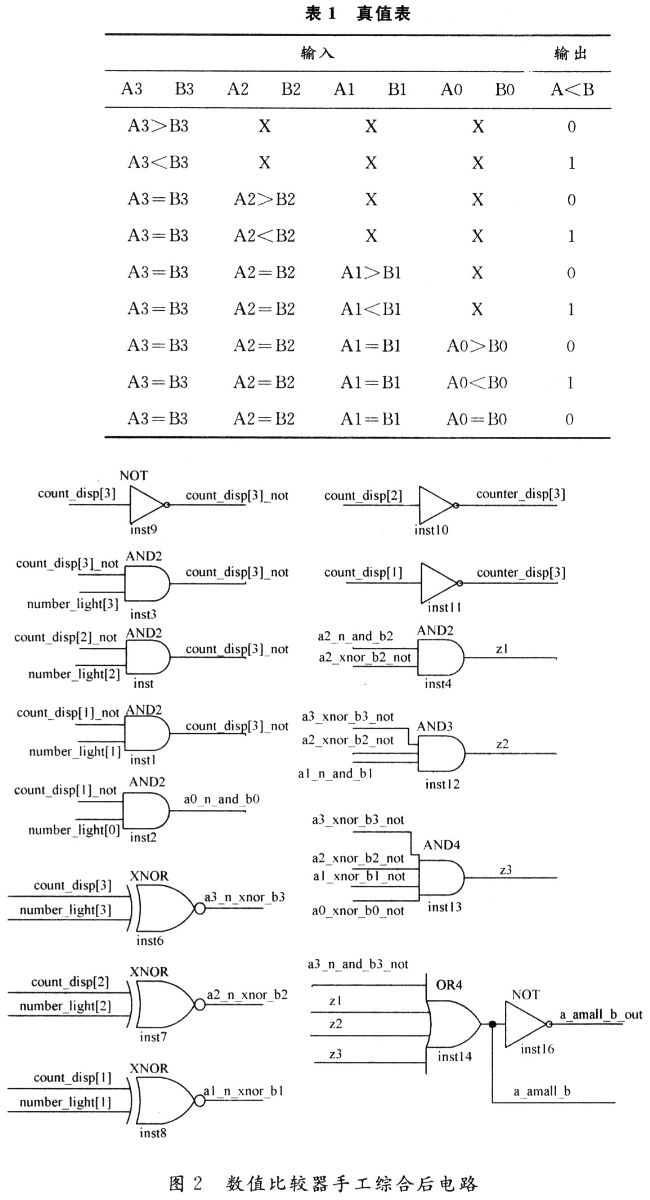

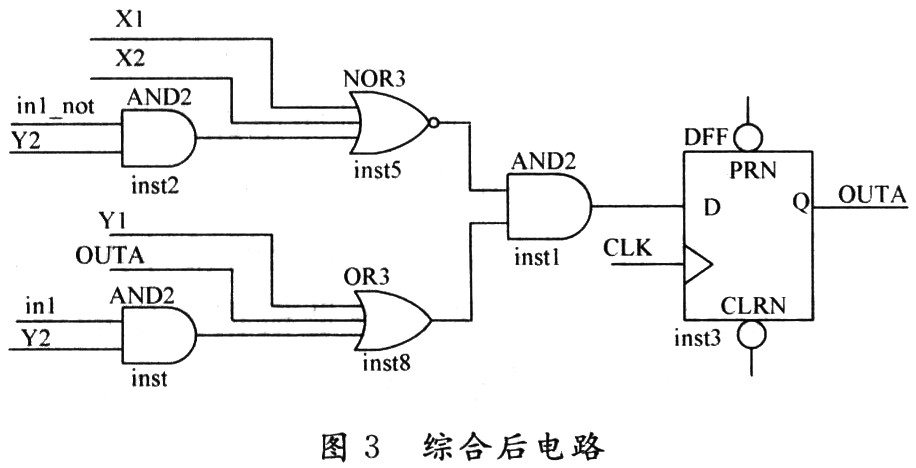

在進行了格式判別,確定采用何種時序元件后,就可以從相應的目標庫中提取相應的元件,組織成符合最終輸出形式的網表格式。在提取元件時應當根據用戶的輸入描述取得最優(yōu)化的結果,當然,這種優(yōu)化問題也可以在得到最終的數據通道之后進行。對于同步/異步復位及上升/下降沿觸發(fā)的問題,在一般的目標庫中,都有各種不同類型的時序邏輯電路元件,同步/異步復位元件為其中之一。同步/異步復位觸發(fā)器的綜合與其他元件的綜合有所不同,綜合時考慮的不僅是某一條賦值語句,而是將用戶的描述作為一個整體來考慮。在提取賦值語句時,同時分析相互有關聯(lián)的語句以及這些語句的相關條件,根據上下文語義得出最終的結論。下面針對上述理論用一實例來說明:在采用上面的綜合步驟預處理和綜合實現(xiàn)算法后,得到輸出信號outA的賦值情況如下:

條件X1成立時outA≤0;條件X2成立時outA≤0;條件Y1成立時outA≤1;條件Y2成立時OutA≤in1;其他條件下outA保持。

其處理過程如下:

(1)將所有使輸出信號為0的條件標識為A1,A2等A類(A1=X1,A2=X2);

(2)將所有使輸出信號為1的條件標識為B1,B2等B類(B1=Y1);

(3)將所有使輸出信號為某個輸入信號或中間信號值的條件標識為C1,C2等C類(C1=Y2);

(4)寫出其邏輯表達式:

(5)將目標信號的邏輯表達式進行畫簡(這里設定已為最簡式);

(6)畫出對應的邏輯電路圖(見圖3):(其中in1_not表示為in1的非,其余類同。)

具有數據通道的有限狀態(tài)機是描述數字系統(tǒng)的最常用的模型。有限狀態(tài)機分為兩個部分:數據通道部分和控制部件部分。數據通道部分包括數據的處理部件、存儲部件、傳輸部件及其互連。控制部分主要完成數據通道的時序控制,以及根據當前狀態(tài)、外部控制輸入和數據通道內部狀態(tài)產生外部控制輸出和數據通道控制信號等。邏輯綜合接受算法級行為描述,通過將其編譯轉換成為內部表示形式,然后經過操作調度和硬件資源分配等處理過程,最終產生表示數據通道的寄存器傳輸級網表,并根據調度的需要提取控制信息產生控制部件的行為描述(即有限狀態(tài)機的描述,一般為狀態(tài)轉換表/圖)。控制流綜合對行為描述的有限狀態(tài)機進行分解、化簡、分配等處理,選取時序元件,導出狀態(tài)轉換函數和控制輸出函數。

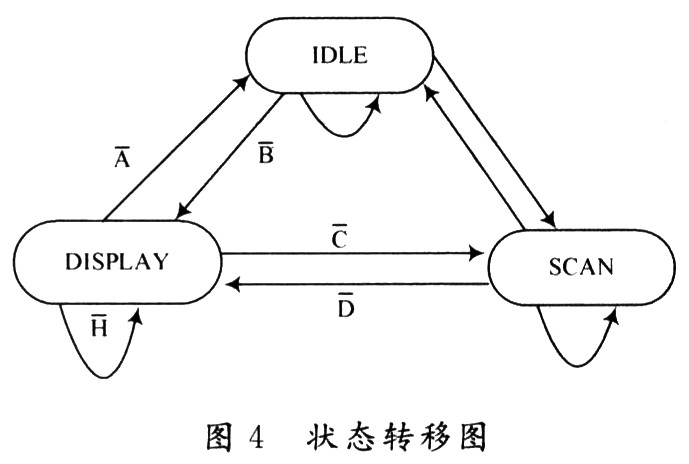

下面以一個實例來介紹控制部分的邏輯綜合過程和方法。按照前面的步驟,分析Verilog HDL代碼,已得出該控制流部分的狀態(tài)轉換圖(見圖4),在這里只列出用符號代替的狀態(tài)轉移條件,未寫出各輸出端信號。

這是IED驅動控制芯片核心模塊(顯示和鍵掃控制模塊)的狀態(tài)轉換圖,下面以DISPLAY狀態(tài)為目標求其狀態(tài)轉移電路圖,如圖5所示。

(1)根據狀態(tài)轉移圖列出與DISPLAY狀態(tài)相關的狀態(tài)轉換條件:

當A=1,DISPLAY=1 D="1時",DISPLAY=1;

當B=1,DISPLAY=0 C="1時",DISPLAY=0

(2)推斷出DISPLAY狀態(tài)保持的條件,設為E:E=(B&&DISPLAY)||(C&&DISPLAY)+H=BC&&DISPLAY+H=BC&&DISPLAY

(3)化簡并得出DISPLAY的邏輯表達式:

DISPLAY≤A+D+E

(4)畫出其邏輯電路圖(狀態(tài)機采用獨熱碼編碼方式)。

3 結 語

在此歸納出一套手工邏輯綜合的方法和綜合步驟,該方法適用于中小規(guī)模和超大規(guī)模中的核心電路部分的電路綜合。同時手工綜合后的效果與自動綜合軟件相比,其電路可靠且使用的門電路規(guī)模減少,功耗降低,延時達到最小。

此內容為AET網站原創(chuàng),未經授權禁止轉載。