文獻(xiàn)標(biāo)識碼: A

文章編號: 0258-7998(2014)08-0017-03

PowerPC具有外設(shè)豐富、處理能力強以及便于移植Linux等操作系統(tǒng)的特點,而現(xiàn)場可編輯邏輯門陣列FPGA具有處理能力強、在線可編程等特點。因此,在復(fù)雜工業(yè)控制、路由器等諸多領(lǐng)域,采用PowerPC+FPGA的架構(gòu)得到了廣泛的使用。眾所周知,F(xiàn)PGA多采用靜態(tài)隨機存取存儲器SRAM(Static Random-Access Memory)工藝,掉電后配置數(shù)據(jù)將丟失。因此,系統(tǒng)每次上電后都必須進(jìn)行數(shù)據(jù)配置。此外,隨著FPGA規(guī)模越來越大,配置數(shù)據(jù)已達(dá)到幾十甚至上百兆比特,常用的串行配置邊界掃描(JTAG)等方式在很多場合下已無法滿足需求。若設(shè)計中需要對多片F(xiàn)PGA進(jìn)行配置,則更為復(fù)雜,耗費時間更長。目前,主流PowerPC具有豐富的通用輸入/輸出口GPIO(General Purpose I/O),自帶位寬達(dá)32 bit的本地總線(Local Bus),且在其上移植Linux等操作系統(tǒng)方便快捷。因此,可以利用PowerPC本地總線對多片F(xiàn)PGA進(jìn)行快速并行配置。

1 FPGA配置方式

1.1 常用的配置方式及特點

目前主流的FPGA廠家有Xilinx、Altera等公司。雖然不同廠家、不同系列的FPGA芯片配置方式或多或少存在一些差異,但是大體來說配置方式包括JTAG模式、主動模式以及被動模式[1-2]。不同模式之間通過模式選擇控制引腳進(jìn)行選擇,具體設(shè)置方式由相應(yīng)的芯片資料給出。

JTAG模式使用最方便,使用下載器就可以很方便地將計算機生成的配置數(shù)據(jù)下載到FPGA中。但是這種模式?jīng)]有存儲芯片,掉電后需重新通過計算機下載,所以這種配置方式多用于調(diào)試階段;主動模式下FPGA作為控制器,產(chǎn)生配置時鐘和控制時序,從配置器件等外部設(shè)備中讀取配置數(shù)據(jù),進(jìn)而將數(shù)據(jù)下載至FPGA。根據(jù)數(shù)據(jù)采用的是串行還是并行模式,又分為主動串行模式和主動并行模式。被動模式是由外部配置器件產(chǎn)生時鐘和控制時序控制整個配置過程,F(xiàn)PGA只是被動地接收配置數(shù)據(jù)。同樣根據(jù)數(shù)據(jù)采用的是串行還是并行模式(對應(yīng)Xilinx FPGA的SelectMAP模式),又分為被動串行和被動并行模式[3-4]。當(dāng)然,根據(jù)數(shù)據(jù)是同步還是異步的,還可以進(jìn)一步細(xì)分。

串行(主串或從串)模式具有配置信號少、配置電路簡單等優(yōu)點。但是FPGA 在配置時鐘的1個上升沿只能接收1 位配置數(shù)據(jù),顯然該配置方式速度較慢;并行模式配置信號線比較多,但是配置速度較快,在高密度的FPGA系統(tǒng)中,更適合采用并行模式。并行模式除了采用專用配置芯片外,還可以采用微處理器或者CPLD控制Flash等存儲器對FPGA進(jìn)行配置。由于主流PowerPC具有豐富的GPIO口和32位總線,若運行Linux系統(tǒng),則可以進(jìn)一步擴展CF卡或者SD卡,將配置文件存放在CF卡或者SD卡中,而不用Flash芯片。在精簡系統(tǒng)設(shè)計的同時,使得程序升級維護(hù)更方便,在工程實踐中更具有實際意義。

1.2 FPGA配置文件

以Xilinx FPGA芯片為例,其配置文件可由集成開發(fā)環(huán)境ISE生成。常用的配置文件格式(后綴名)包括:.bit、.rbt、.bin、.mcs以及.hex等格式。其中.bin和.bit文件都是直接向FPGA配置的文件。.bit文件除包含有真正的配置數(shù)據(jù)外,還在文件開頭添加了頭部冗余信息,包含當(dāng)前ISE工程的名字、器件型號、編譯時間等信息,主要用于JTAG下載;.bin文件只包含了原始配置數(shù)據(jù)的二進(jìn)制文件,實質(zhì)上就是去除了頭部冗余信息的.bit文件。.bin文件也由文件頭和配置數(shù)據(jù)組成,其中文件頭主要包括位寬檢測和同步字等,第二部分才是真正寫入FPGA的配置文件,這種格式常用于利用微處理器對FPGA進(jìn)行并行下載。.rbt格式為.bit文件的ASCII格式;.mcs文件包括地址和校驗信息,主要用于專用配置芯片進(jìn)行程序燒寫;.hex文件只包含F(xiàn)PGA的配置數(shù)據(jù),也是給用戶使用的。顯然,利用PowerPC對FPGA進(jìn)行配置時要選擇.bin格式文件。本文采用被動SelectMAP模式對Xinlix Virtex-6 FPGA進(jìn)行配置。

2 硬件設(shè)計與實現(xiàn)

2.1 并行配置的相關(guān)時序

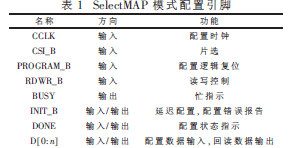

Xilinx SelectMAP模式實質(zhì)上就是并行配置模式,它以字節(jié)為單位將配置數(shù)據(jù)寫入FPGA。在從SelectMAP模式下,外部數(shù)據(jù)源向FPGA提供時鐘(CCLK)、編程(PROGRAM_B)、片選(CSI_B)、讀/寫(RDWR_B)、初始化(INIT_B)以及數(shù)據(jù)信號D[0:n](在8 bit、16 bit、32 bit模式下,n分別對應(yīng)7、

15、31)。表 1給出了SelectMAP模式下的配置引腳功能。其中信號方向是相對于FPGA而言的。

各控制信號的具體含義如下[5]:

(1)PROGRAM_B:編程復(fù)位信號。在上電過程中為邊沿敏感,上電后為低電平有效。該信號拉低完成芯片的復(fù)位,低電平保持時間為0.5 ?滋s乘以配置文件的幀數(shù)。對Virtex-6芯片,大概幾十毫秒(經(jīng)實測在1 ms以內(nèi))。復(fù)位完成后,內(nèi)部INIT_B抬高。

(2)INIT_B:初始化信號。為雙向信號,在重啟或者編程初始化(PROGRAM_B=0)過程中,用來指示FPGA是否已經(jīng)完成配置初始化。作為輸入信號,將INIT_B拉低來推遲對FPGA的配置。一般情況下,只需在PROGRAM_B=0后等待一定時間即可完成初始化。為了簡化設(shè)計,在本設(shè)計中INIT_B只用于輸入。

(3)CSI_B:片選信號。低電平有效,CSI_B=0表示總線允許。

(4)RDWR_B:讀寫控制信號。RDWR_B=0表示總線寫入,RDWR_B=10表示總線讀出。需要注意的是,拉低RDWR_B信號之前,必須確認(rèn)CSI_B=0,否則可能會導(dǎo)致數(shù)據(jù)丟失。

(5)BUSY:握手信號。當(dāng)配置時鐘頻率超過50 MHz時,利用本信號控制寫入或者讀出速度。

(6)DONE:配置狀態(tài)指示信號。數(shù)據(jù)正確配置后,DONE=1。

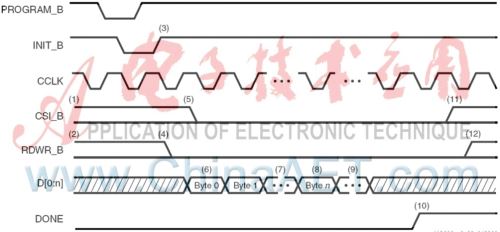

圖 1給出了連續(xù)并行配置的時序圖。

圖1 SelectMAP 模式連續(xù)配置時序圖

2.2 基本思想與硬件設(shè)計原理

由表1和圖1可以看出,F(xiàn)PGA在CSI_B、PROGRAM_B、RDWR_B以及INIT_B的控制下,在時鐘CCLK的上升沿時刻將配置數(shù)據(jù)寫入FPGA。以上4個控制信號可以利用PowerPC的GPIO口生成,雖然CCLK也可以用GPIO生成,但是由于GPIO口輸出的數(shù)據(jù)和總線數(shù)據(jù)都要經(jīng)過鎖存、電平轉(zhuǎn)換等,在高速設(shè)計中,可能會產(chǎn)生意想不到的結(jié)果,或者為了保證時序的正確性而犧牲效率。考慮到PowerPC總線進(jìn)行寫操作時,其對應(yīng)的片選信號LCS以及RDWR信號都為低電平,而進(jìn)行其他操作時,RDWR為高電平。此外,通過對PowerPC的總線控制寄存器進(jìn)行設(shè)置,可以使LCS信號滯后于RDWR拉高。因此可以將LCS與RDWR進(jìn)行“或操作”產(chǎn)生配置時鐘CCLK。寫命令發(fā)出后,由于LCS滯后于RDWR信號,可以保證數(shù)據(jù)能夠被正確寫入FPGA。

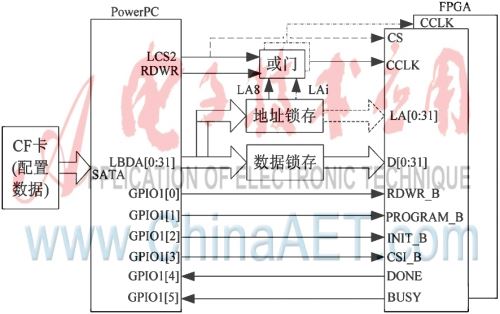

基于以上時序分析的結(jié)果,設(shè)計了圖2所示的原理框圖。通過SATA接口相連的CF卡用來存放配置數(shù)據(jù),當(dāng)然也可以用SD卡。CF卡或者SD卡可以很方便地從卡座上拔下,使得程序維護(hù)升級非常方便,甚至非專業(yè)人員都能完成程序的升級。在調(diào)試過程中,數(shù)據(jù)可以直接存放在調(diào)試計算機中,利用NFS協(xié)議調(diào)試,方便快捷。為了能夠區(qū)分多片F(xiàn)PGA,可以將不同的地址線與LCS、RDWR一起進(jìn)行或運算,實現(xiàn)片選。地址線為高電平時,時鐘始終為高電平,對應(yīng)FPGA芯片不被選中(芯片較多的情況下,也可采用譯碼器來實現(xiàn)片選)。向相應(yīng)的地址寫入數(shù)據(jù),就實現(xiàn)了片選。需要注意的是,在FPGA配置過程中,無需對地址進(jìn)行操作,地址僅僅是作為片選信號使用。此外,圖中的數(shù)據(jù)總線不僅在配置期間使用,在訪問FPGA時也要使用。為了更好地利用同一條總線實現(xiàn)對FPGA的配置和訪問,LCS2同時連接至多片F(xiàn)PGA的片選,在配置期間與其他信號一起產(chǎn)生配置時鐘,在訪問期間起到片選的作用。圖中的虛線表示在PowerPC訪問FPGA時采用的信號線,在配置期間不使用。

圖2 PowerPC并行配置FPGA原理框圖

3 軟件設(shè)計與實現(xiàn)

3.1 軟件設(shè)計要點

針對PowerPC、Linux操作系統(tǒng)以及FPGA的特點,在軟件設(shè)計過程中,應(yīng)注意以下幾點:

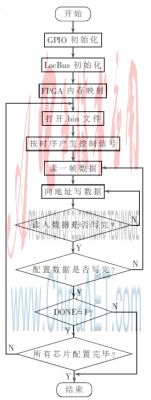

(1)利用內(nèi)存映射函數(shù)替代驅(qū)動程序設(shè)計。通常情況下,Linux內(nèi)核通過驅(qū)動程序來實現(xiàn)對外部設(shè)備的輸入/輸出操作。利用PowerPC對FPGA進(jìn)行并行配置,當(dāng)然也可以利用驅(qū)動程序來實現(xiàn)。不過由于驅(qū)動程序編寫比較繁瑣,使用起來也不夠靈活,所以可以利用Linux內(nèi)存映射函數(shù)mmap[6],將包括系統(tǒng)配置寄存器等相關(guān)寄存器在內(nèi)的一塊內(nèi)核空間映射到用戶空間的一段內(nèi)存區(qū)域。映射成功后,用戶對這段內(nèi)存區(qū)域的操作可以直接反映到內(nèi)核空間。具體來說,經(jīng)過映射后,用戶可以通過對相應(yīng)的內(nèi)存地址進(jìn)行操作,實現(xiàn)對系統(tǒng)配置寄存器、GPIO寄存器、本地總線控制器寄存器等的配置和訪問,而無需利用驅(qū)動程序,使得配置程序得以簡化。

(2)妥善處理字節(jié)序和比特序問題。在FPGA配置過程中,因涉及到眾多軟硬件,要特別注意接口過程中的字節(jié)序和比特序問題。以MPC8377 PowerPC為例,其為大端、最低有效位LSB(Least Significant Bit)在前模式,而Virtex-6系列FPGA為小端、LSB在前模式。大端模式是在寫內(nèi)存時在內(nèi)存低地址處存放數(shù)據(jù)的高位字節(jié),高地址處存放低位字節(jié);而讀內(nèi)存時,將內(nèi)存的高位地址視為目標(biāo)數(shù)據(jù)的低字節(jié),將低位地址視為高字節(jié)。小端模式正好相反。ISE生成的.bin文件與FPGA一致,也為小端模式。因此通過PowerPC將數(shù)據(jù)下載至FPGA時必須要進(jìn)行大小端轉(zhuǎn)換,即字節(jié)序轉(zhuǎn)換。因PowerPC和FPGA均為LSB在前模式,因此無需作比特序的轉(zhuǎn)換。也就是說,利用ISE生成.bin文件時不需做bit swap處理。

(3)正確配置寄存器。使用本地總線首先必須要正確配置本地總線的本地訪問窗口基址寄存器、本地訪問窗口屬性寄存器、本地總線控制基寄存器和可選寄存器。若片選信號為LCS2,則這4個寄存器分別為:LBLAWBAR2、LBLAWAR2、BR2和OR2。其中,LBLAWBAR2就是本地訪問窗口的基址,可以直接設(shè)置為LCS2對應(yīng)的地址;LBLAWAR2是本地訪問窗口屬性寄存器,這個寄存器主要定義了允許訪問窗口的大小,主要由需要配置的FPGA片選對應(yīng)的地址空間決定;BR2主要是對總線的位寬進(jìn)行設(shè)置,位寬有8 bit、16 bit以及32 bit 3種選擇;OR2也比較重要,決定了外部存儲器寫訪問期間LCS2 和LWE 何時無效。舉例來說,在bit21 22=00的情況下,對bit20置位,可使LWE提前總線1/4個周期。這樣可以確保在LCS2拉高前,數(shù)據(jù)能夠被正確寫入FPGA。當(dāng)然,也可以對bit21 22通過設(shè)置其他的值,實現(xiàn)LCS2的不同延時。

3.2 軟件流程

按照上述思想,給出了軟件流程如圖3所示。

4 調(diào)試要點

(1)注意大小端問題。利用MPC8377對FPGA進(jìn)行配置時,總線寬度可以是8 bit、16 bit、32 bit之一。8 bit模式下不用關(guān)心字節(jié)序,16 bit和32 bit必須進(jìn)行大小端轉(zhuǎn)換。關(guān)注同步字即可確定字節(jié)序和比特序。在實際的調(diào)試過程中,應(yīng)抓住一點,對于FPGA,其引腳上的同步字為D[31..0]=0x5599AA66。若FPGA和PowerPC的引腳是順序?qū)?yīng)的(即D0對D0,D31對D31),那么對于PowerPC,需要在總線上傳輸?shù)臄?shù)據(jù)應(yīng)該是0x665599AA。所以需要將.bin配置文件中的同步字0xAA995566進(jìn)行大小端轉(zhuǎn)換后變?yōu)?x665599AA,然后通過PowerPC傳送到FPGA對應(yīng)的引腳上即可。

(2)善于利用JTAG口。FPGA的JTAG既可以用來下載數(shù)據(jù),也可以借助它來查看FPGA配置狀態(tài)寄存器的值,其中包括總線寬度、配置模式等參數(shù)。在利用PowerPC對FPGA進(jìn)行配置的過程中,關(guān)注配置寄存器的相關(guān)狀態(tài),可以得到對應(yīng)的信息。比如配置模式在INIT信號由低變高時被采樣,總線寬度是在檢測到位寬信號后被采樣。若位寬顯示正常,說明配置數(shù)據(jù)已能被正確寫入FPGA;若配置還是錯誤,就應(yīng)該檢查字節(jié)序、配置文件等是否正確。

(3)利用NFS協(xié)議調(diào)試。調(diào)試過程中,可以將程序放在本地計算機中進(jìn)行編譯,通過NFS協(xié)議,PowerPC可以運行存放在主機中的文件。等調(diào)試完畢后,可將應(yīng)用程序、配置文件一并存入外接的CF卡中,以提高調(diào)試效率。

此外,在調(diào)試階段可以將PROGRAM、INIT等信號間隔適當(dāng)拉大,調(diào)整OR寄存器的值,適當(dāng)降低配置速率,等配置成功后,再對相關(guān)值進(jìn)行調(diào)整和優(yōu)化,以提高配置速度。

本文給出了一種利用PowerPC對多片F(xiàn)PGA進(jìn)行并行配置的簡單方法。經(jīng)實測,配置1片Virtex-6 XC6VS-

X475T芯片,若采用JTAG模式,需要48 s,而采用文中給出的并行配置方案,可將配置時間縮短至1 s左右,極大地縮短了配置時間。該方法也同樣適用于Xilinx其他系列的芯片以及Altera系列芯片。

參考文獻(xiàn)

[1] Altera.Device configuration schemes[EB/OL].(2013-10-08) [2014-03-30].http://www.altera.com.cn/support/devices/configuration/schemes/cfg-matrix.html.

[2] Xilinx.Configuration for Virtex-6 FPGA[EB/OL].(2013-08-25)[2014-03-30].http://www.xilinx.com/products/design_resources/config_sol/v6/config_v6.htm.

[3] 葛飛,何輔云,夏玉寶.FPGA被動并行配置控制器的研究與實現(xiàn)[J].合肥工業(yè)大學(xué)學(xué)報(自然科學(xué)版),2008,30(4):39-41.

[4] 趙勇,孟李林,李小龍.Cyclone IV系列FPGA的配置方式及其工程應(yīng)用[J].微型機與應(yīng)用,2013,32(19):25-28.

[5] Xilinx.UG360 Virtex-6 FPGA configuration user guide[EB/OL].(2013-11-27)[2014-03-30].http://www.xilinx.com/support/documentation/user_guides/ug360.pdf.

[6] 韓超,魏治宇,廖文江.嵌入式Linux上的C語言編程實踐[M].北京:電子工業(yè)出版社,2009.

(收稿日期:2014-04-22)