有些應(yīng)用需要對一組模擬電壓的采樣,至少有兩種傳統(tǒng)方法可以滿足這種要求。最常見的辦法是將一個經(jīng)典的模擬累加器與一個采樣保持放大器級聯(lián)。經(jīng)典的模擬累加器是一個運放加上至少三只精密電阻。這些電阻的值應(yīng)盡可能低,以避免影響累加器的帶寬。但這些低值電阻會消耗功率。此外,累加器與采樣保持放大器的結(jié)構(gòu)也帶來了另一種缺點,當兩個輸入電壓幅度相近而極性相反時,就會顯示出這種缺點。此時,即使輸入電壓幅度很高,得到的總和也很低,如果輸入電壓幅度相等則總和為零。對低電壓的采樣通常會使輸出電壓出現(xiàn)相對較大的誤差,因為每個放大器都有一些動態(tài)誤差,如殘留的寄生電荷傳入存儲電容。

還有一種可能方法,即每通道使用一個放大器,用一個經(jīng)典的模擬累加器將它們的輸出匯總。雖然這種結(jié)構(gòu)避免了輸入電壓幅度相似、極性相反會導(dǎo)致高輸出誤差的問題,但累加器的精密電阻仍要消耗功率。

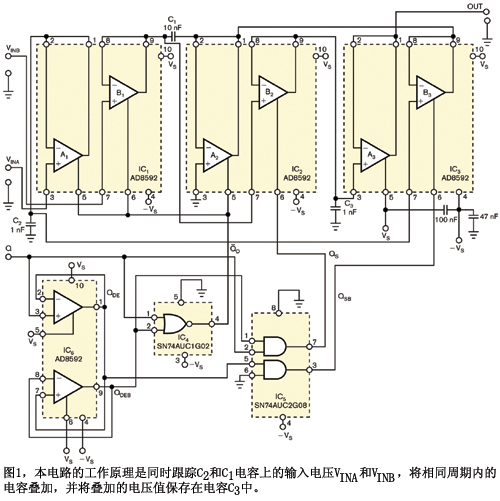

采用圖1中的電路結(jié)構(gòu)就可以避免這些問題,它不使用外接電阻。在穩(wěn)態(tài)下,內(nèi)部跟蹤周期內(nèi),內(nèi)部邏輯信號為高電平有效,將A1、B1與A2組成的跟隨器使能。因此,以地為參考的電容C2充電到VINA電壓。IC2 Pin 2上的電容C1低端通過A2跟隨器的輸出臨時接地,同時其接到IC1 Pin 9的高端充電到VINB電壓。VINA與VINB分別是A和B輸入的輸入電壓。

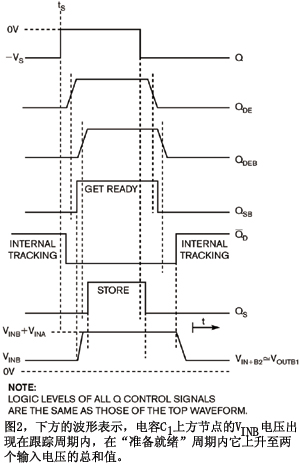

經(jīng)過一個穩(wěn)定期以后,當所有內(nèi)部邏輯控制信號均為低,并且所有受控跟隨器均被禁用,QSB控制邏輯信號為高。因為使能跟隨器B3,C1低端的電勢從0V到VC2(tS) = VINA(tS)。 VC2(tS)是電容C2中存儲的電壓值,然后信號轉(zhuǎn)變到一個無效低電平。C1高端的電勢因此而上升到VC2(tS) + VC1(tS) = VINA(tS) + VINB(tS),如圖2中下方波形所示。該波形是此圖中唯一的模擬波形。采樣命令邏輯信號QS從低至高的有效轉(zhuǎn)換略微滯后于QSB邏輯信號,抑制了輸出電壓上的毛刺。當QS為高時,在IC2 Pin 7上出現(xiàn)的采樣電壓VINA(tS) + VINB(tS)通過使能跟隨器B2接入并存儲在電容C3中,直到下一個采樣指令。跟隨器A3作為一個阻抗變換器。雙運放IC6用作一個分支延遲線,它與一個單或非門和一個雙與門結(jié)合,從單一的外接邏輯控制信號Q中得到時序正確的內(nèi)部邏輯控制信號。