僅使用兩個(gè)轉(zhuǎn)換器形成膠連邏輯,一個(gè)8位微處理器和兩個(gè)12位DAC實(shí)現(xiàn)256級QAM。

本設(shè)計(jì)提出一種有效方法,僅用兩個(gè)反向器,也無需查表,實(shí)現(xiàn)QAM(正交幅度調(diào)制)映射和轉(zhuǎn)換成兩個(gè)余角值。

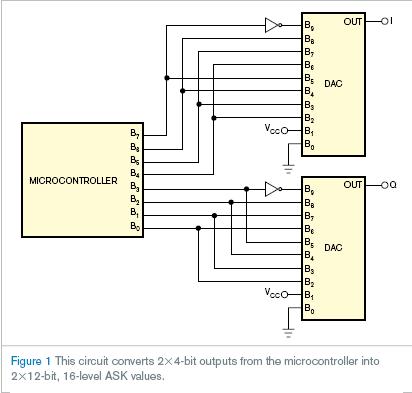

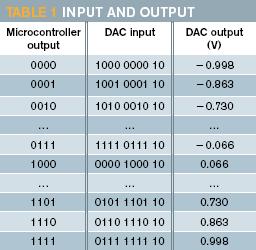

假設(shè)要使用微處理器和兩個(gè)帶并行輸入的10位DAC,創(chuàng)建在兩個(gè)余角符號中的256級QAM信號。因?yàn)閷?56級QAM信號分離成同相成分的16級ASK(幅變調(diào)制)信號和求積成分的16級ASK,對稱的方法是可行的。完全對稱電路實(shí)現(xiàn)16位ASK的映射和轉(zhuǎn)換(圖1)。兩個(gè)換向器是轉(zhuǎn)換所需的唯一膠連邏輯。電路各部分轉(zhuǎn)換微處理器的四個(gè)輸出位為一個(gè)10位雙余角矢量,它直接提供給DAC(表1)。DAC輸入的可能值平均分布。表1的第三列在可選電流到電壓轉(zhuǎn)換后,提供規(guī)格化DAC輸出。

對256級QAM信號,需要8個(gè)輸入位,精確符合大多數(shù)處理器上通用輸入輸出口的寬度。同時(shí)設(shè)定全部8位確保同相和積分信號之間同步。可以容易地為任何QAM模塊和DAC分辨率改變電路。由于電路為全數(shù)字的,可以用反向放大器做輸出緩沖器,并將其嵌入FPGA或CPLD。

英文原文:

Circuit provides low-cost QAM mapping and translation

Using just two inverters for glue logic, an 8-bit microcontroller and two 12-bit DACs enable 256-level QAM.

Pieter Demuytere, Cedric Mélange, Elena Matei, Els De Backer, Johan Bauwelinck, and Jan Vandewege, Ghent University, Department of Information Technology, Ghent, Belgium; Edited by Charles H Small and Fran Granville -- EDN, 9/27/2007

This Design Idea presents an efficient way to do QAM (quadrature-amplitude-modulation) mapping and translation into two’s-complement values with only two inverters and no look-up tables.

Suppose you want to create a 256-level QAM signal using a microcontroller and two 10-bit DACs with a parallel input in two’s-complement notation. Because you can split a 256-level QAM signal into a 16-level ASK (amplitude-shift-keying) signal for the in-phase component and a 16-level ASK for the quadrature component, a symmetrical approach is feasible. The fully symmetrically circuit performs the 16-level ASK mappings and translations (Figure 1). Two inverters are the only glue logic you need for the conversion. Each part of the circuit converts four output bits of the microcontroller into a 10-bit two’s-complement vector, which feeds directly to the DACs (Table 1). The possible DAC-input values are equally distributed. The third column of Table 1 gives the normalized DAC output after an optional current-to-voltage conversion.

For 256-level QAM signals, you need 8 input bits, which exactly fit the width o f a general-purpose-I/O bank on most microcontrollers. Simultaneously setting all 8 bits ensures synchronization between in-phase and quadrature signals. You can easily adapt this circuit for any QAM constellation or DAC resolution. Because this circuit is fully digital, you can also embed it in FPGAs or CPLDs, using the inverters available in the output buffers.