l 引 言

PowerPC是1993年IBM,Apple和Motorola公司(其半導(dǎo)體部門(mén)現(xiàn)在分拆為Freescale公司)聯(lián)盟的共同設(shè)計(jì)的。PowerPC技術(shù)以RISC(精簡(jiǎn)指令集計(jì)算機(jī))為基礎(chǔ),該技術(shù)由IBM的POWER(性能優(yōu)化的增強(qiáng)RISC)體系結(jié)構(gòu)而來(lái)。因PowerPC芯片具有高性能和低功耗的特點(diǎn),主要應(yīng)用在嵌入式系統(tǒng)。MPC7410是新一代G4處理器,通過(guò)加入A1tiVec技術(shù),處理能力達(dá)到4G FLOPS,而1.8V的低電壓操作大大降低了芯片的功耗,提高了系統(tǒng)的穩(wěn)定性。MPC7410內(nèi)部主頻最高為500 MHz,每個(gè)時(shí)鐘周期最多可以執(zhí)行8條指令,其中包括4條矢量運(yùn)算(A1tiVec)指令和2條整型指令。系統(tǒng)采用MPC7410為核心處理器搭建嵌入式系統(tǒng)硬件平臺(tái)。利用Tsi107芯片組的PCI接口連接以太網(wǎng)。網(wǎng)口是系統(tǒng)非常重要的通信接口,通常情況下操作系統(tǒng)映像的下載以及與外界的通信都是通過(guò)以太網(wǎng)口進(jìn)行的。文中介紹了以太網(wǎng)接口硬件設(shè)計(jì)和VxWorks BSP的開(kāi)發(fā)。

2 系統(tǒng)結(jié)構(gòu)概述

整個(gè)系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

在系統(tǒng)中使用了Motorola公司的RISC處理器Pow—erPC7410作為核心處理器,該處理器具有高性能和低功耗的特點(diǎn),外接一個(gè)2 MB L2作為二級(jí)緩存,以提高運(yùn)算速度。以Tundra公司為PowerPC專(zhuān)門(mén)設(shè)計(jì)的橋芯片/存儲(chǔ)器控制器Tsil07作為北橋芯片,利用60X總線(xiàn)和MPC7410相接,用以把60X總線(xiàn)信號(hào)轉(zhuǎn)化為PCI總線(xiàn)信號(hào),并管理FLASH和SDRAM。此設(shè)計(jì)充分利用60X總線(xiàn)高數(shù)據(jù)傳輸速率和優(yōu)秀的連接性能,發(fā)揮了MPC7410的高可靠性和強(qiáng)大的處理能力,使該硬件平臺(tái)具有很高的性能。

3 Tsil07的PCI接口

Tsil07的PCI接口與PCI 2.1規(guī)范兼容。使用一個(gè)32位地址/數(shù)據(jù)復(fù)用線(xiàn)。在PCI總線(xiàn)和處理器或本地memory之間提供內(nèi)部緩沖。處理器讀和寫(xiě)操作分別有1個(gè)32 B緩沖,memory操作具有2個(gè)32 B讀緩沖和2個(gè)32 B寫(xiě)緩沖。PCI總線(xiàn)使用中央仲裁方式,每一個(gè)master都有它自己的請(qǐng)求(REQ)和獲得(GNT)信號(hào)。可通過(guò)一個(gè)簡(jiǎn)單的請(qǐng)求——獲得握手獲得總線(xiàn)的控制權(quán)。仲裁在前一個(gè)訪問(wèn)時(shí)發(fā)生,故不會(huì)占用PCI總線(xiàn)的周期。

Tsil07為自身和另外最多5個(gè)PCI總線(xiàn)master提供總線(xiàn)仲裁邏輯,可通過(guò)設(shè)置PCI仲裁控制寄存器(PACR)的位15決定是否使能(置為1)或禁止(置為O)片內(nèi)PCI仲裁器。在復(fù)位信號(hào)(HRESET)為高時(shí)采集SDMA9以確定片內(nèi)PCI仲裁器被使能(低)或禁止(高)。

片內(nèi)PCI仲裁器使用一個(gè)可編程的、兩級(jí)、round—robin仲裁算數(shù)邏輯,5個(gè)外部master的每一個(gè),加上Tsi107使用PACR中的適當(dāng)位被編成2個(gè)優(yōu)先級(jí),高或低。低優(yōu)先級(jí)組在高優(yōu)先級(jí)組中共同占用一個(gè)總線(xiàn)請(qǐng)求傳輸通道。系統(tǒng)中如果有N個(gè)高優(yōu)先級(jí)設(shè)備和M個(gè)低優(yōu)先級(jí)設(shè)備,則每一個(gè)高優(yōu)先級(jí)設(shè)備最少會(huì)得到![]() 總線(xiàn)傳輸,每個(gè)低優(yōu)先級(jí)的設(shè)備最少會(huì)得到

總線(xiàn)傳輸,每個(gè)低優(yōu)先級(jí)的設(shè)備最少會(huì)得到![]() 總線(xiàn)傳輸。

總線(xiàn)傳輸。

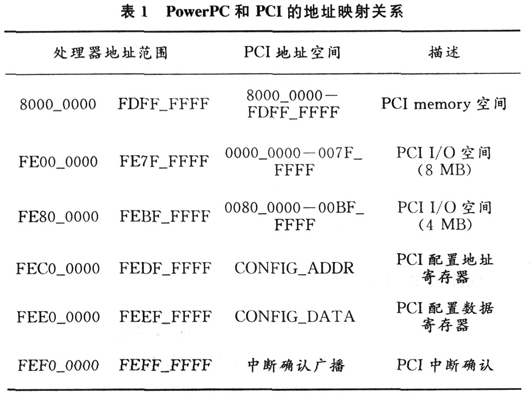

4 地址映射關(guān)系

根據(jù)Tsi107在電路中所起的作用它的工作方式可以分為2種,host mode和agent mode。在host mode,Pow—erPC是整個(gè)板子的主CPU,Tsi107管理整個(gè)系統(tǒng)的Memory和PCI總線(xiàn)。在agent mode,PowerPC系統(tǒng)是一個(gè)PCI設(shè)備,Tsi107負(fù)責(zé)和PCI主橋通信,管理這個(gè)PCI設(shè)備局部的memory。整個(gè)PowerPC系統(tǒng)受PCI主橋管理。在本系統(tǒng)中Tsi107工作在host mode。Tsil07在host mode時(shí)可采用2種地址映射方式,map A和map B。在復(fù)位時(shí)通過(guò)地址映射配置引腳SDBA0選擇地址映射方式。如果Tsi107工作在host mode并且SDBA0上拉,則Tsil07使用map B。建議不使用map A,使用map B時(shí),PowerPC和PCI的地址映射關(guān)系如表1所示。

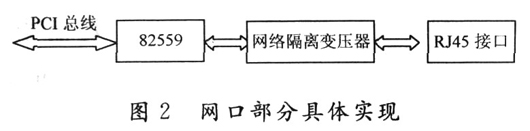

5 網(wǎng)口部分設(shè)計(jì)

網(wǎng)口部分的設(shè)計(jì)基于芯片組Tsil07控制的PCI總線(xiàn),基本框圖如圖2。

網(wǎng)口部分主要由Intel 82559,網(wǎng)絡(luò)隔離變壓器和RJ45接口3部分組成。82559是一個(gè)高集成度、高性能、低功耗的10/100 Mb/s快速以太網(wǎng)控制器,符合LON設(shè)計(jì)規(guī)范。物理尺寸只有15 mm×15 mm,是一款高性?xún)r(jià)比芯片。82559有完整的PCI接口,既可作主設(shè)備又可作從設(shè)備,在系統(tǒng)上電對(duì)其進(jìn)行配置時(shí)只能作為從設(shè)備,正常工作后可作為主設(shè)備。32位的PCI控制器使82559在PCI總線(xiàn)上執(zhí)行高速的數(shù)據(jù)傳輸。并且PCI控制器可處理通信任務(wù),因而減輕CPU的負(fù)擔(dān)。82559包含一個(gè)傳輸FIFO和一個(gè)接收FIFO,大小各為3 kB,在等待總線(xiàn)傳輸時(shí)可防止數(shù)據(jù)的流失。這將使82559利用最小的幀間距傳送數(shù)據(jù)。82559可工作在全雙工和半雙工模式。82559連接一個(gè)E2PROM,E2PROM為硬件和軟件提供上電初始化。在82559芯片上集成了MAC(介質(zhì)訪問(wèn)子層)和PHY(物理層)的功能,通過(guò)片上的命令和狀態(tài)寄存器經(jīng)由PCI總線(xiàn)和PowerPC通信。H1102是一個(gè)網(wǎng)絡(luò)隔離變壓器,82559通過(guò)網(wǎng)絡(luò)隔離變壓器驅(qū)動(dòng)剛45網(wǎng)線(xiàn)接口,用來(lái)支持10/100BASE—T,實(shí)現(xiàn)與外界通信。

6 以太網(wǎng)的VxWorks BSP的開(kāi)發(fā)

BSP即Board Support Package,板級(jí)支持包,是對(duì)目標(biāo)系統(tǒng)的底層支持軟件。對(duì)于具體的硬件平臺(tái),與硬件相關(guān)的代碼都被封裝在BSP中,由BSP向上提供虛擬的硬件平臺(tái),BSP與操作系統(tǒng)通過(guò)定義好的接口進(jìn)行交互。BSP是所有與硬件相關(guān)的代碼體的集合,是介于底層硬件和上層操作系統(tǒng)之間的一層,主要目的是為了支持操作系統(tǒng),使之能夠更好地運(yùn)行于硬件系統(tǒng)。以下介紹了網(wǎng)口的VxWorks BSP的開(kāi)發(fā)方法。

6.1 Tsil07的PCI接口的寄存器初始化

對(duì)Tsil07的PCI接口的寄存器初始化主要是對(duì)PCI命令寄存器,PCI狀態(tài)寄存器,PCI仲裁控制寄存器等和PCI相關(guān)的寄存器設(shè)置。因用戶(hù)手冊(cè)上對(duì)各寄存器的參數(shù)進(jìn)行了詳細(xì)的說(shuō)明,在此將不再贅述。

Tsil07中的32位配置寄存器地址是0x8000_00nn,nn是寄存器的相對(duì)偏移地址。對(duì)配置寄存器的訪問(wèn)采用間接方式,將配置寄存器的地址寫(xiě)到CONFIG_ADDR端口,則配置寄存器的內(nèi)容將在CONFIG_DATA端口獲得。CONFIG_ADDR端口的地址為:OxFEC0_0000~OXFEDF_FFFC,CONFIG_DATA端口的地址為0xFEE0_0000~0xFEEF_FFFF。

6.2 82559的PCI接口的寄存器初始化

對(duì)Tsil07的PCI接口的寄存器初始化包括對(duì)PCI命令寄存器,PCI狀態(tài)寄存器,Cache行大小(CLS)寄存器等寄存器的設(shè)置,以便能夠找到PCI設(shè)備82559,使Power—PC能夠?qū)υ撛O(shè)備進(jìn)行訪問(wèn)。

PCI定義了3個(gè)地址空間:PCI memory空間,PCII/O空間和PCI配置空間。PCI memory空間,PCI I/O空間采用直接訪問(wèn)。PCI支持2種類(lèi)型的配置訪問(wèn),typeO和type 1。AD[31:O]信號(hào)表示地址時(shí)根據(jù)配置訪問(wèn)的類(lèi)型使用不同的形式,地址的低兩位表明配置訪問(wèn)的類(lèi)型——type O(AD[1:O]=ObOO)或type 1(AD[1:O]=Ob01)。2種地址形式都表明了一個(gè)具體的設(shè)備和該設(shè)備的一個(gè)具體的配置寄存器。typel 0用于在本地PCI總線(xiàn)上選擇一個(gè)設(shè)備,type 1通過(guò)一個(gè)PCI—to—PCI橋傳遞配置請(qǐng)求到另一個(gè)PCI總線(xiàn)。系統(tǒng)采用type O配置,如圖3所示。

為訪問(wèn)配置空間,必須向CONFIG_ADDR寄存器寫(xiě)入一個(gè)32位的值,用于定義目標(biāo)PCI總線(xiàn)、該總線(xiàn)上的目標(biāo)設(shè)備和設(shè)備中要訪問(wèn)的配置寄存器。對(duì)CONFIG_DATA寄存器的一個(gè)讀或?qū)懖僮鲗⑹怪鳂驅(qū)⒃撛L問(wèn)轉(zhuǎn)化為一個(gè)PCI配置周期(CONFIG_ADDR中的使能位被設(shè)置并且設(shè)備編號(hào)不是0b1_1111)。

對(duì)于map B,處理器可在地址空間0xFEC0_0000~0xFEDF_FFFF中使用任何地址訪問(wèn)CONFIG_ADDR寄存器。盡管系統(tǒng)可以使用0xFEC0_0000~OxFEDF_FFFF中的任何地址,但一般使用地址0xFEC0_0CF8。為簡(jiǎn)化CONFIG_ADDR的地址通常被稱(chēng)為CF8。處理器可在地址空間0xFEE0_0000~0xFEEF_FFFF中的任何地址訪問(wèn)CONFIG_DATA寄存器。最常用的地址為0xFEE0_OCFC~0xFEE0_0CFF。為簡(jiǎn)化起見(jiàn),一般指為CFC。

對(duì)于type O配置,Tsi107把CONFIG_ADDR寄存器的設(shè)備編號(hào)轉(zhuǎn)化為惟一的IDSEL信號(hào),它們之間有一一對(duì)應(yīng)的關(guān)系。功能編號(hào)和寄存器編號(hào)將不加改變的復(fù)制到AD[10:2],AD[1:O]在type O配置時(shí)為0b00。

6.3 中斷的實(shí)現(xiàn)

Tsil07的EPIC(可編程中斷控制單元)支持5個(gè)外部中斷。IRQ[O:4]信號(hào)代表了外部中斷,它們被5個(gè)IRQ向量/優(yōu)先級(jí)寄存器(IVPRO—IVPR4)控制和初始化。外部中斷可被設(shè)置為電平或邊沿觸發(fā)。軟件通過(guò)對(duì)向量/優(yōu)先級(jí)寄存器的寫(xiě)操作為每一個(gè)中斷源設(shè)置優(yōu)先級(jí),優(yōu)先級(jí)的值在O~15之間,15最高。EPIC單元通過(guò)麗向處理器核申請(qǐng)中斷。當(dāng)處理器通過(guò)對(duì)EPIC單元中的中斷響應(yīng)寄存器(IACK)進(jìn)行讀操作以響應(yīng)中斷請(qǐng)求時(shí),EPIC返回一個(gè)8位的中斷向量到處理器,然后處理器處理該中斷。處理器對(duì)EPIC單元的結(jié)束中斷(EOI)寄存器進(jìn)行寫(xiě)操作時(shí),中斷處理完成。

對(duì)EPIC的初始化主要是設(shè)置各中斷源的優(yōu)先級(jí)和中斷向量的設(shè)置。包括對(duì)特征報(bào)告寄存器(FRR)、全局配置寄存器(GCR)、偽向量寄存器(SVR)、外部和內(nèi)部中斷寄存器等的設(shè)置。

7 結(jié) 語(yǔ)

搭建以MPC7410為核心處理器的嵌入式系統(tǒng)硬件平臺(tái),闡述以太網(wǎng)接口硬件設(shè)計(jì)和VxWorks BSP的設(shè)計(jì)方法,使以太網(wǎng)接口在系統(tǒng)中能正常通信。