摘 要: 復(fù)位是FPGA設(shè)計中一個基本而又重要的問題,如果處理不當,,不僅可能導(dǎo)致亞穩(wěn)態(tài)的問題,,而且會降低設(shè)計的資源利用率。分析了不同的復(fù)位方式對系統(tǒng)亞穩(wěn)態(tài)和資源利用率的影響,,并對不同的目標器件中復(fù)位信號的使用給出了建議,。

關(guān)鍵詞: 復(fù)位;亞穩(wěn)態(tài),;資源利用率

在FPGA設(shè)計中,,復(fù)位信號扮演著重要的角色,設(shè)計人員通常都使用一個外部輸入的全局復(fù)位信號在上電初期對系統(tǒng)進行初始化[1-2],。通常,,F(xiàn)PGA中的全局復(fù)位信號一般由3種途徑獲得[3]:(1)用一個復(fù)位按鈕產(chǎn)生一個復(fù)位信號接到FPGA的全局復(fù)位管腳上,它的速度非常慢,而且存在抖動的問題;(2)上電時由電源芯片產(chǎn)生,如TI公司TPS76x系列的電源系統(tǒng)一般都可以產(chǎn)生復(fù)位信號,,供主芯片上電復(fù)位使用,;(3)由微處理器產(chǎn)生復(fù)位脈沖,這個是設(shè)計人員可以方便使用程序控制的,。

全局復(fù)位管腳類似于其他任何輸入管腳,,通常都是異步的,設(shè)計人員可以在FPGA中將其當作異步或同步復(fù)位信號來使用,, 但一個最佳的復(fù)位結(jié)構(gòu)卻可以對FPGA的亞穩(wěn)態(tài)和資源利用率產(chǎn)生很大的影響,。

1 復(fù)位與亞穩(wěn)態(tài)

1.1 異步復(fù)位

在大多數(shù)FPGA設(shè)計中,外部輸入的全局復(fù)位信號被直接當作異步復(fù)位來使用,。這種用法在可控的仿真環(huán)境下工作正常,,然而在真實的系統(tǒng)中卻常常會出現(xiàn)不規(guī)律的錯誤,其原因在于設(shè)計人員常常低估了真實系統(tǒng)中復(fù)位信號的“釋放”問題,,這個問題可能導(dǎo)致系統(tǒng)中的觸發(fā)器進入亞穩(wěn)態(tài),,從而影響整個系統(tǒng)的穩(wěn)定性[4]。

常用的異步復(fù)位電路Verilog描述如下:

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n) q <= 1’b0;

else q <= d;

end

在Quartus Ⅱ中綜合出的異步復(fù)位電路模型如圖1所示,。圖2為異步復(fù)位電路的復(fù)位時序圖,。

如果異步復(fù)位信號的撤銷時間在Trecovery(恢復(fù)時間)和Tremoval(移除時間)之內(nèi),,則造成亞穩(wěn)態(tài)的產(chǎn)生,觸發(fā)器的輸出在時鐘邊沿的Tco后會產(chǎn)生振蕩,,最終穩(wěn)定到“0”或者“1”,,這就有可能造成復(fù)位失敗。

1.2 同步復(fù)位

由于全局復(fù)位信號通常是異步的,,因此,,有些設(shè)計人員采用同步復(fù)位電路對FPGA進行復(fù)位,并且絕大多數(shù)文獻資料認為同步復(fù)位電路都不會發(fā)生亞穩(wěn)態(tài),,其實不然,,同步電路也會發(fā)生亞穩(wěn)態(tài),只是幾率小于異步復(fù)位電路,。

常用的同步復(fù)位電路Verilog描述如下:

always @ (posedge clk)

begin

if(!rst_n) q <= 1’b0;

elseq <= d;

end

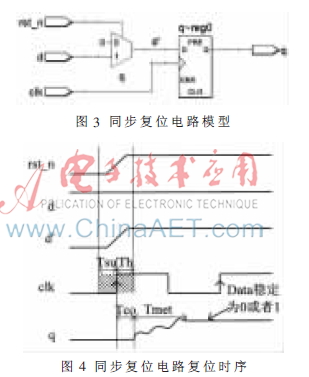

在Quartus Ⅱ中綜合出的異步復(fù)位電路模型如圖3所示,其復(fù)位時序圖如圖4所示,。

當輸入端d為高電平且復(fù)位信號的撤銷時間在clk的Tsu(建立時間)和Th(保持時間)內(nèi)時,亞穩(wěn)態(tài)就隨之產(chǎn)生了,。如圖4所示,,當復(fù)位信號的撤銷時間在clk的Tsu和Th內(nèi)時,輸入數(shù)據(jù)為“1”,,通過和輸入數(shù)據(jù)相“與”后產(chǎn)生的信號d’也在clk的Tsu和Th內(nèi),,因此,勢必會造成類似異步信號采集的亞穩(wěn)態(tài)情況,。

1.3 異步復(fù)位,、同步釋放

為了解決單純的異步復(fù)位或同步復(fù)位所帶來的亞穩(wěn)態(tài)問題,一種常用的處理方式是異步復(fù)位,、同步釋放,。其Verilog描述如下:

always @ (posedge clk or negedge rst_n_asyn)

begin

if (!rst_n_asyn)

begin

temp <= 1′b0;

rst_n_syn <= 1′b0;

end

else

begin

temp <= 1′b1;

rst_n_syn <= temp;

end

end

在Quartus Ⅱ中綜合出的異步復(fù)位、同步釋放電路模型如圖5所示,。

由圖5可以看出,,新產(chǎn)生的復(fù)位信號rst_n_syn是一個同步化了的異步復(fù)位信號,其復(fù)位時刻的到來不受時鐘信號的影響,,同時其復(fù)位釋放的時刻卻與時鐘信號同步,。這種復(fù)位方式很好地將異步復(fù)位和同步復(fù)位的優(yōu)點結(jié)合起來,設(shè)計人員在開發(fā)FPGA工程時只需要在每個時鐘域內(nèi)用這種異步復(fù)位,、同步釋放的復(fù)位結(jié)構(gòu)產(chǎn)生一個局部的復(fù)位信號rst_n_syn,,并用它來對該時鐘域內(nèi)的所有模塊進行復(fù)位,便可以有效地降低亞穩(wěn)態(tài)出現(xiàn)的幾率。

2 復(fù)位與資源利用率

在不同的目標器件中,,寄存器對復(fù)位的異步或同步,、高電平或低電平有不同的要求和實現(xiàn),因此,,不同的復(fù)位方式對FPGA的資源利用率也將產(chǎn)生很大的影響,。

2.1 Altera公司的FPGA

在Altera公司的FGPA中,,每個寄存器都有一個異步的清零輸入端[5]。高/低電平的異步/同步復(fù)位電路在Quartus Ⅱ中綜合出的電路模型如圖6~圖9所示,。

由圖6~圖9所示的電路模型可以看出,,在Altera公司的FPGA中,不論是高電平還是低電平的異步復(fù)位,直接使用了寄存器的CLR端口,;然而如果是同步復(fù)位,,綜合后會在其寄存器的數(shù)據(jù)路徑上增加一個數(shù)據(jù)選擇器,將復(fù)位信號作為輸入邏輯的使能信號,,這樣不僅增加了設(shè)計的資源占用量,,而且增加了數(shù)據(jù)信號的路徑時延。

2.2 Xilinx公司的FPGA

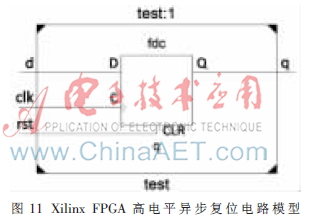

在Xilinx公司的FGPA中,,每個寄存器都有一個專用的清零輸入端[6],。高/低電平的異步/同步復(fù)位電路在ISE 12.4中綜合出的電路模型如圖10~圖13所示。

由圖10~圖13所示的電路模型可以看出,,在Xilinx的FPGA中,不論是同步的還是異步的高電平復(fù)位,,直接使用了寄存器的專用清零輸入端,;然而如果是低電平復(fù)位,綜合后會在復(fù)位路徑上增加一個反相器,,這樣不僅增加了設(shè)計的資源占用量,,而且增加了復(fù)位信號的路徑時延。

從以上分析可以看出,, 在FPGA設(shè)計中,,通過異步復(fù)位、同步釋放的復(fù)位結(jié)構(gòu)將外部輸入的全局復(fù)位信號進行同步化,,可以降低系統(tǒng)中亞穩(wěn)態(tài)出現(xiàn)的幾率,,增加系統(tǒng)復(fù)位的可靠性; 同時,在Altera公司的FPGA中對寄存器使用高電平或低電平的異步復(fù)位,、在Xilinx公司的FPGA中對寄存器使用異步或同步的高電平復(fù)位,,均可以降低設(shè)計的資源占用量,提高資源利用率,。因此,,在FPGA設(shè)計時,設(shè)計人員應(yīng)該根據(jù)不同的應(yīng)用場景和不同的目標器件區(qū)別使用復(fù)位方式,,以取得最佳的復(fù)位效果,。

參考文獻

[1] 周偉,杜玉曉,楊其宇,等.FPGA跨時鐘域亞穩(wěn)態(tài)研究[J].

電子世界, 2012(3):87-89.

[2] 黃隸凡,鄭學(xué)仁.FPGA設(shè)計中的亞穩(wěn)態(tài)研究[J]. 微電子

學(xué), 2011,41(2):265-268,273.

[3] CHAPMAN K. Get smart about reset think local, not

global[Z]. Xilinx FPGAs, 2008.

[4] 汪路元.FPGA設(shè)計中的亞穩(wěn)態(tài)及其緩解措施[J].電子技

術(shù)應(yīng)用,,2012,38(8):13-15.

[5] Altera. Cyclone IV device handbook[Z].2013.

[6] Xilinx. Virtex-5 family overview[Z].2009.