創(chuàng)新,是Altera公司成功的因素之一,也是FPGA產(chǎn)品在多個(gè)領(lǐng)域備受關(guān)注的原因所在。就像Altera公司亞太區(qū)副總裁兼董事總經(jīng)理Erhaan Shaikh所介紹的,微軟宣布將使用Altera的FPGA產(chǎn)品來實(shí)現(xiàn)Bing搜索引擎的加速;2014年Intel的開發(fā)者大會(huì)上,Intel表示使用FPGA的產(chǎn)品配合實(shí)現(xiàn)CPU的加速;IBM和Altera將在OpenCL方面進(jìn)行合作;Altera與中國(guó)移動(dòng)研究院共同發(fā)展下一代5G網(wǎng)絡(luò),即5G-RAN……

Altera公司亞太區(qū)副總裁兼董事總經(jīng)理Erhaan Shaikh

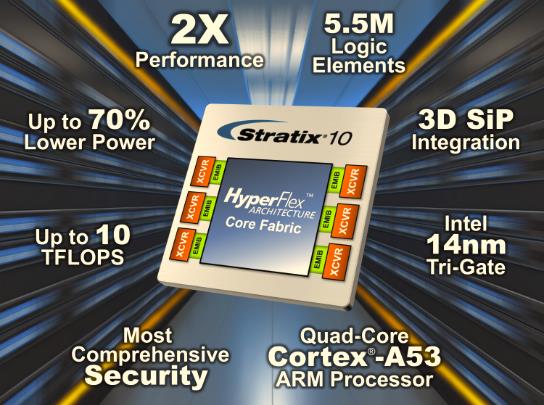

而Stratix 10,這一可編程世界中的又一個(gè)巨大突破,給我們帶來的將是哪些改變?它與原有的28nm產(chǎn)品相比性能提高了2倍,這又是如何實(shí)現(xiàn)的?

Altera公司產(chǎn)品營(yíng)銷資深總監(jiān) Patrick Dorsey解答了上述疑惑:“Stratix 10之所以能實(shí)現(xiàn)這樣的性能提升主要基于兩大技術(shù),一個(gè)是Intel 的14 nm三柵極技術(shù),第二個(gè)就是Altera公司創(chuàng)新的HyperFlex架構(gòu)。正是由于這兩個(gè)大技術(shù)的使用,我們才實(shí)現(xiàn)了新一代產(chǎn)品性能的極大突破。”

Altera公司產(chǎn)品營(yíng)銷資深總監(jiān) Patrick Dorsey

HyperFlex:十多年來最大的FPGA體系結(jié)構(gòu)創(chuàng)新,解決布線難題

在傳統(tǒng)的架構(gòu)當(dāng)中,系統(tǒng)性能能否得到提高,很大程度上受制于實(shí)現(xiàn)連接的速度有多快。Patrick Dorsey表示:“布線延時(shí)是系統(tǒng)性能瓶頸的主要因素。通常我們采用的更寬的總線無異于飲鳩止渴,它絕不是解決問題的根本方案,反而會(huì)增加擁塞。要從根本上解決問題,我們就要從布線上尋求創(chuàng)新。”

HyperFlex體系結(jié)構(gòu)解決了布線難題

HyperFlex體系結(jié)構(gòu)的核心是“無處不在”,它在所有內(nèi)核互聯(lián)布線段上引入了寄存器,使得Stratix 10 FPGA和SoC能夠受益于成熟可靠的性能增強(qiáng)設(shè)計(jì)方法,例如寄存器重新定時(shí)、流水線和其他設(shè)計(jì)優(yōu)化方法。這些設(shè)計(jì)方法在傳統(tǒng)的FPGA體系結(jié)構(gòu)中是不可能實(shí)現(xiàn)的。HyperFlex體系結(jié)構(gòu)幫助設(shè)計(jì)人員避免了關(guān)鍵通路和布線延時(shí),其設(shè)計(jì)能夠迅速達(dá)到時(shí)序收斂。內(nèi)核邏輯性能提高2倍后,不需要很寬的數(shù)據(jù)通路,也不需要競(jìng)爭(zhēng)體系結(jié)構(gòu)由于其他偏移導(dǎo)致的設(shè)計(jì)結(jié)構(gòu),極大的提高了器件利用率,降低了功耗。HyperFlex體系結(jié)構(gòu)支持高性能設(shè)計(jì)降低邏輯面積要求,功耗從而降低了70%。

異構(gòu)3D SiP集成的新時(shí)代:單片F(xiàn)PGA內(nèi)多個(gè)裸片封裝

Stratix 10 FPGA和SoC系列的所有型號(hào)都采用了異構(gòu)3D SiP集成技術(shù)高效經(jīng)濟(jì)的集成高密度單片F(xiàn)PGA內(nèi)核架構(gòu)(高達(dá)5.5M邏輯單元)以及其他先進(jìn)的組件,從而提高了Stratix 10 FPGA和SoC的可擴(kuò)展性和靈活性。單片內(nèi)核架構(gòu)避免了使用多個(gè)FPGA管芯來提高密度的競(jìng)爭(zhēng)同構(gòu)器件的連接問題。Altera的異構(gòu)SiP集成技術(shù)是通過使用Intel的專用嵌入式多管芯互聯(lián)橋接(EMIB,Embedded Multi-die Interconnect Bridge)技術(shù)實(shí)現(xiàn)的,與基于中介層的方法相比,進(jìn)一步提高了性能,降低了復(fù)雜度和成本,增強(qiáng)了信號(hào)完整性。

“我們之所以選擇使用Intel的這項(xiàng)封裝技術(shù),出于三方面的考慮。第一,數(shù)據(jù)的吞吐量,急速提升,從十幾Gb/s到五十幾Gb/s。通常在單一芯片當(dāng)中很難實(shí)現(xiàn)如此大量的數(shù)據(jù)傳輸。第二,客戶希望能夠盡快地受益于HyperFlex架構(gòu),同時(shí)要求這些芯片支持那些尚未被確定為標(biāo)準(zhǔn)的協(xié)議,所以這對(duì)于我們來說面臨著一個(gè)兩難的選擇。第三就是調(diào)制格式的問題,隨著要求越來越高,芯片之間的對(duì)話方式也變得更加具體化,我們必須要使得一個(gè)邏輯與另外一個(gè)器件進(jìn)行對(duì)話的時(shí)候,它使用到的引腳得到很大程度的優(yōu)化,從而使得這兩個(gè)芯片能夠以一種很具體的方式來實(shí)現(xiàn)溝通。”Patrick Dorsey解釋道。

初次發(fā)布的Stratix 10器件將使用EMIB來集成高速串行收發(fā)器和協(xié)議塊以及單片內(nèi)核邏輯。通過異構(gòu)3D SiP方法實(shí)現(xiàn)高速協(xié)議和收發(fā)器,Altera將能夠快速交付Stratix 10器件型號(hào),滿了不斷發(fā)展的市場(chǎng)需求。例如,使用異構(gòu)3D SiP集成技術(shù)為Stratix 10器件提供了途徑來實(shí)現(xiàn)更高的收發(fā)器速率(56 Gbps)、新出現(xiàn)的調(diào)制格式(PAM-4)、通信標(biāo)準(zhǔn)(PCIe Gen4、多端口以太網(wǎng)),以及模擬和寬帶存儲(chǔ)器等其他功能。

創(chuàng)新的安全設(shè)計(jì)管理器:提供業(yè)界最全面的安全功能

第十代的FPGA產(chǎn)品,其中會(huì)涉及到500多萬個(gè)邏輯單元,相比當(dāng)前一代產(chǎn)品在邏輯單元數(shù)量上提升了5倍之多。Patrick Dorsey分析:“通過創(chuàng)新的安全設(shè)計(jì)管理器,我們可以把這些FPGA的邏輯單元分離開來,在每一個(gè)單元上面都可以有單獨(dú)的一個(gè)芯片,使它的安全性能得到很大的提高。對(duì)于云提供商來說,他們可以把某一個(gè)客戶的應(yīng)用和另外客戶的應(yīng)用區(qū)分開,最大程度地保障客戶應(yīng)用的安全性。”

除了上述創(chuàng)新的性能提升之外,Altera還提供了全面的設(shè)計(jì)環(huán)境和Enpirion電源模組來支持Stratix 10的應(yīng)用。