摘 要: 采用FPGA搭建圖像處理系統(tǒng),通過(guò)硬件算法實(shí)現(xiàn)圖像的流水線及并行處理,實(shí)現(xiàn)了對(duì)具有特定顏色的物體的識(shí)別與跟蹤。整個(gè)系統(tǒng)工作于像素頻率,避免了算法的程序跑飛現(xiàn)象,使系統(tǒng)的可靠性大為提高,較好地保持了系統(tǒng)的低功耗特性,且優(yōu)于DSP等串行處理器結(jié)合軟件算法來(lái)實(shí)現(xiàn)的方法。

關(guān)鍵詞: FPGA;圖像識(shí)別;目標(biāo)跟蹤

0 引言

近年基于FPGA硬件技術(shù)的視頻圖像處理系統(tǒng)被廣泛地應(yīng)用于視頻智能監(jiān)控、智能交通系統(tǒng)、視頻采集和跟蹤系統(tǒng)等[1]。作為機(jī)器視覺(jué)的一個(gè)重要研究方向,動(dòng)態(tài)目標(biāo)檢測(cè)在視頻智能監(jiān)控、智能交通系統(tǒng)等方面得到了越來(lái)越多的應(yīng)用[2]。通常圖像識(shí)別與跟蹤算法可以通過(guò)軟件或者硬件來(lái)實(shí)現(xiàn),但出于成本及開(kāi)發(fā)難度的考慮,圖像識(shí)別與跟蹤一般由軟件來(lái)實(shí)現(xiàn)。在高速、高分辨率的情況下,傳統(tǒng)軟件的串行處理算法不足以應(yīng)對(duì)大量的運(yùn)算以及嚴(yán)格的時(shí)間要求,而采用硬件算法則可以實(shí)現(xiàn)并行或者流水的運(yùn)算結(jié)構(gòu),大大地加快了運(yùn)算速度[3]。目前可采用硬件實(shí)現(xiàn)的主要方案包括:DSP數(shù)字信號(hào)處理器、專用的集成圖像處理芯片、FPGA和配合的相關(guān)電路。與其他方案相比,使用FPGA芯片豐富的硬件資源以及硬件可重構(gòu)性,可大大提高圖像識(shí)別跟蹤系統(tǒng)的靈活性和通用性。

本設(shè)計(jì)通過(guò)使用可編程邏輯器件和硬件算法進(jìn)行圖像處理以實(shí)現(xiàn)對(duì)圖像中特定目標(biāo)進(jìn)行識(shí)別和跟蹤,并通過(guò)并行和流水線結(jié)構(gòu)算法大大加快圖像處理的速度,使得處理速率與輸入時(shí)鐘同步,真正地做到了無(wú)延時(shí)處理。

1 系統(tǒng)整體功能概述

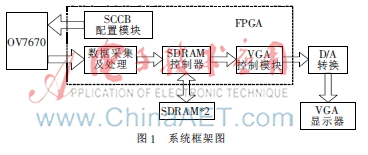

本設(shè)計(jì)中采用Altera公司的EP2C8系列FPGA作為系統(tǒng)核心。圖像從30萬(wàn)像素CMOS攝像頭輸入,F(xiàn)PGA負(fù)責(zé)圖像處理以及接口管理,因攝像頭與VGA接口的幀率不同,所以使用SDRAM作為幀緩沖。高速視頻DAC芯片ADV7123負(fù)責(zé)把RGB圖像數(shù)據(jù)轉(zhuǎn)換成模擬量,以實(shí)現(xiàn)VGA輸出。系統(tǒng)的框架圖如圖1所示,整個(gè)系統(tǒng)采用5 V直流供電,可以通過(guò)AS或者JTAG接口進(jìn)行調(diào)試以及程序的下載。通過(guò)鍵盤(pán)可以切換系統(tǒng)的工作狀態(tài),改變圖像的處理效果。

2 硬件設(shè)計(jì)

要實(shí)現(xiàn)圖像處理,首先要搭建好圖像的采集系統(tǒng),實(shí)現(xiàn)對(duì)輸入圖像正確的顯示。由于系統(tǒng)處理的數(shù)據(jù)量大,速度快,對(duì)硬件電路的設(shè)計(jì)以及器件布局布線都有較高的要求。

2.1 FPGA外圍電路設(shè)計(jì)

FPGA的外圍電路包括時(shí)鐘電路、復(fù)位電路、JTAG以及AS調(diào)試接口。本設(shè)計(jì)提供40 MHz和50 MHz時(shí)鐘輸入,50 MHz時(shí)鐘可通過(guò)PLL倍頻到100 MHz作為SDRAM時(shí)鐘,也可分頻到25 MHz作為CMOS攝像頭時(shí)鐘;而40 MHz作為后備時(shí)鐘。JTAG接口可把配置數(shù)據(jù)下載到FPGA的內(nèi)部RAM上,并可以通過(guò)SignalTap嵌入式邏輯分析儀對(duì)FPGA時(shí)序進(jìn)行分析。AS接口則可以把配置數(shù)據(jù)之間固化到串行EPROM上,使FPGA上電后自動(dòng)配置。

2.2 VGA接口設(shè)計(jì)

VGA接口芯片本質(zhì)上是三路獨(dú)立的高速DA,負(fù)責(zé)把數(shù)字化的圖像數(shù)據(jù)轉(zhuǎn)換成模擬量,以供顯示器顯示。為了阻抗匹配,模擬輸出端需并聯(lián)75 Ω電阻,DAC輸出電流的最大值由偏置電位器決定,通過(guò)調(diào)節(jié)電位器,可以調(diào)節(jié)輸出圖像的最大亮度。

2.3 SDRAM外圍電路設(shè)計(jì)

SRAM在存儲(chǔ)器中速度最快、最穩(wěn)定、操作最方便,但是由于其成本高,一般靜態(tài)存儲(chǔ)器只適用于存儲(chǔ)容量小、存儲(chǔ)速度要求高的場(chǎng)合。而SDRAM相對(duì)于SRAM制造成本低很多,隨著技術(shù)的進(jìn)步,SDRAM的速度越來(lái)越快,容量越來(lái)越大,穩(wěn)定性也越來(lái)越好。在視頻圖像處理中SDRAM主要用作數(shù)據(jù)緩存,也就是FPGA對(duì)SDRAM操作最頻繁的為讀命令、寫(xiě)命令,在這兩個(gè)命令中間插接激活、預(yù)充電、猝發(fā)終止、刷新等命令[4]。

SDRAM的主要作用是把經(jīng)過(guò)處理后的圖像數(shù)據(jù)以30 S/s的速率進(jìn)行緩存,然后再以60 S/s的速率讀取到VGA接口輸出。采用16 bit字寬的SDRAM,讀寫(xiě)時(shí)鐘為100 MHz。SDRAM總帶寬為100 MHz,其中攝像頭寫(xiě)入占用12.5 MHz帶寬,VGA讀取占用25 MHz帶寬,剩余的62.5 MHz帶寬可留作圖像處理使用。

3 算法設(shè)計(jì)

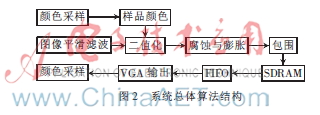

采用基于顏色的目標(biāo)識(shí)別算法從背景中分割目標(biāo)并動(dòng)態(tài)標(biāo)記,該算法實(shí)現(xiàn)簡(jiǎn)單,但對(duì)圖像的質(zhì)量要求較高。由于CMOS攝像頭輸出的圖像噪點(diǎn)較多,尤其在光照不足的情況下,因此圖像的預(yù)處理工作顯得尤為重要[5]。系統(tǒng)總體算法結(jié)構(gòu)如圖2所示。

預(yù)處理采用3×3的平滑濾波器對(duì)圖像進(jìn)行濾波。將處理后的圖像與樣品顏色進(jìn)行比較,當(dāng)圖像與樣品顏色的R、G、B分量的差值在一定范圍內(nèi)時(shí),圖像像素被標(biāo)記為白色,否則標(biāo)記為黑色,最終實(shí)現(xiàn)圖像的二值化。包圍盒對(duì)噪點(diǎn)非常敏感,在進(jìn)行包圍操作前,再對(duì)圖像進(jìn)行一次濾波處理。包圍盒的作用是找出目標(biāo)圖像像素的最小坐標(biāo)以及最大坐標(biāo),通過(guò)這兩個(gè)坐標(biāo)即可計(jì)算出目標(biāo)的中心位置。

3.1 圖像平滑濾波器設(shè)計(jì)

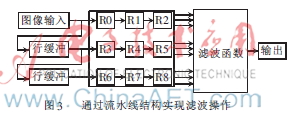

傳統(tǒng)的軟件算法在實(shí)現(xiàn)濾波操作時(shí),需要先把輸入和輸出圖像都緩沖到幀緩存中去,對(duì)于每個(gè)輸出像素,算法獲取輸入圖像對(duì)應(yīng)窗口的像素并用濾波函數(shù)計(jì)算來(lái)取得輸出值。由于每個(gè)輸出都需要讀取對(duì)應(yīng)窗口的輸入像素,勢(shì)必占用極大的內(nèi)存帶寬,并且處理性能會(huì)受到內(nèi)存帶寬的限制。由于每個(gè)輸入像素都會(huì)被多個(gè)窗口所利用,故可以先對(duì)輸入圖像進(jìn)行緩存,以便在后續(xù)的窗口中被重新利用[6]。本設(shè)計(jì)使用流水處理的方法,實(shí)現(xiàn)濾波算法的加速計(jì)算,算法結(jié)構(gòu)如圖3所示。

3.2 圖像二值化

在第一個(gè)時(shí)鐘的上升沿,攝像頭輸入的16 bit圖像數(shù)據(jù)先分割為R、G、B三個(gè)分量,分別為5 bit、6 bit、 5 bit,分別與樣本顏色的對(duì)應(yīng)分量進(jìn)行比較,通過(guò)減法器獲得對(duì)應(yīng)的誤差絕對(duì)值,下一個(gè)時(shí)鐘上升沿,這三個(gè)誤差的絕對(duì)值再與對(duì)應(yīng)的閾值進(jìn)行比較,最后把比較結(jié)果進(jìn)行與運(yùn)算,作為最終輸出。整個(gè)二值化操作的流水線延時(shí)為兩個(gè)時(shí)鐘周期。圖4為其中一個(gè)處理通道的簡(jiǎn)化表示。本設(shè)計(jì)的二值化操作是在RGB色彩空間上進(jìn)行的,只有在R、G、B三個(gè)通道上同時(shí)滿足條件的像素點(diǎn)才會(huì)被設(shè)為最大值。

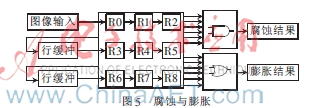

3.3 圖像腐蝕與膨脹

圖像的腐蝕操作能夠輕易地濾除面積小于窗口的孤立噪點(diǎn)而不影響圖像本身的清晰度,經(jīng)過(guò)腐蝕后目標(biāo)圖像會(huì)變小,需要膨脹操作來(lái)補(bǔ)償腐蝕的影響,與平滑濾波器相類似。其實(shí)現(xiàn)方法如圖5所示,經(jīng)過(guò)行緩沖的像素?cái)?shù)據(jù)依次進(jìn)入窗口,通過(guò)對(duì)窗口內(nèi)所有像素進(jìn)行與運(yùn)算來(lái)實(shí)現(xiàn)腐蝕,進(jìn)行或運(yùn)算來(lái)實(shí)現(xiàn)膨脹,其效果如圖6所示。

3.4 包圍盒設(shè)計(jì)

一組像素的包圍盒是指能夠包圍所有像素的最小矩形,本設(shè)計(jì)在進(jìn)行包圍操作之前已經(jīng)先對(duì)圖像進(jìn)行二值化分割,故只需要找出每一幀圖像中目標(biāo)像素橫縱坐標(biāo)的最大值和最小值即可實(shí)現(xiàn)對(duì)圖像的包圍操作。

4 結(jié)論

經(jīng)過(guò)處理后的圖像有VGA接口輸出,其效果如圖7所示。由于采用了硬件算法實(shí)現(xiàn)的并行以及流水結(jié)構(gòu),大大加快了圖像的處理速度,處理速度為900萬(wàn)像素每秒,流水線延時(shí)約為64 ?滋s。通過(guò)動(dòng)態(tài)流水線結(jié)構(gòu),系統(tǒng)可以把每一步中間處理的結(jié)果直接輸出到VGA,這樣就可以獨(dú)立地觀察每一步處理的實(shí)際效果。通過(guò)對(duì)比發(fā)現(xiàn),若關(guān)閉圖像預(yù)處理,則圖像中噪點(diǎn)明顯增多,包圍盒出現(xiàn)晃動(dòng),說(shuō)明圖像的預(yù)處理操作能夠提高識(shí)別和跟蹤的準(zhǔn)確度和穩(wěn)定性。

由于使用硬件算法,從本質(zhì)上避免了傳統(tǒng)軟件算法的程序跑飛現(xiàn)象,使得系統(tǒng)的可靠性大為提高。為了提高處理速度,傳統(tǒng)軟件算法往往只能通過(guò)提高系統(tǒng)的時(shí)鐘實(shí)現(xiàn),然而過(guò)高的時(shí)鐘頻率意味著高功耗和干擾,而本設(shè)計(jì)通過(guò)流水線結(jié)構(gòu),使整個(gè)處理系統(tǒng)工作于像素頻率,同時(shí)也保持了系統(tǒng)的低功耗特性。

參考文獻(xiàn)

[1] 鄭俊波,蘇成悅,何榕禮,等.Android終端及FPGA控制的智能家居系統(tǒng)[J].微型機(jī)與應(yīng)用,2014,33(5):93-95.

[2] 向厚振,張志杰,王鵬.基于FPGA視頻和圖像處理系統(tǒng)的FIFO緩存技術(shù)[J].電視技術(shù),2012,36(9):134-135.

[3] MARUYAMA T, YAMAGUCHI Y. How fast is an FPGA image processing[J]. IEICE Technical Report, 2008,108(48):83-88.

[4] 田豐,鄧建國(guó),李巍,等.SDRAM控制器的設(shè)備與VHDL實(shí)現(xiàn)[J].電子技術(shù)應(yīng)用,2010,36(2):74-77.

[5] OLSON T, SANFORDCARL W. Real-time multistage IR image-based tracker[J]. The International Society for Optical Engineering,2011,58(112):56-57.

[6] 王德勝,康令州.基于FPGA的實(shí)時(shí)圖像采集與預(yù)處理[J].電視技術(shù),2011,35(3):38-41.