文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2015)02-0035-03

0 引言

人的視網(wǎng)膜感受光信號(hào)刺激后,,將會(huì)誘發(fā)一系列源于視覺傳導(dǎo)通路及枕葉視皮層的電生理活動(dòng),,即視覺誘發(fā)電位(Visual Evoked Potential,VEP)[1],。在低刺激率(<3rev/s)下,,會(huì)誘發(fā)暫態(tài)視覺誘發(fā)電位(transient VEP,tVEP)。而當(dāng)刺激率提高(>7rev/s),,視覺誘發(fā)電位會(huì)出現(xiàn)穩(wěn)態(tài)反應(yīng)(Steady-State VEP,,SSVEP)[2]。Bobak的研究表明,,tVEP和SSVEP是由大腦不同生理通道處理產(chǎn)生[3],。Herrmann認(rèn)為,SSVEP反映了受刺激信號(hào)驅(qū)動(dòng)的神經(jīng)節(jié)律現(xiàn)象[4],。另外,,SSVEP在神經(jīng)視功能的評(píng)估方面有廣闊的應(yīng)用前景,是當(dāng)前視覺誘發(fā)電位領(lǐng)域的研究熱點(diǎn),。

在研究SSVEP的實(shí)驗(yàn)中,,需要給予受試者一個(gè)高頻率的視覺刺激信號(hào),并保證刺激圖像和觸發(fā)信號(hào)的同步性與準(zhǔn)確性,。視覺刺激器產(chǎn)生用于VEP檢查的視覺刺激信號(hào),,傳統(tǒng)的刺激器主要有兩種:(1)基于單片機(jī)的視覺刺激器,其原理是利用單片機(jī)輸出刺激圖像,。其性能穩(wěn)定,,但單片機(jī)內(nèi)部資源有限,變更刺激模式困難,;(2)基于PC的視覺刺激器,,是通過PC上的軟件編程實(shí)現(xiàn)圖像刺激。其優(yōu)點(diǎn)是方便修改代碼,,能靈活地產(chǎn)生不同刺激模式,。但因刺激器需運(yùn)行在多任務(wù)操作系統(tǒng)下,其時(shí)間精度有賴于CPU性能及對(duì)硬件的調(diào)度,。刺激器在產(chǎn)生高頻圖像刺激時(shí),,圖像刺激和觸發(fā)信號(hào)會(huì)出現(xiàn)延時(shí)[5],導(dǎo)致同步性變差,。在本實(shí)驗(yàn)中采用MATLAB產(chǎn)生高于30 rev/s的圖像刺激,,出現(xiàn)圖像失真和觸發(fā)信號(hào)延遲??梢?,單片機(jī)方式的不靈活和軟件方式的同步性差不能滿足目前SSVEP研究對(duì)刺激器的要求。

本文設(shè)計(jì)一種基于FPGA的高頻視覺刺激控制器,,從串口接收刺激模式命令,在由FPGA控制生成刺激圖像的同時(shí),,向采集設(shè)備發(fā)送觸發(fā)信號(hào),。測(cè)試結(jié)果表明,本文設(shè)計(jì)的高頻視覺刺激器能靈活地變更不同的刺激模式,,并確保了高刺激率下刺激圖像和采集信號(hào)的完全同步,。

1 系統(tǒng)整體設(shè)計(jì)

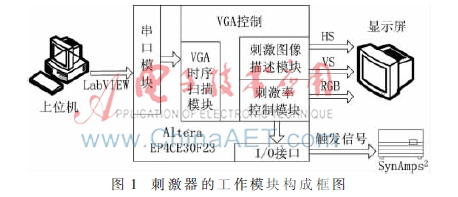

本文設(shè)計(jì)的高頻視覺刺激控制器采用Altera公司的EP4CE30型FPGA芯片作為主控器件,。整個(gè)視覺刺激器包括硬件和軟件兩個(gè)部分:(1)系統(tǒng)硬件部分,主要采用一塊FPGA電路板,,包括串口電路,、VGA接口電路、按鍵電路及I/O口等外圍電路,;(2)系統(tǒng)軟件部分,,主要是由硬件描述語言設(shè)計(jì)的FPGA程序組成,包括串口通信模塊,、VGA時(shí)序掃描模塊,、刺激圖像描述模塊及刺激率控制模塊。

刺激器工作原理如圖1所示,,視覺刺激器上電后,,讀取預(yù)置的配置文件完成硬件系統(tǒng)初始化。上位機(jī)通過LabVIEW編寫的用戶界面向串口發(fā)送刺激模式的選擇信號(hào)至FPGA芯片,。在串口模塊解析完上位機(jī)的控制指令后,, VGA控制模塊按所選的刺激模式開始行掃描和場(chǎng)掃描,在刺激圖像描述模塊中生成所需的刺激圖像,,并在刺激率控制模塊中產(chǎn)生相應(yīng)的刺激率信號(hào)及觸發(fā)信號(hào),,再將觸發(fā)信號(hào)發(fā)送到FPGA板上I/O口,經(jīng)并行接口送至誘發(fā)電位采集設(shè)備,,并把RGB,、行同步及場(chǎng)同步信號(hào)發(fā)送給VGA接口,通過接口上連接的顯示器向受試者給予視覺誘發(fā)刺激,。目前對(duì)于通過本刺激器所誘發(fā)的數(shù)據(jù)采集利用美國(guó)NeuroScan公司的SynAmps2系統(tǒng),,此系統(tǒng)需要接收一個(gè)來自刺激器的觸發(fā)信號(hào)(脈沖信號(hào)),用于標(biāo)記視覺刺激的開始位置,。

2 系統(tǒng)核心控制模塊

FPGA控制程序是本系統(tǒng)的核心部分,,本文根據(jù)模塊化設(shè)計(jì)方法把系統(tǒng)劃分為串口通信模塊、VGA時(shí)序掃描模塊,、刺激圖像描述模塊及刺激率控制模塊四大模塊,。然后把實(shí)例化的子模塊連接起來,組成一個(gè)完整的系統(tǒng),。

2.1 串口通信模塊

上位機(jī)和刺激器間的通信通過串口通信模塊實(shí)現(xiàn),。串口通信模塊包括波特率發(fā)生器、發(fā)送器和接收器3個(gè)子模塊,。波特率發(fā)生器模塊根據(jù)串口協(xié)議,,負(fù)責(zé)對(duì)系統(tǒng)時(shí)鐘(50 MHz)進(jìn)行5 208個(gè)計(jì)數(shù)定時(shí),分頻得到讀寫波特率9 600 b/s(1×5 208/50 MHz≈1/9 600 s)。

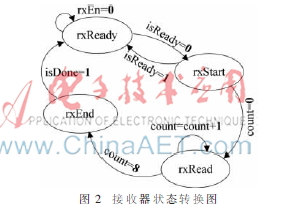

發(fā)送器和接收器屬于串口通信模塊,,主要負(fù)責(zé)接收上位機(jī)的控制命令并根據(jù)協(xié)議反饋握手信號(hào),。本串口模塊的幀數(shù)據(jù)每隔1個(gè)讀寫時(shí)鐘讀寫1位,遵循讀寫次序?yàn)?位起始位,、8位數(shù)據(jù)位,、1位校驗(yàn)位與1位停止位[6]。模塊采用狀態(tài)機(jī)的方式來實(shí)現(xiàn),。以接收器為例,,分別以rxReady、rxStart,、rxRead,、rxEnd標(biāo)識(shí) 4個(gè)狀態(tài)。圖2為接收器狀態(tài)轉(zhuǎn)換圖,, 狀態(tài)rxReady判斷信號(hào)rxEn為低電平就決定狀態(tài)機(jī)的開始,,并進(jìn)入rxStart狀態(tài),判斷信號(hào)isReady為低電平就標(biāo)記幀數(shù)據(jù)的起始位并進(jìn)入狀態(tài)rxRead,,利用計(jì)數(shù)器count循環(huán)讀取8位有效數(shù)據(jù),,最后狀態(tài)rxEnd負(fù)責(zé)延時(shí)兩個(gè)讀寫時(shí)鐘信號(hào)而忽略校驗(yàn)位和停止位,并輸出isDone接收完畢信號(hào),。數(shù)據(jù)接收完后,,狀態(tài)機(jī)重新進(jìn)入rxReady狀態(tài)等待下一個(gè)幀數(shù)據(jù)的接收。

2.2 VGA時(shí)序掃描模塊

本模塊中主要是通過對(duì)系統(tǒng)時(shí)鐘進(jìn)行PLL鎖相倍頻得到VGA的掃描時(shí)鐘[7],,再通過行同步和場(chǎng)同步信號(hào)控制CRT顯示器的陰極射線槍發(fā)射電子束,,按設(shè)定的時(shí)序打在涂有熒光粉的熒光屏上,產(chǎn)生紅綠黃三基色,,合成1個(gè)彩色像素,。掃描從屏幕左上角頂點(diǎn)開始,從左往右,,從上到下逐點(diǎn)掃描,。每掃描完一行,電子束需要回到屏幕的左邊下一行的起始點(diǎn),,此時(shí)就要用行同步信號(hào)對(duì)電子束消隱,,避免電子束損壞屏幕圖像;掃描完所有行,,再由場(chǎng)同步信號(hào)進(jìn)行消隱,,讓電子束重新回到屏幕左上角頂點(diǎn),同時(shí)需要行消隱,,準(zhǔn)備下一場(chǎng)的掃描,。VGA顯示器有800×600@60 Hz,、1 024×768@85 Hz等多種顯示標(biāo)準(zhǔn),,以1 024×768@85 Hz說明VGA時(shí)序掃描的原理,,此VGA標(biāo)準(zhǔn)下時(shí)序技術(shù)參數(shù)如表1所示[7]。

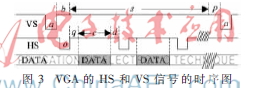

行同步信號(hào)HS和場(chǎng)同步信號(hào)VS的時(shí)序圖如圖3所示,。HS先拉低96個(gè)脈沖周期(以o表示)后再被拉高,,即行消隱時(shí)間;經(jīng)過208個(gè)脈沖(以q表示)后,,DATA數(shù)據(jù)有效,,即顯示器開始掃描1 024個(gè)列像素點(diǎn)(以c表示),掃描完成到下一次HS再次被拉低,,中間經(jīng)過48個(gè)時(shí)鐘脈沖(以d表示)[8],。掃描一行的數(shù)據(jù)幀長(zhǎng)為1 376。同樣,,VS類似HS的掃描方式,。VS先拉低3個(gè)行周期(以a表示)后再被拉高,延遲36個(gè)行周期(以b表示)后行再被拉低,,這樣開始掃描這一幀的數(shù)據(jù),,經(jīng)過1個(gè)行周期(以p表示),完成全幀掃描后VS再次被拉低重復(fù)上述過程,。

2.3 刺激圖像描述模塊

本模塊把顯示屏看作一個(gè)直角坐標(biāo)系,,原點(diǎn)在屏幕左上角,通過列計(jì)數(shù)器Hcnt和行計(jì)數(shù)器Vcnt,,定義掃描有效顯示區(qū)域的行和列坐標(biāo)變量Haddr和Vaddr,,通過直接對(duì)不同坐標(biāo)地址賦予不同的顏色值,產(chǎn)生視覺誘發(fā)電位實(shí)驗(yàn)所需刺激圖像,,如水平光柵,、垂直光柵和棋盤格等。

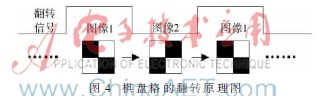

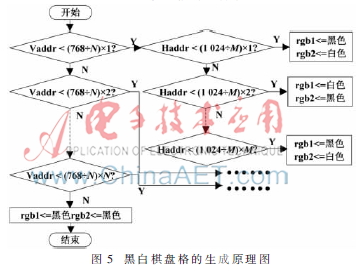

以棋盤格刺激圖像為例,,刺激器是通過生成同位置黑白相反的兩幅棋盤格圖像,,按照翻轉(zhuǎn)信號(hào)的高低電平變化將兩幅棋盤格RGB信號(hào)輪流發(fā)送給VGA端口。如圖4所示,,翻轉(zhuǎn)信號(hào)在高電平時(shí)顯示圖像1,,反之,在低電平時(shí)顯示圖像2,,因此實(shí)現(xiàn)兩幅棋盤格翻轉(zhuǎn)的效果,。棋盤格生成流程如圖5所示,圖中M,、N分別代表棋盤格的水平和垂直的格數(shù),,寄存器rgb1和rgb2分別負(fù)責(zé)寄存兩幅棋盤格中不同位置的顏色值,。

2.4 刺激率控制模塊

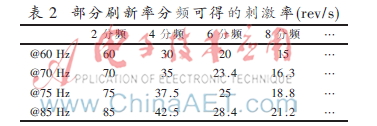

一個(gè)翻轉(zhuǎn)周期(cycle)包括兩個(gè)顏色相反的圖像翻轉(zhuǎn),而翻轉(zhuǎn)頻率指每秒鐘翻轉(zhuǎn)(reversal)的次數(shù)(rev/s),。兩者關(guān)系可以表示為1 Hz相當(dāng)于2 rev/s[2],。本刺激器中刺激率指每秒的翻轉(zhuǎn)次數(shù),是通過對(duì)VGA時(shí)序掃描模塊產(chǎn)生的場(chǎng)同步信號(hào)分頻得到,。場(chǎng)同步信號(hào)即VGA工業(yè)技術(shù)上的刷新率,。如圖6所示,翻轉(zhuǎn)信號(hào)和觸發(fā)信號(hào)產(chǎn)生原理是通過捕捉VS的下降沿時(shí)刻,,本模塊就按設(shè)定的分頻數(shù)生成一個(gè)方波信號(hào),,即翻轉(zhuǎn)信號(hào)。同時(shí),,在方波信號(hào)發(fā)生高低電平變換時(shí)刻,,即圖像每次翻轉(zhuǎn)時(shí)同步產(chǎn)生一個(gè)脈沖信號(hào),即觸發(fā)信號(hào),。這樣的實(shí)現(xiàn)方式保證了VS和翻轉(zhuǎn)信號(hào)的時(shí)鐘同源,,從而確保刺激圖像的正確顯示。比如,,60 Hz二分頻得30 Hz(60 rev/s),。由VESA公布的VGA時(shí)序[7], 表2舉例部分刷新率分頻可得的刺激率,。由表2可看出本刺激器已可實(shí)現(xiàn)高于30 rev/s的刺激率,,并隨著得到更高刷新率的時(shí)序技術(shù)參數(shù),就能實(shí)現(xiàn)更高的刺激率,。

3 刺激器測(cè)試結(jié)果

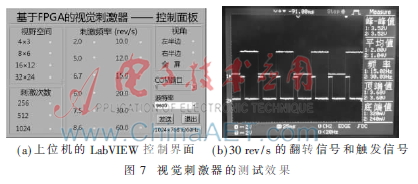

本文選擇顯示標(biāo)準(zhǔn)為1 024×768@60 Hz進(jìn)行測(cè)試,,通過JTAG口把編譯成功的FPGA程序燒錄到板上Flash芯片中,采用19寸CRT顯示器(EIZO T761)作為刺激視屏,。

測(cè)試結(jié)果如圖7所示,,圖7(a)是上位機(jī)的控制界面,參數(shù)選擇包括視角,、視野空間,、刺激次數(shù)和刺激率。圖7(b)為高刺激率30 rev/s時(shí)示波器的檢測(cè)情況,,示波器通道1顯示翻轉(zhuǎn)信號(hào)波形,,通道2顯示觸發(fā)信號(hào)波形,通道1高低電平切換時(shí)刻與通道2高電平開始時(shí)刻完全一致,,這說明了圖像刺激與觸發(fā)信號(hào)完全保持同步性,。

4 穩(wěn)態(tài)視覺誘發(fā)電位測(cè)試實(shí)驗(yàn)

為測(cè)試本視覺刺激器在高刺激率下的有效性,本文進(jìn)行了一個(gè)高刺激率的視覺誘發(fā)電位測(cè)試實(shí)驗(yàn),。

實(shí)驗(yàn)方法和步驟均嚴(yán)格按照視覺誘發(fā)電位實(shí)驗(yàn)標(biāo)準(zhǔn)要求[9],,利用本刺激器生成20,、30和60 rev/s等3個(gè)高頻刺激信號(hào),對(duì)1名受試者進(jìn)行以上3個(gè)高刺激率的視覺誘發(fā)電位測(cè)試實(shí)驗(yàn),。文獻(xiàn)[2]提到,,SSVEP波形是一個(gè)類似正弦曲線的波形,且頻率固定,。利用MATLAB處理通過SynAmps2系統(tǒng)采集所得數(shù)據(jù)并分別畫出SSVEP波形圖,,如圖8所示。從圖可清晰看出,,3個(gè)SSVEP波形都是類似正弦曲線的周期性波形,即受試者在3個(gè)高刺激率下,,視覺系統(tǒng)都有效地誘發(fā)出視覺穩(wěn)態(tài)反應(yīng),。

由刺激器測(cè)試結(jié)果和視覺測(cè)試實(shí)驗(yàn)證明,本文設(shè)計(jì)的基于FPGA的高頻視覺刺激控制器能滿足穩(wěn)態(tài)視覺誘發(fā)電位的實(shí)驗(yàn)要求,,不但順利完成高刺激率下刺激圖像的準(zhǔn)確呈現(xiàn)及觸發(fā)信號(hào)的同步發(fā)送,,成功誘發(fā)出有效穩(wěn)態(tài)覺誘發(fā)電位,并且具有操作方便,、刺激模式豐富,、可擴(kuò)展性強(qiáng)的優(yōu)勢(shì)。

參考文獻(xiàn)

[1] 黎宇飛,,劉技輝,,陳曉雷,等.不同刺激野的圖形翻轉(zhuǎn)視覺誘發(fā)電位[J].法醫(yī)學(xué)雜志,,2009,,25(1):15-18.

[2] ALMUDENA C,PAULA P A,,CAMPO P,,et al.Steady-statevisual evoked potentials can be explained by temporal superposition of transient event-related responses[J].Plos One,2011,,6(1):e14543.

[3] BOBAK P,,F(xiàn)RIEDMAN R.Visual evoked potentials to multi-ple temporal frequencies.Use in the differential diagnosis ofoptic neuropathy[J].Arch.of Ophthalmol,1988,,106(7):936-940.

[4] HERRMANN C S.Human EEG responses to 1-100 Hz flicker: resonance phenomena in visual cortex and their potential correlation to cognitive phenomena[J].Experimental Brain Research,,2001,137(3-4):346-353.

[5] 程光輝,,石銳,,何慶華.Windows環(huán)境下腦機(jī)接口視覺刺激器的設(shè)計(jì)[J].計(jì)算機(jī)工程與應(yīng)用,2006,,42(13):175-177,,193.

[6] 王永成,,黨源源,徐抒巖,,等.基于cpld實(shí)現(xiàn)dsp的uart設(shè)計(jì)研究[J].電子器件,,2008,31(3):1066-1068,,1072.

[7] Video Electronics Standards Association.VESA and industry standards and guidelines for computer display monitor timing[Z].2004.

[8] 姜世杰,,余紅英,洪永學(xué),,等.基于FPGA的VGA接口驅(qū)動(dòng)技術(shù)[J].電子測(cè)試,,2012(12):29-32,71.

[9] ODOM J V,,BACH M,,BRIGELL M,et al.ISCEV standard for clinical visual evoked potentials (2009update)[J].Docu-menta Ophthalmolgical,,2010,,120(1):111-119.