文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2015)01-0071-04

0 引言

隨著高速數(shù)字通信技術(shù)的發(fā)展,傳統(tǒng)的低速采樣技術(shù)已難以滿足寬帶、超寬帶雷達(dá)等領(lǐng)域?qū)Ω咚俑呔葦?shù)據(jù)采集的需求[1]。而且在航空、工業(yè)應(yīng)用中對(duì)數(shù)據(jù)采集設(shè)備的采樣率和精度要求也越來(lái)越高,高速ADC數(shù)據(jù)采集系統(tǒng)的應(yīng)用需求越來(lái)越廣泛。雖然現(xiàn)有的單片ADC速度有了很大提高,但是受現(xiàn)階段器件制造工藝的限制,使得其難以在高采樣的同時(shí)保持高的精度。傳統(tǒng)的高速電子開關(guān)雙DAC合成轉(zhuǎn)換技術(shù)由于高速電子開關(guān)限制使得其不能廣泛應(yīng)用[2],而并行多通道技術(shù)的出現(xiàn)為解決數(shù)據(jù)采集系統(tǒng)的采樣率低的問(wèn)題提供了技術(shù)支持,其也可稱為時(shí)間交替采樣技術(shù)[3],即前端并行逐次采樣后端串行多路復(fù)用。但是由于各通道的不一致性會(huì)產(chǎn)生3種失配誤差(偏移誤差、時(shí)延誤差和增益誤差)[4-6],誤差如果不進(jìn)行矯正會(huì)影響整個(gè)采集系統(tǒng)的性能。

因此,針對(duì)傳統(tǒng)數(shù)據(jù)采集系統(tǒng)采樣率低、誤差大的問(wèn)題,本文設(shè)計(jì)了一種基于FPGA與DSP相結(jié)合的高速數(shù)據(jù)采集系統(tǒng),其可實(shí)現(xiàn)信號(hào)的1 GS/s高速采樣及失配誤差的修正,使系統(tǒng)在高速采集的同時(shí)保持高的性能。

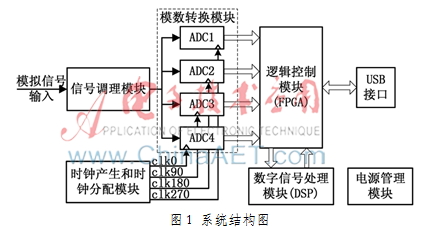

1 系統(tǒng)總體設(shè)計(jì)

根據(jù)時(shí)間交替采樣系統(tǒng)的功能和原理,本文將整個(gè)系統(tǒng)劃分為6個(gè)主要模塊:信號(hào)調(diào)理模塊、時(shí)鐘產(chǎn)生和分配模塊、模數(shù)轉(zhuǎn)換模塊、FPGA邏輯控制模塊、DSP數(shù)字信號(hào)處理模塊和電源管理模塊。其主要結(jié)構(gòu)框圖如圖1所示,系統(tǒng)的基本工作原理:寬帶模擬信號(hào)經(jīng)過(guò)信號(hào)輸入模塊的基本調(diào)理后,模數(shù)轉(zhuǎn)換模塊完成其輸出的高質(zhì)量模擬信號(hào)的并行采樣,邏輯控制模塊則完成高速采樣數(shù)據(jù)的接收和緩存等預(yù)處理,最后通過(guò)數(shù)字信號(hào)處理模塊實(shí)現(xiàn)數(shù)據(jù)的檢驗(yàn)和誤差矯正。

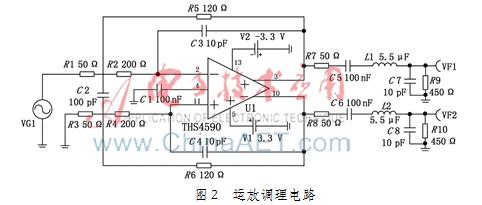

1.1 信號(hào)調(diào)理電路

在高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)中,需要給ADC模數(shù)轉(zhuǎn)換模塊提供高質(zhì)量的輸入信號(hào),以便實(shí)現(xiàn)信號(hào)的高精度轉(zhuǎn)換和后期的信號(hào)處理。因此,在模擬信號(hào)輸入系統(tǒng)之前,需要完成基本的調(diào)理過(guò)程,包括放大和濾波。本文比較TI公司各種運(yùn)算放大器,選用了THS45xx系列中的THS4509高速低噪聲寬帶差分運(yùn)算放大器。其具有600 MHz的小信號(hào)帶寬,當(dāng)輸入頻率為10 MHz 時(shí),2階諧波失真為-104 dBc、3階諧波失真為-108 dBc的特點(diǎn),能夠滿足系統(tǒng)的要求。利用TI公司的FilterPro濾波器軟件和TINA-TI仿真軟件完成信號(hào)調(diào)理電路的設(shè)計(jì)如圖2所示。

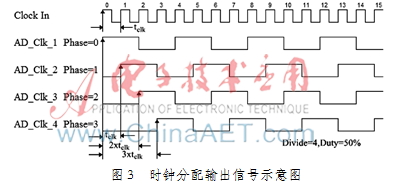

1.2 時(shí)鐘產(chǎn)生和分配

時(shí)鐘產(chǎn)生和分配模塊是實(shí)現(xiàn)并行多通道采樣技術(shù)的關(guān)鍵之一,為了實(shí)現(xiàn)1 GHz的采樣率,需要提供4路250 MHz頻率且相移相差90°的高質(zhì)量時(shí)鐘信號(hào)(clk0、clk90、clk180、clk270)。如果采用4個(gè)分離的時(shí)鐘驅(qū)動(dòng)芯片來(lái)分別驅(qū)動(dòng)4個(gè)ADC芯片,時(shí)鐘相位的延時(shí)難以準(zhǔn)確實(shí)現(xiàn),因此本文在設(shè)計(jì)中采用了集成壓控振蕩器的鎖相環(huán)芯片來(lái)產(chǎn)生1 GHz的時(shí)鐘,再利用時(shí)鐘分配芯片生成4路250 MHz相移90°的時(shí)鐘信號(hào),作為ADC芯片的采樣時(shí)鐘。時(shí)鐘分配芯片輸出的時(shí)鐘信號(hào)如圖3所示。

鎖相環(huán)芯片選用了輸出頻率范圍為350~1 800 MHz的ADF4360-7,時(shí)鐘分配則采用能夠根據(jù)分頻系數(shù)對(duì)相位進(jìn)行調(diào)節(jié)的AD9510芯片。其都是ADI公司生產(chǎn)的高性能時(shí)鐘產(chǎn)生和分配芯片,能夠?qū)崿F(xiàn)模數(shù)轉(zhuǎn)換模塊對(duì)時(shí)鐘的要求。

1.3 模數(shù)轉(zhuǎn)換模塊

模數(shù)轉(zhuǎn)換模塊實(shí)現(xiàn)模擬信號(hào)到數(shù)字信號(hào)的轉(zhuǎn)換,其主要由4個(gè)ADC芯片構(gòu)成。考慮到無(wú)雜散動(dòng)態(tài)范圍(SFDR)、信噪比(SNR)、有效位數(shù)(ENOB)以及輸入信號(hào)的帶寬等指標(biāo)要求,選用了250 MS/s、8位的AD9480。當(dāng)其以250 MS/s的速度對(duì)19.7 MHz的正弦波采樣時(shí),只有-65 dBc的SFDR,47 dB的SNR,7.6位的ENOB。而且其模擬信號(hào)輸入的帶寬可達(dá)750 MHz,能夠滿足高速采樣和高帶寬輸入的要求。

1.4 FPGA邏輯控制

輸入的模擬信號(hào)經(jīng)過(guò)A/D轉(zhuǎn)換之后,需要將采樣的數(shù)據(jù)接收和緩存。本設(shè)計(jì)選用XLINX公司的XC3S500E來(lái)接收AD9480輸出的時(shí)鐘和數(shù)據(jù),完成數(shù)據(jù)采樣的時(shí)序和邏輯控制。控制單元將采樣的信號(hào)存放在內(nèi)部RAM中,在完成32 KB(8KB/路)數(shù)據(jù)存儲(chǔ)后產(chǎn)生DSP中斷信號(hào),通知DSP讀入數(shù)據(jù)進(jìn)行數(shù)據(jù)的檢驗(yàn)和誤差矯正。為了減小FPGA的工作的負(fù)荷,本文采用了數(shù)據(jù)分裂存儲(chǔ)技術(shù),即將AD輸出的250 MHz時(shí)鐘和采樣的數(shù)據(jù)分成兩路,每路以125 MHz的速度寫入FPGA內(nèi)部的FIFO中。

1.5 數(shù)據(jù)處理電路

本系統(tǒng)采用了TI公司的TMS320VC5509A定點(diǎn)數(shù)字信號(hào)處理器來(lái)處理采樣后的數(shù)據(jù),該芯片的EMIF(存儲(chǔ)器擴(kuò)展接口)結(jié)構(gòu)和DMA(直接內(nèi)存訪問(wèn))技術(shù)為高速數(shù)據(jù)傳輸提供了一種可能和可靠的通道。其CPU支持內(nèi)部總線結(jié)構(gòu),包括一個(gè)程序總線、3個(gè)數(shù)據(jù)讀取總線、兩個(gè)數(shù)據(jù)寫總線和額外的專用外圍總線。在一個(gè)單一的周期內(nèi),這些總線能夠?qū)崿F(xiàn)3個(gè)數(shù)據(jù)讀取和兩個(gè)數(shù)據(jù)寫的功能。同時(shí),能夠支持高達(dá)200 MHz時(shí)鐘頻率,而且具有兩個(gè)算術(shù)/邏輯單元。

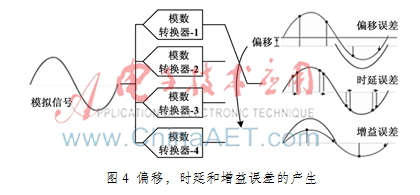

2 誤差分析

由于各通道電路布局布線和ADC芯片的不同,導(dǎo)致各通道采樣不可能完全一致,不可避免地產(chǎn)生通道失配誤差。如圖4所示,由于采樣時(shí)鐘延時(shí)精度不夠帶來(lái)的時(shí)延誤差,增益不一致導(dǎo)致的增益誤差,偏移不一致引起的偏移誤差。而誤差的存在是影響系統(tǒng)指標(biāo)的關(guān)鍵,通過(guò)對(duì)各誤差進(jìn)行時(shí)域或頻域分析能夠完成后期誤差的處理和矯正。

假設(shè)將M塊低速的模數(shù)轉(zhuǎn)換器組合成一個(gè)高速的AD。且其理想采樣間隔為T,低速AD的采樣間隔則為MT。g(t)為輸入的信號(hào)。則本系統(tǒng)高速AD采集的序列如下:

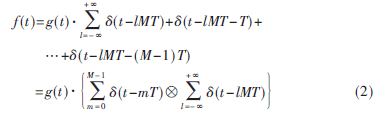

當(dāng)M個(gè)AD采樣時(shí),時(shí)間偏置理想下都是固定的,所有采樣點(diǎn)在時(shí)間上都是以MT為周期,因此理想情況下時(shí)間交替采樣信號(hào)的數(shù)學(xué)模型為:

2.1 偏移誤差

當(dāng)系統(tǒng)存在偏移誤差時(shí),設(shè)每個(gè)AD的偏移誤差為am,其中m=0,1,2,…,M-1,則實(shí)際的時(shí)域表現(xiàn)為:

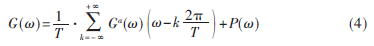

其主要包含兩部分:一部分是均勻采樣后的頻譜,另一部分為通道偏移不一致帶來(lái)的分量(P(t))。令P(?棕)為偏移誤差的傅里葉變換,輸入信號(hào)的傅里葉變換為Ga(?棕)(a代表模擬信號(hào)頻譜)。則含偏移誤差的采樣信號(hào)頻譜為:

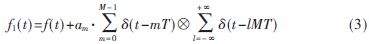

2.2 增益誤差

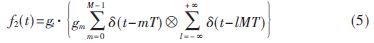

假設(shè)每個(gè)AD存在gm的增益誤差,其中m=0,1,2,…,M-1,則其時(shí)序表現(xiàn)為:

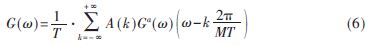

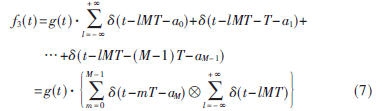

對(duì)其傅里葉變換得:

其中, M,…。式(6)即為增益幅度非均勻采樣信號(hào)的數(shù)字頻譜表達(dá)式。

M,…。式(6)即為增益幅度非均勻采樣信號(hào)的數(shù)字頻譜表達(dá)式。

2.3 時(shí)延誤差

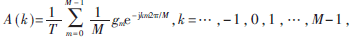

在實(shí)際的信號(hào)采集中,系統(tǒng)內(nèi)M個(gè)ADC實(shí)際采樣點(diǎn)的時(shí)間是不均勻的,故f3(t)實(shí)為:

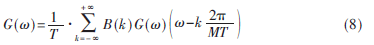

求出其頻域響應(yīng)為:

其中, 。

。

從以上分析中可以看出,3種誤差之間保持彼此獨(dú)立,互不干擾。當(dāng)采樣頻率fs固定后,時(shí)延誤差、增益誤差和偏移誤差引起的雜散在頻域的位置是固定的,是單獨(dú)作用的。

3 數(shù)據(jù)處理和誤差矯正

雖然系統(tǒng)存在這3種誤差,但是時(shí)延誤差僅與時(shí)鐘分配芯片有關(guān),一旦采樣率確定,這個(gè)誤差不會(huì)隨著輸入信號(hào)的改變而改變,增益誤差和偏移誤差僅與各AD的內(nèi)部結(jié)構(gòu)有關(guān)。因此,在實(shí)際中,可以通過(guò)數(shù)字信號(hào)處理的方式計(jì)算出誤差固定值,并加入誤差矯正模塊修正采樣的數(shù)據(jù),從而得到精確的結(jié)果。

為了消除誤差值,系統(tǒng)采用輸入正弦信號(hào)擬合法,完成誤差的矯正。誤差估計(jì)過(guò)程:輸入10 MHz的正弦波并進(jìn)行采樣,F(xiàn)PGA在完成一次采樣后,輸出中斷信號(hào),DSP讀出采樣的數(shù)據(jù)并完成偏移誤差、時(shí)延誤差和增益誤差的測(cè)量,最后得到每一路AD的偏移誤差ok、增益誤差gk、時(shí)延誤差ak后,就可以利用這3個(gè)參數(shù)對(duì)采樣后的信號(hào)進(jìn)行矯正。

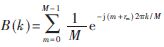

系統(tǒng)的誤差矯正流程如圖5所示,主要包括Farrow結(jié)構(gòu)的濾波器[7-8]、偏移消除模塊和增益消除模塊。其中時(shí)延誤差的矯正就是根據(jù)傅里葉變換的時(shí)移性質(zhì),如果時(shí)間誤差tk與采樣周期Ts的比值為ak,則對(duì)應(yīng)的頻域變化為頻域值乘以 。使采樣信號(hào)通過(guò)理想頻率響應(yīng)為

。使采樣信號(hào)通過(guò)理想頻率響應(yīng)為 的全通濾波器即可實(shí)現(xiàn)對(duì)時(shí)延誤差的校正。

的全通濾波器即可實(shí)現(xiàn)對(duì)時(shí)延誤差的校正。

將采樣得到的四路信號(hào)通過(guò)四組Farrow結(jié)構(gòu)的濾波器,濾波器對(duì)不同的AD采得的數(shù)據(jù)施以不同的延遲ak,從而補(bǔ)償了時(shí)延誤差。為了消除ADC間的偏置誤差,讓每路采樣后都減去其固有的直流偏置。而消除通道間的增益誤差的方法是,將其余三路信號(hào)都乘以與其中一路參考信號(hào)的幅度比gk,使后三路信號(hào)都與參考的增益保持一致。

4 試驗(yàn)結(jié)果

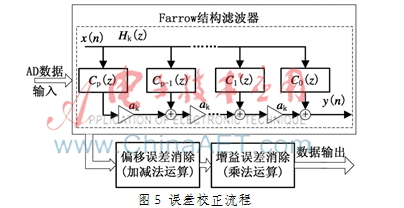

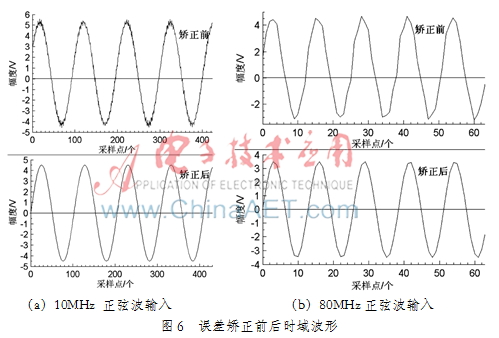

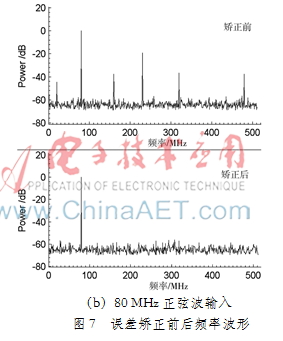

通過(guò)對(duì)采樣后存儲(chǔ)的數(shù)據(jù)進(jìn)行分析,并對(duì)比矯正前后的時(shí)域和頻域波形,可以得出系統(tǒng)的矯正效果。實(shí)驗(yàn)中將誤差矯正算法加入到DSP中,分別輸入10 MHz正弦波和80 MHz正弦波測(cè)試誤差矯正前后的時(shí)域及頻域效果,如圖6、7所示。從圖示中可以看出,采樣數(shù)據(jù)經(jīng)過(guò)矯正后,誤差明顯降低,而且波形質(zhì)量比矯正前效果好。由傅里葉變換數(shù)據(jù)的對(duì)稱性整個(gè)頻譜圖是以fs/2頻率為對(duì)稱軸的,因此,在頻譜圖中只取一半。本設(shè)計(jì)經(jīng)過(guò)多次測(cè)試,證明了基于時(shí)間交替采樣技術(shù)的高速采集系統(tǒng)的可行性和準(zhǔn)確性,能夠?qū)崿F(xiàn)高速采集條件下的誤差矯正。

5 結(jié)論

本文介紹了一種基于FPGA+DSP的高速采樣系統(tǒng),并應(yīng)用了時(shí)間交替采樣的技術(shù)實(shí)現(xiàn)了采樣速率的提高。在硬件設(shè)計(jì)上,結(jié)合了可編程邏輯器件的靈活性和數(shù)字信號(hào)處理器的高速信號(hào)處理能力。通過(guò)對(duì)偏移誤差、時(shí)延誤差和增益誤差的分析,解決了高速采樣系統(tǒng)中存在的誤差問(wèn)題,實(shí)現(xiàn)了采樣數(shù)據(jù)的矯正處理。該設(shè)計(jì)已可實(shí)現(xiàn)采樣率為1 GS/s的4路ADC并行采樣,并能完成誤差的矯正,且矯正后的指標(biāo)優(yōu)于矯正前。

參考文獻(xiàn)

[1] 張思杰,趙泰,汪振興,等.基于FPGA的USB接口數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2011,37(5):98-100.

[2] BLACK W C,HODGES D A.Time interleaved converter arrays[M].IEEE Journal of Solid-State Circuits,1980,15(6):1022-1029.

[3] 孔路平,姚國(guó)英.一種提高DAC采樣率的新方法[J].電子測(cè)量技術(shù),2008,31(9):21-24.

[4] VOGEL C.The impact of combined channel mismatch in time-interleaved ADCs[J].IEEE Trans.Instrum.Meas,2005,54(1):415-427.

[5] 朱子翰,呂幼新.時(shí)間交替采樣系統(tǒng)的誤差測(cè)量與FPGA實(shí)現(xiàn)[J].電子測(cè)量技術(shù),2011,34(3):54-56.

[6] KUROSAWA N,KOBAYASHI H,MARUYAMA K,et al.Explicit analysis of channel mismatch effects in time-inter-leaved ADC systems[J].IEEE Transactions on Circuits and System I:Fundamental Theory and Applications,2001,48(3):261-271.

[7] FARROW C W.A continuously variable digital element[C].Proc.IEEE Int.Symp.Circuits Systems,(ICAS-88),1988,3:2642-2645.

[8] 劉艷茹,田書林,王志剛,等.一種基于Farrow濾波器的并行采樣時(shí)間誤差校正[J].電子測(cè)量與儀器學(xué)報(bào),2010,24(1):50-54.