摘 要: 數(shù)據(jù)采樣精度和采樣速率是A/D轉(zhuǎn)換的重要技術(shù)指標(biāo)。目前受半導(dǎo)體工藝技術(shù)的限制,高采樣精度的A/D芯片一般具有較低的采樣速率。本文提出一種時(shí)間交替ADC采樣技術(shù),通過在時(shí)域上多通道并行交替采樣,使采樣速率達(dá)到原來單片ADC的多倍。最后進(jìn)行多路交替采樣試驗(yàn),結(jié)果驗(yàn)證了該方法的正確性。

關(guān)鍵詞: 時(shí)間交替采樣;模數(shù)轉(zhuǎn)換;并行處理

0 引言

高速數(shù)據(jù)采集廣泛應(yīng)用于雷達(dá)、電子對(duì)抗、航空航天、導(dǎo)彈測(cè)控、儀器儀表、圖像處理、高性能控制器等領(lǐng)域,是現(xiàn)代電子設(shè)備中的技術(shù)關(guān)鍵。隨著計(jì)算機(jī)、通信和微電子技術(shù)的高速發(fā)展,人們不斷地對(duì)數(shù)據(jù)采集的速度和精度提出更高的要求,然而受芯片制造工藝的限制,超高速ADC采樣芯片的特性難以滿足高性能設(shè)備的需求[1]。采用多片高速ADC芯片并行交替采樣,實(shí)現(xiàn)超高速和高精度采樣,是解決此類問題最為有效的方法。本文利用N路高速ADC芯片對(duì)一路模擬信號(hào)并行交替采樣,然后對(duì)各路采樣得到的數(shù)據(jù)依次拼接,使得整個(gè)系統(tǒng)采樣頻率為單塊A/D芯片的N倍,在保持高精度的同時(shí)成倍地提高系統(tǒng)的采樣率,達(dá)到超高速的采樣目的。

1 高速并行數(shù)據(jù)采集系統(tǒng)結(jié)構(gòu)

本設(shè)計(jì)首先將一路10 MHz、10 Vpp的高頻模擬信號(hào)分別接入兩路12位A/D芯片的輸入接口,然后通過FPGA對(duì)兩路A/D芯片分別以50 MHz的速率并行交替采樣10 ms,將轉(zhuǎn)換的采樣數(shù)據(jù)存儲(chǔ)到SDRAM中,存儲(chǔ)的數(shù)據(jù)可以通過串行接口送到上位機(jī)處理,整個(gè)系統(tǒng)硬件結(jié)構(gòu)如圖1所示。

10 MHz正弦波信號(hào)通過信號(hào)發(fā)生器產(chǎn)生,該信號(hào)的輸出頻率及幅值大小可以根據(jù)實(shí)際需要進(jìn)行調(diào)整。模數(shù)轉(zhuǎn)換芯片采用ADI的AD9226芯片,AD9226是一款單路、12位、65 MS/s模數(shù)轉(zhuǎn)換器,采用單電源供電,內(nèi)置一個(gè)片內(nèi)高性能采樣保持放大器和基準(zhǔn)電壓源。它采用多級(jí)差分流水線架構(gòu),數(shù)據(jù)速率達(dá)65 MS/s,在整個(gè)工作溫度范圍內(nèi)保證無失碼[2]。FPGA芯片采用Altera公司所生產(chǎn)的Cyclone IV系列芯片EP4E6F17C8,其具有低成本、低功耗的FPGA系統(tǒng)構(gòu)架;內(nèi)部具有大量嵌入式存儲(chǔ)器和邏輯單元,可以通過NIOS軟件構(gòu)成軟核處理器。本設(shè)計(jì)外部存儲(chǔ)器選擇SDRAM,其型號(hào)為HY57V2562GTR,容量為256 Mit(16 M×16 bit),具有16 bit總線。本設(shè)計(jì)通過NIOS可以生成EP4E6F17C8與外部存儲(chǔ)器的接口,包括有SDR、DDR、DDR2等。

一路模擬信號(hào)同時(shí)輸入至兩路A/D轉(zhuǎn)換芯片輸入端,為了使信號(hào)相位相同,可以通過PCB的等長走線來實(shí)現(xiàn)。由于本設(shè)計(jì)A/D轉(zhuǎn)換要求輸入電壓在1~3 V之間,所以需要將信號(hào)發(fā)生器的±5 V信號(hào)進(jìn)行調(diào)理。AD8065放大器為電壓反饋型放大器,提供FET輸入,工作噪聲極低(7.0 nV/Hz和0.6 fA/Hz),輸入阻抗較高,帶寬為145 MHz,適合各種應(yīng)用[3]。VREF為AD9226輸出+2.5 V參考電壓,通過NE5532二級(jí)運(yùn)放構(gòu)成增益為-1的電壓跟隨,最終輸出-2.5 V的參考電壓,參考電壓通過AD8065進(jìn)行差分運(yùn)算。增益調(diào)理電路如圖2所示,通過運(yùn)算放大器AD8065將交流信號(hào)調(diào)理至1~3 V送至模數(shù)轉(zhuǎn)換芯片的輸入端。

模數(shù)轉(zhuǎn)換芯片選擇AD9226,本設(shè)計(jì)采用SSOP封裝形式,AD9226的D0~D11引腳為模數(shù)轉(zhuǎn)換的數(shù)字輸出量,當(dāng)時(shí)鐘信號(hào)送至AD9226的1腳時(shí),將觸發(fā)一次模數(shù)轉(zhuǎn)換,在模數(shù)轉(zhuǎn)換中D0~D10為數(shù)據(jù)位,而D11為符號(hào)位,OTR為模數(shù)轉(zhuǎn)換的溢出標(biāo)志。由于A/D轉(zhuǎn)換的電路比較簡單,這里就不列舉,詳細(xì)內(nèi)容請(qǐng)參閱其數(shù)據(jù)手冊(cè)。

整個(gè)系統(tǒng)采用FPGA控制,與相對(duì)順序操作的單片機(jī)或者ARM控制相比,其具有無法比擬的優(yōu)勢(shì)。FPGA采用的是并行處理的可編程邏輯器件,通過FPGA實(shí)現(xiàn)數(shù)據(jù)的高速采樣、讀取、存儲(chǔ)及處理等操作。EP4CE6F17C8的外部時(shí)鐘源為50 MHz,可以通過PLL進(jìn)行倍頻。由于FPGA內(nèi)部沒有程序存儲(chǔ)單元,所以需要外部擴(kuò)展,本設(shè)計(jì)采用M25P16(或EPCS16),其實(shí)質(zhì)是一個(gè)容量為16 Mbit的串行Flash芯片,這對(duì)于存儲(chǔ)FPGA中的程序綽綽有余,同時(shí)還可以存儲(chǔ)軟核NIOS II的應(yīng)用程序。

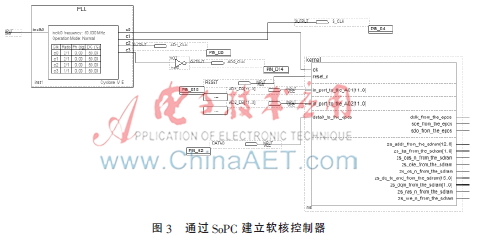

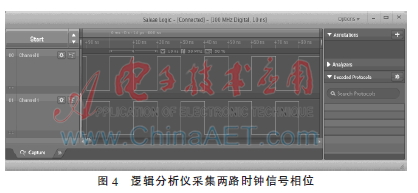

在本設(shè)計(jì)中,F(xiàn)PGA與A/D轉(zhuǎn)換模塊接口、存儲(chǔ)器模塊接口以及PLL時(shí)鐘信號(hào)都可以通過開發(fā)軟件Quartus在SoPC(System on a Programmable Chip)中建立。SoPC用可編程邏輯技術(shù)把整個(gè)系統(tǒng)放到一塊硅片上,用于嵌入式系統(tǒng)的研究和電子信息處理,是一種特殊的嵌入式系統(tǒng)。它是片上系統(tǒng)(SoC),即由單個(gè)芯片完成整個(gè)系統(tǒng)的主要邏輯功能,但它又不是簡單的SoC,它具有靈活的設(shè)計(jì)方式,可裁減、可擴(kuò)充、可升級(jí),并具備軟硬件在系統(tǒng)可編程的功能。通過Quartus軟件在SoPC上建立的軟核如圖3所示,PLL為鎖相環(huán),輸出C0~C3四路時(shí)鐘信號(hào),C0作為軟核kernel的時(shí)鐘源。由于SDRAM要求時(shí)鐘頻率為100 MHz,而FPGA外部時(shí)鐘信號(hào)為50 MHz,所以需要對(duì)C1進(jìn)行2倍頻。C2和C3為兩路A/D采樣的時(shí)鐘信號(hào),由于相位相差180度,可以通過時(shí)鐘相位偏移設(shè)置,本文在C3的輸出信號(hào)線上加入一個(gè)非門,來實(shí)現(xiàn)兩路時(shí)鐘信號(hào)的180度相位偏轉(zhuǎn),用邏輯分析儀采集的兩路時(shí)鐘信號(hào)相位波形如圖4所示。AD1_DB[11..0]和AD2_DB[11..0]將外部兩路A/D采樣轉(zhuǎn)換后的數(shù)據(jù)輸入FPGA。

兩路A/D采樣精度為12 bit,同時(shí)以50 MHz的速率交替采樣,則數(shù)據(jù)量將達(dá)到1.2 Gb/s,這個(gè)數(shù)據(jù)量是相當(dāng)大的,目前計(jì)算機(jī)普通數(shù)據(jù)傳輸速率遠(yuǎn)達(dá)不到此要求。所以本設(shè)計(jì)以微秒為單位,只采集有限個(gè)點(diǎn)的數(shù)據(jù),將采集的數(shù)據(jù)暫存入SDRAM中。兩路A/D轉(zhuǎn)換有嚴(yán)格的時(shí)序關(guān)系,由圖3可知AD2的采樣時(shí)鐘信號(hào)比AD1的延遲180度,為了保持信號(hào)嚴(yán)格時(shí)序,系統(tǒng)在讀取AD1當(dāng)前采樣數(shù)據(jù)的同時(shí),讀取前一次AD2的采樣數(shù)據(jù),而數(shù)據(jù)存儲(chǔ)格式為AD1_DB[11..0]+AD2_DB[11..0]共計(jì)24位,低位存AD1的數(shù)據(jù),高位存AD2的數(shù)據(jù)(由于各通道采樣時(shí)間間隔為20 ns,而相位相差180度,所以在數(shù)據(jù)采集過程中沒有包含時(shí)間量)。等到采樣結(jié)束后,將采集的數(shù)據(jù)轉(zhuǎn)換為字符串,通過串行接口送至上位機(jī)進(jìn)行分析處理。整個(gè)軟件通過NIOS調(diào)用Quartus軟核,其中A/D采樣及SDRAM的讀寫比較簡單,這里就不做詳細(xì)介紹,而串行接口的讀寫可以參考相應(yīng)的例程資料。

2 實(shí)驗(yàn)數(shù)據(jù)分析及結(jié)論

為了驗(yàn)證實(shí)驗(yàn)的有效性,通過信號(hào)發(fā)生器在系統(tǒng)的輸入端輸入一個(gè)10 Vpp、10 MHz的正弦信號(hào),系統(tǒng)對(duì)該信號(hào)連續(xù)采樣1 000組數(shù)據(jù)存入SDRAM,然后將數(shù)據(jù)通過串口發(fā)送至上位機(jī)。得到的兩路數(shù)據(jù)最終以Excel數(shù)據(jù)格式存儲(chǔ)。隨機(jī)提取連續(xù)的100組采樣數(shù)據(jù),通過MATLAB對(duì)數(shù)據(jù)進(jìn)行處理,將數(shù)據(jù)轉(zhuǎn)換成連續(xù)的點(diǎn)。各通道采樣點(diǎn)的連線與整合后的采樣點(diǎn)連線如圖5所示,MATLAB數(shù)據(jù)處理程序如下:

x1=caiyang1(:,1);

y1=caiyang1(:,2)/2048*5;

subplot(3,1,1);

title(′一通道采樣點(diǎn)連線′);

line(x1,y1,′Marker′,′+′);

grid on;

x2=caiyang2(:,1);

y2=caiyang2(:,2)/2048*5;

subplot(3,1,2);

title(′二通道采樣點(diǎn)連線′);

line(x2,y2,′Marker′,′*′)

grid on;

x3=honghe(:,1);

y3=honghe(:,2)/2048*5;

subplot(3,1,3)

title(′整合后采樣點(diǎn)連線′);

line(x3,y3,′Marker′,′.′)

grid on;

通過圖5可知,整合后的交替高速數(shù)據(jù)采集系統(tǒng)的采樣精度有了大幅提高。所以,采用時(shí)間交替技術(shù)的并行數(shù)據(jù)采集系統(tǒng),能在保證采樣精度的情況下最大限度地提高采樣速度。在超高速數(shù)據(jù)采集系統(tǒng)的構(gòu)建上提出了一種新的解決方法,使得超高速數(shù)據(jù)采集成為可能,對(duì)超高速儀器儀表的研究發(fā)展具有重大的借鑒意義。

參考文獻(xiàn)

[1] 李玉生.超高速并行采樣模擬/數(shù)字轉(zhuǎn)換的研究[D].合肥:中國科學(xué)技術(shù)大學(xué),2007.

[2] ANALOG DEVICE. AD9226 DATA SHEET(Revision .0)[Z]. 2000.

[3] ANALOG DEVICE. AD8065/AD8066數(shù)據(jù)手冊(cè)(Revision.J)[Z]. 2010.