文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2015)01-0118-04

中文引用格式:魏漢明,劉文怡,關(guān)詠梅,張彥軍,張國(guó)佳.基于漢明碼校驗(yàn)的AES數(shù)據(jù)加密記錄器設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2015,41(01):118-121

0 引言

數(shù)據(jù)記錄器是遙測(cè)系統(tǒng)中重要的組成部分,可為飛行器的質(zhì)量評(píng)估及飛行器的技術(shù)改進(jìn)提供數(shù)據(jù)依據(jù)。近些年半導(dǎo)體技術(shù)高速發(fā)展,固態(tài)記錄器以成為飛行記錄器的發(fā)展趨勢(shì),在現(xiàn)有的固態(tài)存儲(chǔ)介質(zhì)中,基于NAND技術(shù)的非揮發(fā)性存儲(chǔ)器Flash(閃速存儲(chǔ)器)以其體積小、功耗低、密度大、編程和擦除速度快、成本低等優(yōu)點(diǎn)而被廣泛地運(yùn)用于各個(gè)領(lǐng)域[1]。

同時(shí)為了防止數(shù)據(jù)記錄器中的信息被對(duì)手截獲,需要對(duì)信息進(jìn)行保密防護(hù),常用的措施為采用加密編碼[2-3]。加密編碼對(duì)基于Nand Flash芯片的數(shù)據(jù)記錄器會(huì)產(chǎn)生一個(gè)問(wèn)題。Nand Flash芯片的物理特性使其在使用中有可能出現(xiàn)位翻轉(zhuǎn)的問(wèn)題,即在一定的數(shù)據(jù)塊中產(chǎn)生了一比特的誤碼,這個(gè)誤碼經(jīng)過(guò)加密編碼后會(huì)引起誤碼擴(kuò)散。如數(shù)據(jù)在采集后以16 B分組,經(jīng)加密編碼后存入Flash芯片中,若在Flash芯片中出現(xiàn)了位翻轉(zhuǎn)錯(cuò)誤,那么該位所在的128 b加密數(shù)據(jù)在解密后一般得不到原來(lái)的明文數(shù)據(jù),那么原來(lái)出現(xiàn)在1 B的誤碼經(jīng)加密后擴(kuò)散到了16 B中。由此可見(jiàn),在加密存儲(chǔ)系統(tǒng)中,對(duì)誤碼的控制設(shè)計(jì)尤為重要。漢明碼的二元線性分組碼中編碼效率高,簡(jiǎn)單實(shí)用,在分組數(shù)據(jù)內(nèi)能實(shí)現(xiàn)錯(cuò)誤檢測(cè)和1比特的誤碼糾正[4]。本文將研究數(shù)據(jù)記錄器的AES加密設(shè)計(jì)及基于漢明碼的誤碼控制設(shè)計(jì)。

1 系統(tǒng)方案設(shè)計(jì)

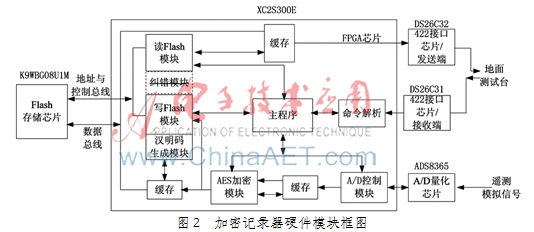

AES加密數(shù)據(jù)記錄器主要完成對(duì)遙測(cè)模擬信號(hào)的采集、加密及存儲(chǔ),同時(shí)嵌入漢明校驗(yàn)碼增強(qiáng)存儲(chǔ)的可靠性;記錄器中存儲(chǔ)的數(shù)據(jù)最后被讀取至計(jì)算機(jī)終端,完成解密與分析。記錄器不能與計(jì)算機(jī)終端直接通信,配套地面測(cè)試臺(tái)設(shè)備是計(jì)算機(jī)終端與數(shù)據(jù)記錄器通信的橋梁。在傳統(tǒng)方案中,誤碼的糾錯(cuò)工作在記錄器中完成,數(shù)據(jù)從Flash中讀出時(shí)首先要在記錄器中緩存,等到誤碼檢測(cè)與糾錯(cuò)工作完成后才能將糾錯(cuò)后的數(shù)據(jù)上傳給計(jì)算機(jī),這樣會(huì)大大降低了數(shù)據(jù)傳輸速度。本文設(shè)計(jì)的方案中將糾錯(cuò)工作交由計(jì)算機(jī)完成,這樣不僅能檢測(cè)和糾正NAND Flash芯片存儲(chǔ)的位翻轉(zhuǎn)錯(cuò)誤,減輕了硬件系統(tǒng)的工作量,保證了數(shù)據(jù)傳輸?shù)乃俣龋依糜?jì)算機(jī)能夠使糾錯(cuò)工作結(jié)果更直觀[5-6]。系統(tǒng)的工作方案如圖1所示。

AES加密數(shù)據(jù)記錄器以48 kHz的頻率對(duì)6路遙測(cè)模擬信號(hào)進(jìn)行采樣,然后將量化后的遙測(cè)數(shù)據(jù)分組加密,加密后的數(shù)據(jù)及生成的漢明校驗(yàn)碼寫(xiě)入NAND Flash芯片中。采樣芯片采用ADS8365芯片,單個(gè)芯片可并行實(shí)現(xiàn)6路差分通道的轉(zhuǎn)換,有益于小尺寸系統(tǒng)設(shè)計(jì);采樣精度可達(dá)16 bit。存儲(chǔ)芯片采用三星公司的4 GB容量NAND Flash芯片K9WBG08U1M。整個(gè)加密記錄器的系統(tǒng)設(shè)計(jì)框架如圖2所示。

2 關(guān)鍵技術(shù)實(shí)現(xiàn)

2.1 AES加密算法的FPGA實(shí)現(xiàn)

本文采用的密鑰長(zhǎng)度為128 b,狀態(tài)矩陣由4×4 B組成,則加密的迭代輪數(shù)為10,每一輪的步驟為:(1)字節(jié)代換(s盒替換),(2)行移位,(3)列混合(最后一輪沒(méi)有),(4)輪密鑰加。

字節(jié)代換即通過(guò)一個(gè)非線性的函數(shù),將原有字節(jié)替換成對(duì)應(yīng)字節(jié)的過(guò)程。其實(shí)際運(yùn)算操作為:首先將字節(jié)變換到GF(28)域上的乘法逆元,再對(duì)字節(jié)進(jìn)行一個(gè)仿射變換。字節(jié)代換可以簡(jiǎn)化為一個(gè)簡(jiǎn)單的查表操作,AES定義了一個(gè)S盒(及逆S盒),S盒是一個(gè)由16×16 B組成矩陣,矩陣共有256個(gè)元素(字節(jié))。查表時(shí),字節(jié)的高4位作為行地址x,低4位作為列地址y,指向S盒的第x行第y列的字節(jié)。為了簡(jiǎn)化硬件的工作,本文將采用官方S盒,且將S盒內(nèi)容初始化至FPGA的IP核ROM中。

行移位是一個(gè)簡(jiǎn)單的左循環(huán)移位操作。對(duì)4×4的狀態(tài)矩陣,第1行不移位,第2行左移1個(gè)字節(jié),第3行左移2個(gè)字節(jié),第4行左移3個(gè)字節(jié)即可。

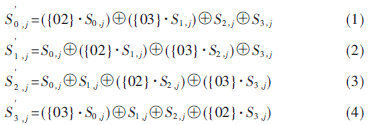

列混合是將狀態(tài)矩陣與一固定矩陣相乘,狀態(tài)矩陣每一列的更新方式如下式所示:

式中涉及的操作有加法(異或)和乘法,由于乘法在FPGA中直接實(shí)現(xiàn)較為復(fù)雜,需要將乘法運(yùn)算轉(zhuǎn)換為移位和加法運(yùn)算。在有限域GF(28)上,{02}乘以一字節(jié)b(x)=b7×7+b6×6+b5×5+b4×4+b3×3+b2×2+b1×1+b0×0,若該字節(jié)的最高位b7為0,則可直接對(duì)b(x)在字節(jié)內(nèi)左移1位,最低位補(bǔ)0即可;若最高位b7為1則需在移位后再與{1B}異或。{03}乘以一字節(jié)時(shí)則將{03}分解為{02}+{01}再進(jìn)行運(yùn)算即可。

輪密鑰加即將狀態(tài)矩陣與輪密鑰矩陣逐位異或即可。

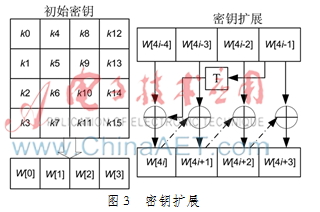

輪密鑰由初始密鑰經(jīng)過(guò)密鑰擴(kuò)展操作得來(lái)。初始密鑰由用戶制定,長(zhǎng)度為128 b,將其輸入到一個(gè)4×4的矩陣中,用數(shù)組W[i]表示密鑰中的某一列,則初始密鑰可用W[0]、W[1]、W[2]、W[3]4個(gè)數(shù)據(jù)表示;下一輪的擴(kuò)展密鑰可用W[4]、W[5]、W[6]、W[7]表示……依次,最后一輪的擴(kuò)展密鑰數(shù)據(jù)為W[40]、W[41]、W[42]、W[43]。各數(shù)組之間的關(guān)系為:

(1)若i非4的倍數(shù),則有:

W[i]=W[i-4]⊕W[i-1](5)

(2)若i為4的倍數(shù),則有:

W[i]=W[i-4]⊕T(W[i-1])(6)

式中T相當(dāng)與一個(gè)復(fù)雜的函數(shù),其具體的操作為:

①字循環(huán):將自變量循環(huán)左移1個(gè)字節(jié)。如數(shù)組[w0,w1,w2,w3]經(jīng)過(guò)字循環(huán)變換為[w3,w0,w1,w2]。

②字節(jié)代換:使用S盒對(duì)每個(gè)字節(jié)進(jìn)行代換。

③輪常量異或:將前兩步的結(jié)果與輪常量Rcon[j]進(jìn)行異或,j表示輪數(shù)。輪常數(shù)的內(nèi)容(4個(gè)字節(jié))如表1所示,密鑰擴(kuò)展過(guò)程如圖3所示。

用戶定義了初始密鑰后,由密鑰擴(kuò)展運(yùn)算就可以得到后續(xù)的10輪密鑰。為了簡(jiǎn)化硬件工作,密鑰擴(kuò)展工作可由計(jì)算機(jī)完成,然后將所有密鑰(共11×16=176 B)作為初始化文件載入FPGA ROM核中。這樣,F(xiàn)PGA對(duì)于密鑰的相對(duì)操作可簡(jiǎn)化為簡(jiǎn)單的查表運(yùn)算。

為了加快執(zhí)行速度,F(xiàn)PGA程序中采用流水線設(shè)計(jì)。根據(jù)AES加密算法的原理,把程序主要?jiǎng)澐譃檩喢荑€加、S盒替換、行變換、列混合、加密輸出等5個(gè)模塊。各模塊之間設(shè)由握手信號(hào)進(jìn)行通信,每個(gè)模塊只需完成自己的任務(wù)((1)AES加密步驟;(2)輸出指示信號(hào)和加密狀態(tài)(數(shù)據(jù)))即可。

2.2 漢明碼校驗(yàn)設(shè)計(jì)

漢明碼的FPGA實(shí)現(xiàn)較為簡(jiǎn)單,首先需要對(duì)數(shù)據(jù)進(jìn)行分組設(shè)計(jì)。由于使用的NAND Flash是4 KB每頁(yè)的結(jié)構(gòu),因此將一頁(yè)的4 KB數(shù)據(jù)分為一組。將4 KB數(shù)據(jù)看成是4 096(行)×8(列)的矩陣,數(shù)據(jù)在邊寫(xiě)入Flash時(shí)可邊產(chǎn)生漢明校驗(yàn)碼,完全不影響存數(shù)的速度,最終生成12 bit的行奇校驗(yàn)碼、12 bit的行偶校驗(yàn)碼、3 bit的列奇校驗(yàn)碼、3 bit的列偶校驗(yàn)碼,只需將這總共30 bit的校驗(yàn)碼寫(xiě)入Flash當(dāng)前頁(yè)的備用區(qū)即可。

行校驗(yàn)碼與列校驗(yàn)碼可以看成是獨(dú)立的,而奇校驗(yàn)碼與偶校驗(yàn)碼是互補(bǔ)的,行校驗(yàn)碼最終指示出錯(cuò)的“行”(字節(jié)),列校驗(yàn)碼最終指示出錯(cuò)的“列”(位),二者相結(jié)合最終能定位到整個(gè)分組數(shù)據(jù)中的某一出錯(cuò)位且糾錯(cuò)。

為了方便,以列校驗(yàn)碼的生成做示例。設(shè)列奇校驗(yàn)碼為L(zhǎng)_ECCo,列偶校驗(yàn)碼為L(zhǎng)_ECCe,則有:

L_ECCo[2]=byte_n[7]^byte_n[6]^byte_n[5]^byte_n[4]

(n=0,1……4 095)(7)

L_ECCo[1]=byte_n[7]^byte_n[6]^byte_n[3]^byte_n[2]

(n=0,1……4 095)(8)

L_ECCo[0]=byte_n[7]^byte_n[5]^byte_n[3]^byte_n[1]

(n=0,1……4 095)(9)

L_ECCe[2]=byte_n[3]^byte_n[2]^byte_n[1]^byte_n[0]

(n=0,1……4 095)(10)

L_ECCe[1]=byte_n[5]^byte_n[4]^byte_n[1]^byte_n[0]

(n=0,1……4 095)(11)

L_ECCe[0]=byte_n[6]^byte_n[4]^byte_n[2]^byte_n[0]

(n=0,1……4 095)(12)

計(jì)算機(jī)軟件讀取Flash中的數(shù)據(jù)時(shí)也會(huì)按照同樣的方式生成漢明校驗(yàn)碼,此時(shí)設(shè)列奇校驗(yàn)碼為L(zhǎng)_ECCo′,列偶校驗(yàn)碼為L(zhǎng)_ECCe′。計(jì)算機(jī)在數(shù)據(jù)分析前對(duì)數(shù)據(jù)進(jìn)行校驗(yàn),那么當(dāng)L_ECCo與L_ECCo′、L_ECCe與L_ECCe′分別完全相等時(shí)才認(rèn)定數(shù)據(jù)存儲(chǔ)及傳輸正常(這里只以列校驗(yàn)作說(shuō)明);若L_ECCo、L_ECCo′、L_ECCe、L_ECCe′ 4個(gè)參數(shù)的異或結(jié)果所有位都為1,那么數(shù)據(jù)出現(xiàn)了可糾正的錯(cuò)誤,出錯(cuò)的位地址由L_ECCo′與 L_ECCo的異或結(jié)果表示。

3 實(shí)驗(yàn)結(jié)果

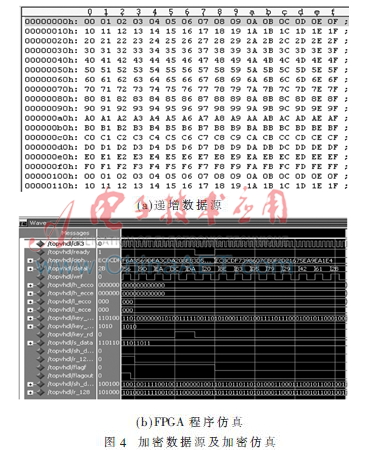

為了驗(yàn)證設(shè)計(jì)的正確性,對(duì)00~FF的循環(huán)遞增數(shù)據(jù)進(jìn)行加密存儲(chǔ),數(shù)據(jù)源如圖4(a)所示。數(shù)據(jù)加密過(guò)程及漢明校驗(yàn)碼生成程序仿真如圖4(b)所示。加密數(shù)據(jù)最后以4 KB為單位打包上傳給計(jì)算機(jī)。

同時(shí),在加密數(shù)據(jù)上傳到計(jì)算機(jī)時(shí),故意將數(shù)據(jù)中的某一位翻轉(zhuǎn),如第17 B(Byte16)的第4位(bit3),那么計(jì)算機(jī)收到的未校驗(yàn)的加密數(shù)據(jù)如圖5(a)所示,其中字節(jié)“C0”為誤碼字節(jié),直接對(duì)圖5(a)數(shù)據(jù)進(jìn)出解密,得到數(shù)據(jù)如圖5(b)所示。數(shù)據(jù)分析報(bào)告稱出現(xiàn)16 B的錯(cuò)誤。由此可知,由于一個(gè)加密字節(jié)的位翻轉(zhuǎn)錯(cuò)誤,經(jīng)過(guò)解密后擴(kuò)散到了原16 B的分組數(shù)據(jù)中。

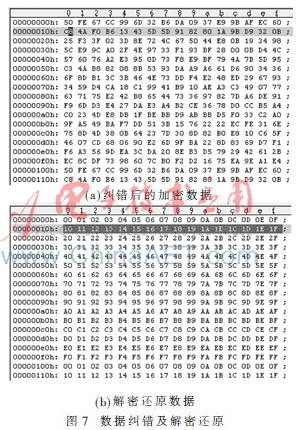

查看數(shù)據(jù)的漢明校驗(yàn)碼,如圖6所示,根據(jù)校驗(yàn)信息對(duì)數(shù)據(jù)進(jìn)行糾錯(cuò),再解密,數(shù)據(jù)還原正確,如圖7所示,加密數(shù)據(jù)中第17 B已經(jīng)由“C0”糾正為“C8”。

4 結(jié)論

本文設(shè)計(jì)并實(shí)現(xiàn)了基于FPGA的AES加密存儲(chǔ)器,利用計(jì)算機(jī)軟件完成部分設(shè)計(jì)(如密鑰的擴(kuò)展和S盒的設(shè)計(jì))后直接例化到FPGA ROM核中,簡(jiǎn)化了硬件設(shè)計(jì);同時(shí)采用流水線技術(shù),加快硬件加密速度。另外,為了避免由于存儲(chǔ)芯片NAND Flash出現(xiàn)的位翻轉(zhuǎn)而造成加密系統(tǒng)的誤碼擴(kuò)散問(wèn)題,在加密數(shù)據(jù)寫(xiě)入存儲(chǔ)器前設(shè)計(jì)生成了漢明校驗(yàn)碼,而數(shù)據(jù)校驗(yàn)則在計(jì)算機(jī)中完成,這樣能幾乎不改變硬件數(shù)據(jù)讀寫(xiě)速度,同時(shí)有效地提高了系統(tǒng)的可靠性。

參考文獻(xiàn)

[1] 王建勛.基于NAND閃存的固態(tài)存儲(chǔ)技術(shù)研究與實(shí)現(xiàn)[D].長(zhǎng)沙:國(guó)防科學(xué)技術(shù)大學(xué),2010.

[2] 龔進(jìn).AES加密算法在電子系統(tǒng)中的優(yōu)化及應(yīng)用研究[D].太原:中北大學(xué),2012.

[3] 陳鐵明,葛亮,蔡家楣,等.TinyTCSec:一種新的輕量級(jí)無(wú)線傳感器網(wǎng)絡(luò)鏈路加密協(xié)議[J].傳感技術(shù)學(xué)報(bào),2011,24(2):275-282.

[4] 陳鐵明,白素剛,蔡家楣.TinyIBE:面向無(wú)線傳感器網(wǎng)絡(luò)的身份公鑰加密系統(tǒng)[J].傳感技術(shù)學(xué)報(bào),2009,22(8):1193-1197.

[5] 陳武.NandFlash糾錯(cuò)碼的設(shè)計(jì)研[D].杭州:浙江大學(xué),2011.

[6] 辛英.漢明碼糾錯(cuò)檢錯(cuò)能力分析與應(yīng)用[J].鹽城工學(xué)院學(xué)報(bào):自然科學(xué)版,2008,21(1):34.