0 引言

隨著計算機網(wǎng)絡和嵌入式系統(tǒng)的快速發(fā)展,信息安全已成為廣大用戶關(guān)注的重點,而加密技術(shù)作為信息安全的利器,正發(fā)揮著重要的作用。加密系統(tǒng)目前已廣泛應用在安全電子支付、金融智能卡、身份識別、生物特征識別、電子護照和可信計算等安全領(lǐng)域。傳統(tǒng)的加密方法是通過在主機上運行加密軟件來實現(xiàn)的,不僅占用主機資源,而且速度較慢。因此,基于芯片級的硬件解決方案成為保證信息安全的最可靠的途徑,把所有關(guān)鍵數(shù)據(jù)的存儲、運算都通過硬件實現(xiàn),不占用主機資源,速度快、安全性高、成本低。以FPGA為代表的可重構(gòu)硬件既具有物理安全性和高速性,又有軟件的靈活性和易維護性[1],已經(jīng)成為加密算法硬件實現(xiàn)的研究熱點。

本文研究的是加密算法的一種可靠的、高效的硬件實現(xiàn)方案,采用了目前流行的電子設計自動化技術(shù)(Electronic Design Automation,EDA),在現(xiàn)場可編程門陣列(Field Programmable Gate Array,F(xiàn)PGA)上實現(xiàn)一種可重構(gòu)的加密系統(tǒng),提出一種基于可重組體系結(jié)構(gòu)的設計原理和方法,該方法使得用戶通過編程來改變芯片內(nèi)部的電路結(jié)構(gòu),以匹配不同的加/解密算法,從而支持不同的加/解密算法在同一塊FPGA芯片上的實現(xiàn),以提高密碼芯片的安全性和靈活性。

1 開發(fā)工具介紹

1.1 QuartusⅡ開發(fā)軟件簡介

QuartusⅡ是Altera公司推出的新一代開發(fā)軟件,適合于大規(guī)模邏輯電路設計。它支持圖形編輯輸入法、基于硬件描述語言的文本編輯輸入法以及內(nèi)存編輯輸入法等多種設計方法。作為一種可編程邏輯的設計環(huán)境,其強大的設計能力已經(jīng)成為廣大設計人員首選的開發(fā)工具。本設計采用的是Quartus II 9.0版本作為開發(fā)平臺。

1.2 FPGA簡介

1.2.1 工作原理

FPGA是目前應用最廣泛的通用可重構(gòu)器件,是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進一步發(fā)展的產(chǎn)物,作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn),既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)量有限的缺點。

1.2.2設計流程

基于EDA技術(shù)的FPGA設計流程如下[2]:

(1)設計輸入:包括原理圖輸入法和HDL語言輸入法。

(2)綜合:依據(jù)給定的硬件結(jié)構(gòu)和約束條件進行編譯、優(yōu)化、轉(zhuǎn)換和綜合,以獲得門級電路甚至更底層的網(wǎng)表文件。

(3)適配:將網(wǎng)表文件配置于指定的目標器件中,使之產(chǎn)生最終的下載文件。

(4)仿真:讓計算機根據(jù)一定的算法和仿真庫,對EDA設計進行模擬,以驗證設計,排除錯誤。

(5)編程下載:將適配生成的下載文件,通過編程器或編程電纜向FPGA芯片下載,以便進行硬件調(diào)試和驗證。

(6)硬件測試:將載入了設計的硬件系統(tǒng)進行統(tǒng)一測試。

2 AES算法基本原理

AES(Advanced Encryption Standard,AES)是密碼學中的高級加密標準,又稱Rijndael加密法,代替了原先的DES算法,成為目前對稱密鑰加密中最流行的算法之一。AES是一個迭代的、對稱密鑰分組的密碼,它可以使用128、192和256位密鑰,并且用128 bit即16 B分組加密數(shù)據(jù)和解密數(shù)據(jù),通過分組密碼返回的加密數(shù)據(jù)的位數(shù)與輸入數(shù)據(jù)的位數(shù)相同。迭代加密使用一個循環(huán)結(jié)構(gòu),在該循環(huán)中重復置換和替換輸入的數(shù)據(jù)。大致步驟如下:(1)密鑰擴展(KeyExpansion);(2)初始輪(Initial Round);(3)重復輪(Rounds),共9輪且每一輪又包括字節(jié)替代、行位移、列混淆、輪密鑰加;(4)最終輪(Final Round)[3]。

以10輪算法為例,前9輪結(jié)構(gòu)相同,除了第10輪由字節(jié)變換、行移位變換、輪密鑰加3步組成外,其他9輪都由字節(jié)變換、行移位變換、列混淆變換、輪密鑰加4步構(gòu)成。

(1)SubBytes變換

在AES算法中,SubBytes變換是唯一的基于S盒的非線性置換,輸入字節(jié)按照如下方式映射為一個新的字節(jié):把該字節(jié)的低4位作為列值,高4位作為行值,在S盒中找到對應行列號的元素作為輸出。所以S盒的性質(zhì)直接決定了整個算法的成敗。SubBytes變換的逆變換是InvSubBytes,它是通過建立并查找逆S-盒來實現(xiàn)的。

(2)ShiftRows變換

ShiftRows變換即行移位,將某個字節(jié)從一列移到另一列中,移位的線性距離是4 B的倍數(shù),這種轉(zhuǎn)換在一定程度上確保了某列中的4 B被擴展到了4個不同的列中。解密中ShiftRows的逆變換是InvShiftRows。

(3)MixColumns變換

列混淆變換MixColumns實現(xiàn)的是逐列混合,符合以下變換公式:

s′(x)=c(x)·s(x)mod(x4+1)(1)

其中,c(x)={03}x3+{02}x2+{01}x+{01}

列混淆變換的系數(shù){01}、{02}、{03}是基于AES算法的執(zhí)行效率考慮的,這些系數(shù)的乘法需涉及一次移位和一次異或運算。

(4)AddRoundKey變換

輪密鑰加變換用于將輸入或中間態(tài)S的每一列,與一個密鑰字ki進行按位異或,即:

AddRoundKey(S,ki)=S?茌ki(2)

式(2)中ki由原始密鑰k通過密鑰擴展算法產(chǎn)生[4]。在解密過程中,AddRoundKey變換是自身的逆。

3 AES算法的硬件設計

AES算法中各運算部件都具有良好的統(tǒng)計特性,并行執(zhí)行能力強,加、解密執(zhí)行速度快,效率高。由于算法本身不需要繁瑣的乘法運算,所有運算部件都可以通過查找表和組合邏輯來實現(xiàn),使得AES算法的硬件實現(xiàn)方案成為可能。因此,本文采用FPGA芯片來進行設計和測試。

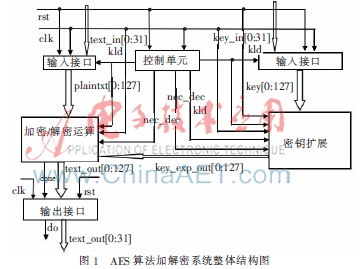

根據(jù)AES算法的基本原理和結(jié)構(gòu),結(jié)合自頂向下的設計步驟,將整個加解密系統(tǒng)分成4個相對獨立的子模塊,即接口模塊、控制單元模塊、加解密運算模塊和密鑰擴展模塊。總體結(jié)構(gòu)如圖1所示。

3.1 接口模塊

明文和密鑰被輸入接口模塊分別傳送到加解密運算模塊和密鑰擴展模塊。因為明文和密鑰輸入都要求是128 bit,為避免整個模塊輸入/輸出端口過于繁雜,分別使用4個32位的數(shù)據(jù)寄存器,在時鐘的控制下,每次輸入一組數(shù)據(jù),需要利用4個時鐘周期得到128 bit的數(shù)據(jù),并進行串并轉(zhuǎn)換。顯然這種方法可大大減少硬件資源的消耗。解密運算結(jié)果由輸出接口模塊輸出,利用并串轉(zhuǎn)換在4個時鐘周期后得到結(jié)果。

3.2 控制模塊

控制模塊負責啟動加解密運算模塊和密鑰擴展模塊工作,在時鐘脈沖控制下,控制模塊產(chǎn)生信號以控制加解密模塊中的SubBytes、ShiftRows、MixColumns、AddRoundKey各部件有序工作。信號的控制由狀態(tài)機實現(xiàn),每一次輸入新的明文或密鑰時,動作是否完成由狀態(tài)機的信號來進行判斷。狀態(tài)機信號為忙狀態(tài),表示加/解密運算正在進行,需等待;信號為空閑狀態(tài),則加/解密運算已完成,加解密運算模塊與密鑰擴展模塊啟動,分別接收原始明文和密鑰,開始新一組數(shù)據(jù)的加解密運算。

3.3 加解密運算模塊

為了盡可能減少硬件資源的消耗,采用基本迭代反饋方式,只用一個輪變換模塊進行迭代,在10個時鐘周期內(nèi)完成一個分組運算。

用VHDL語言中的元件例化語句描述出各子模塊之間連線關(guān)系,部分代碼如下:

addkey1:addroundkey port map(regout0,reg10(0),data0);

sbox1:sbox4word port map(clk1,contr1,sboxout1);

shiftrow1:shiftrow port map(sboxout1,shiftout1);

mixcolumn1:mixcolumn port map(shiftout1,mixout1);

在加解密運算模塊中,要盡可能地使用時序邏輯,以保證每個元件的輸出信號是穩(wěn)定的,從而避免毛刺現(xiàn)象的產(chǎn)生,以提高整個系統(tǒng)的可靠性。

3.4 密鑰擴展模塊

AES算法中每一輪的操作都包括與當前輪的輪密鑰進行輪密鑰加的操作。除第一輪的密鑰為初始密鑰外,其他每一輪的輪密鑰都是由子密鑰擴展而成的,也稱為擴展密鑰[5]。密鑰擴展模塊負責通過輸入的初始密鑰生成每一輪輪變換所需要的輪密鑰。采用流水線方式進行設計,即輪密鑰的生成與加密過程中的輪變換并行完成,在進行某一輪輪變換的同時,也生成了下一輪的128 bit輪密鑰。以此類推,在分組進行第k輪(k<10)運算時,并行計算第k+1輪所需的輪密鑰[6]。由于這種流水線方式采用了時間并行技術(shù),大大提高了加密速度,節(jié)省了FPGA芯片的存儲器資源,是一種可行的方案。

4 仿真分析

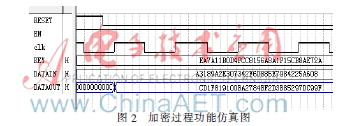

本文實驗環(huán)境為Intel Core 2.0 GHz,2 GB內(nèi)存,Windows 7操作系統(tǒng),系統(tǒng)元件設計采用VHDL語言和原理圖方法,在Quartus II 9.0環(huán)境下進行綜合、適配和仿真,最終的硬件載體是CycloneIII系列的FPGA芯片,型號為EP3C40F780C8。圖2是本系統(tǒng)的仿真波形圖。

輸入128 bit明文datain為:

A3189A2E307342F6D885E7984225A608

輸入128 bit密鑰key為:

EA7A11B0D4FCC8156A8A1F15CB8AE72A

輸出128 bit密文dataout為:

CD1F819100BA2784BF2D3B85297DC99F

從得到的仿真數(shù)據(jù)可以看出,輸出的密文數(shù)據(jù)正確、有效,驗證了本文中利用FPGA實現(xiàn)的加密算法能夠有效地運行。

5 結(jié)論

本文介紹了基于AES標準加密算法的FPGA設計方案,通過QuartusII軟件平臺實現(xiàn)對AES算法的設計與仿真,并進行加密驗證,將低成本、低功耗的FPGA芯片作為最終硬件載體,該芯片具有高速并行處理能力和可重構(gòu)能力。結(jié)果表明,用硬件實現(xiàn)加密算法并且封裝到芯片中,不易被外部攻擊者讀取或更改,有較高的物理安全性,且能最大化加密速度和最小化電路面積,利用諸如流水線和查找表等優(yōu)化技術(shù),可極大地提高系統(tǒng)效率。利用該加密算法所設計出來的加密系統(tǒng)以其可重構(gòu)性、高性能、低功耗的優(yōu)勢,勢必在信息安全市場上取勝。

參考文獻

[1] 趙峰,馬迪明,孫煒.FPGA上的嵌入式系統(tǒng)設計[M].西安:電子科技出版社,2008.

[2] 潘松.EDA技術(shù)實用教程[M].北京:科學出版社,2005.

[3] 孫瑜.基于FPGA的數(shù)據(jù)加解密系統(tǒng)設計[D].大連:大連海事大學,2010.

[4] Dong Xiaoli, Hu Yupu, Wei Yongzhuang, et al. A new method for meet-in-the-middle attacks on reduced AES[J]. China Communications, 2011(8):21-25.

[5] 韓津生,林家駿,周文錦,等.基于FPGA的AES核設計[J].計算機工程與科學,2013,35(3):80-84.

[6] 張慧,汪烈軍,于海濤,等.基于可編程器件的Rijndael加密算法優(yōu)化實現(xiàn)[J].新疆大學學報(自然科學版),2013,30(4):455-459.