文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2014)12-0053-03

0 引言

因?yàn)镾igma-delta(Σ-Δ)MEMS微機(jī)械加速度計(jì)具有尺寸小、功耗低、可靠性高等特點(diǎn),在國(guó)防軍事領(lǐng)域和民用市場(chǎng)都得到了廣泛的應(yīng)用[1]。高性能的加速度計(jì)一般采用高品質(zhì)因數(shù)(Q)的傳感器結(jié)構(gòu),在真空環(huán)境下具有較低的機(jī)械熱噪聲,靈敏度也較高,然而高Q值的加速度計(jì)具有不穩(wěn)定、響應(yīng)時(shí)間長(zhǎng)等特點(diǎn)。對(duì)低階結(jié)構(gòu)的高Q值加速計(jì)系統(tǒng)進(jìn)行PID電學(xué)補(bǔ)償能夠提高系統(tǒng)的穩(wěn)定性,但是在過(guò)采樣率不高的情況下,低階結(jié)構(gòu)的高Q值加速度計(jì)接口電路性能往往受低頻量化噪聲限制,難以滿足應(yīng)用需求[2-3]。提高過(guò)采樣率能夠一定程度上降低基帶內(nèi)的量化噪聲對(duì)系統(tǒng)性能的影響,然而這對(duì)運(yùn)放的帶寬提出了更高的要求,使得系統(tǒng)的功耗大大增加[4]。針對(duì)這一問(wèn)題,本文設(shè)計(jì)了一種高階結(jié)構(gòu)的高Q值閉環(huán)Σ-Δ加速度計(jì)接口電路,大大降低了數(shù)字接口電路基帶內(nèi)的量化噪聲。為了保證該高階系統(tǒng)的穩(wěn)定性,設(shè)計(jì)了一種前置補(bǔ)償器電路來(lái)提高電學(xué)阻尼,完成了PCB板級(jí)的開(kāi)關(guān)電容(SC)電路。測(cè)試結(jié)果表明,設(shè)計(jì)的閉環(huán)高階加速度計(jì)不僅系統(tǒng)穩(wěn)定,而且大大降低了基帶內(nèi)的量化噪聲。

1 ΣΔ加速度計(jì)系統(tǒng)結(jié)構(gòu)

微機(jī)械加速度計(jì)由敏感質(zhì)量塊m借助于彈性元件附于固定支架上,其力學(xué)模型如圖1所示。

當(dāng)外加力施加到質(zhì)量塊上時(shí),質(zhì)量塊受到了彈性力與阻尼力,其幅值分別與質(zhì)量塊的位移、速度成正比,且與系統(tǒng)外力反向。由此可得加速度a(t)作為輸入變量、質(zhì)量相對(duì)殼體位移x(t)作為輸出變量的傳遞函數(shù)為:

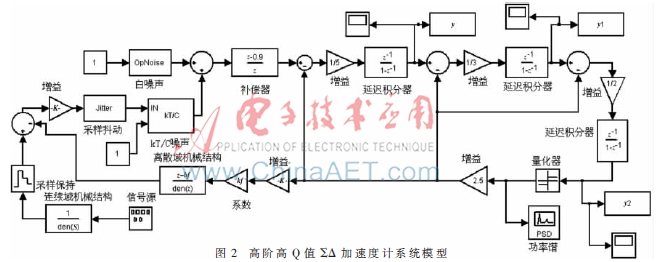

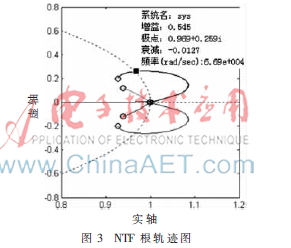

高Q值加速度計(jì)敏感結(jié)構(gòu)處于欠阻尼狀態(tài),不加任何補(bǔ)償?shù)拈]環(huán)二階系統(tǒng)條件穩(wěn)定[5]。在對(duì)高Q值二階系統(tǒng)進(jìn)行電學(xué)補(bǔ)償以后,雖然系統(tǒng)穩(wěn)定性提高,但也降低了系統(tǒng)的環(huán)路增益,使得系統(tǒng)對(duì)低頻噪聲的整形能力下降,影響輸出信號(hào)的性能。因此可以在后級(jí)增加電學(xué)調(diào)制器,提高系統(tǒng)的環(huán)路增益,加強(qiáng)加速度計(jì)系統(tǒng)對(duì)噪聲的整形能力。為使降低設(shè)計(jì)難度的同時(shí)獲取較高的性能,選取三階全反饋結(jié)構(gòu)的電學(xué)調(diào)制器結(jié)構(gòu)。基于該高Q值結(jié)構(gòu)的ΣΔ加速度計(jì)系統(tǒng)結(jié)構(gòu)模型圖如圖2所示,圖中包含機(jī)械結(jié)構(gòu)的連續(xù)時(shí)間模型、機(jī)械結(jié)構(gòu)的離散時(shí)間模型、前級(jí)電荷電壓轉(zhuǎn)換線性因子Ka、前置補(bǔ)償器、調(diào)制器、電壓力轉(zhuǎn)換因子Kg等模塊,另外還包括運(yùn)放噪聲、開(kāi)關(guān)噪聲等噪聲模塊。高階高Q值的加速度計(jì)系統(tǒng)類似于高階的電學(xué)調(diào)制器,存在系統(tǒng)穩(wěn)定性的問(wèn)題,因此需要合理設(shè)計(jì)后級(jí)電路參數(shù),以確保系統(tǒng)穩(wěn)定。圖3是圖2中的五階高Q值ΣΔ加速度計(jì)量化噪聲傳遞函數(shù)QNTF的根軌跡曲線,可以看出該高階系統(tǒng)是條件穩(wěn)定的。當(dāng)增加輸入信號(hào)的幅度使得量化器的增益小于0.545時(shí),QNTF的根軌跡進(jìn)入單位圓外,系統(tǒng)變得不穩(wěn)定,因此該高階系統(tǒng)有一個(gè)輸入信號(hào)范圍。

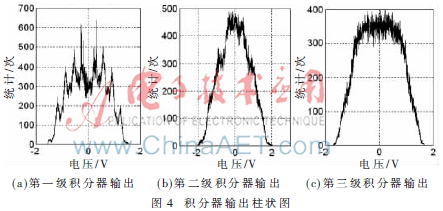

為了進(jìn)一步驗(yàn)證系統(tǒng)的穩(wěn)定性,在MATLAB的Simulink環(huán)境下對(duì)該系統(tǒng)進(jìn)行建模并進(jìn)行瞬態(tài)仿真。給該加速度計(jì)系統(tǒng)施加一個(gè)模擬的正弦加速度信號(hào),系統(tǒng)采樣頻率為250 kHz,輸入信號(hào)幅度為-7.56 dBFS(1 g),頻率為61.035 Hz,帶寬為1 kHz。各級(jí)積分器的輸出統(tǒng)計(jì)圖如圖4所示,可以看出,系統(tǒng)在輸入大信號(hào)時(shí)各級(jí)積分器輸出擺幅較小,系統(tǒng)穩(wěn)定。圖5是其一位量化器輸出的頻譜圖,仿真結(jié)果表明,該加速度計(jì)系統(tǒng)低頻噪聲較小,在1 kHz帶寬內(nèi)信噪失真比約為107 dB,能夠達(dá)到17 bit的有效精度。

2 閉環(huán)電路設(shè)計(jì)

本文整個(gè)閉環(huán)電路原理圖如圖6所示,將機(jī)械結(jié)構(gòu)部分等效成兩個(gè)可變電容CS1和CS2。接口電路部分包括低噪聲前級(jí)電荷放大器、后級(jí)采樣和保持電路、前置相位補(bǔ)償器電路、三階調(diào)制器電路以及一位DAC電路。前級(jí)低噪聲電荷放大器和采樣保持電路借鑒參考文獻(xiàn)[6]的設(shè)計(jì)原理,采用電容檢測(cè)和電壓反饋分時(shí)復(fù)用的方法來(lái)防止反饋信號(hào)和檢測(cè)信號(hào)的互相干擾[7]。這里設(shè)計(jì)了一種無(wú)源相位補(bǔ)償器電路進(jìn)行結(jié)構(gòu)的電學(xué)補(bǔ)償[8]。

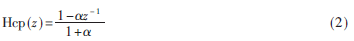

圖6中如果選取電容C2=C3=αC1,則相位補(bǔ)償器的傳遞函數(shù)為:

其中,α表示補(bǔ)償器的補(bǔ)償深度,較大的α值能夠給系統(tǒng)提供較大的相位裕度,提高穩(wěn)定性,但同時(shí)也犧牲了一定的增益。對(duì)于高階系統(tǒng),前級(jí)增益的下降可以通過(guò)后級(jí)增益進(jìn)行調(diào)整,因此系統(tǒng)的噪聲整形能力得到保障。三級(jí)調(diào)制器電路的采樣電容和反饋電容共用,電路結(jié)構(gòu)簡(jiǎn)單,且不會(huì)增加熱噪聲和運(yùn)放的負(fù)載。調(diào)制器輸出控制一位DAC反饋的開(kāi)關(guān),決定反饋電壓的極性。

3 電路測(cè)試驗(yàn)證和分析

上述的設(shè)計(jì)思路和電路原理圖已經(jīng)通過(guò)軟件進(jìn)行了仿真和驗(yàn)證,然后設(shè)計(jì)PCB來(lái)進(jìn)行實(shí)驗(yàn)驗(yàn)證。PCB檢測(cè)電路是基于高精度低噪聲運(yùn)放OPA2209和模擬開(kāi)關(guān)ADG1233進(jìn)行實(shí)驗(yàn)設(shè)計(jì)。時(shí)鐘部分由FPGA產(chǎn)生來(lái)控制模擬開(kāi)關(guān)工作。采樣得到的數(shù)字碼流經(jīng)過(guò)MATLAB程序進(jìn)行處理,從頻譜圖中可以看出系統(tǒng)的噪聲特性。為了對(duì)比高階結(jié)構(gòu)和低階結(jié)構(gòu)對(duì)低頻噪聲整形能力的不同,分別測(cè)試了基于結(jié)構(gòu)本身的二階閉環(huán)加速度計(jì)和基于三階調(diào)制器結(jié)構(gòu)的五階閉環(huán)加速度計(jì)系統(tǒng)。兩次測(cè)試的采樣頻率和采樣點(diǎn)數(shù)一致,測(cè)試結(jié)果分別如圖7和圖8所示。

從圖7的頻譜圖中可以看出,結(jié)構(gòu)本身具有一定的噪聲整形能力,但是由于結(jié)構(gòu)本身的低頻增益較低,系統(tǒng)階數(shù)不高,對(duì)于量化噪聲的整形能力有限。圖8的測(cè)試結(jié)果顯示,當(dāng)采用高階結(jié)構(gòu)以后,低頻帶內(nèi)的量化噪聲得到大大的降低,系統(tǒng)的噪聲整形能力得到很大的提高。系統(tǒng)靈敏度為1.25 V/g,低頻等效加速度輸入噪聲約為63 μg/Hz1/2。模擬開(kāi)關(guān)的導(dǎo)通電阻和饋通效應(yīng)、PCB測(cè)試板的寄生參數(shù)等都會(huì)惡化系統(tǒng)的整體性能。通過(guò)圖7和圖8 測(cè)試結(jié)果的對(duì)比可以發(fā)現(xiàn),設(shè)計(jì)的基于高Q值高階結(jié)構(gòu)的加速度計(jì)經(jīng)過(guò)電學(xué)補(bǔ)償以后系統(tǒng)穩(wěn)定,工作正常,相對(duì)于二階結(jié)構(gòu),其對(duì)傳感器帶內(nèi)量化噪聲的抑制能力大大提高。

4 結(jié)論

針對(duì)低階高Q值加速度計(jì)系統(tǒng)較高的量化噪聲問(wèn)題提出了一種高階高Q值ΣΔ電路。通過(guò)建模分析,驗(yàn)證了提出的帶前置補(bǔ)償器的高階高Q值加速度計(jì)系統(tǒng)的穩(wěn)定性,同時(shí)對(duì)該加速度計(jì)系統(tǒng)進(jìn)行了電路設(shè)計(jì)和實(shí)驗(yàn)驗(yàn)證。測(cè)試結(jié)果表明,基于前置補(bǔ)償器的高階高Q值加速度計(jì)電路系統(tǒng)穩(wěn)定,該高階結(jié)構(gòu)大大降低了傳感器帶內(nèi)的量化噪聲,提升了系統(tǒng)的性能。

參考文獻(xiàn)

[1] Lv Bingjun,Wang Pengfei,Wang Dongbo,et al.A high-performance closed-loop fourth-order sigma delta micro-machined accelerometer[J].Key Engineering Materials,2012(503):134-138.

[2] 徐偉鶴,林友玲,車(chē)錄鋒,等.一種圓片級(jí)硅三層鍵合的三明治加速度傳感器[J].傳感技術(shù)學(xué)報(bào),2008,21(2): 230-232.

[3] 孫騰,車(chē)錄鋒,黎曉林,等.基于PID反饋的高Q值加速度計(jì)閉環(huán)檢測(cè)電路[J].傳感器與微系統(tǒng),2011,30(2):101-106.

[4] LIU X W,XU H L,YIN L,et al.A low noise sigma-deltamicroaccelerometer interface circuit[J].IEICE Electronics Express,2014,11(12):1-6.

[5] 劉云濤.電容式SIGMA-DELTA微加速度計(jì)接口ASIC芯片研究[D].哈爾濱:哈爾濱工業(yè)大學(xué),2010.

[6] 呂炳均.高階SIGMA DELTA微加速度計(jì)接口ASIC芯片研究[D].哈爾濱:哈爾濱工業(yè)大學(xué),2013.

[7] 戚玉婕,車(chē)錄鋒,孫騰,等.反饋補(bǔ)償對(duì)高Q值加速度計(jì)動(dòng)態(tài)性能的影響[J].半導(dǎo)體技術(shù),2011,36(1):26-30.

[8] PETKOV V P,BOSER B E.A fourth-order ΣΔ interface for micromachined inertial sensors[J].IEEE Journal of Solid-State Circuits,2005,40(8):1602-1609.