文獻(xiàn)標(biāo)識(shí)碼: A

文章編號(hào): 0258-7998(2014)12-0056-04

0 引言

視頻信息的采集,、存儲(chǔ)、傳輸與處理一直都是多媒體領(lǐng)域研究的熱點(diǎn)[1],。多種視頻標(biāo)準(zhǔn)并存,,桌面、嵌入式等不同應(yīng)用,,需要兼顧計(jì)算高效性和編程靈活性的動(dòng)態(tài)可重構(gòu)可編程視頻處理器體系結(jié)構(gòu)[2],。而傳統(tǒng)通用處理器(Gnereal Purpose Processor,GPP),、DSP以及專用電路已很難滿足視頻處理性能和靈活性的要求,,所以支持多標(biāo)準(zhǔn)和多種視頻編解碼算法已成為視頻編解碼器發(fā)展的趨勢(shì),這向體系結(jié)構(gòu)設(shè)計(jì)提出了更高的要求[3-4],。GPP采用RISC指令系統(tǒng),,通過超標(biāo)量、亂序執(zhí)行,、動(dòng)態(tài)分支預(yù)測(cè),、推測(cè)執(zhí)行等機(jī)制,但執(zhí)行效率低下,,也只能處理較小的圖像[5],;如Intel的MMX/SSE,、IBM的AltiVec、HP的MAX-I/MAX-II等,。專用集成電路(ASIC)性能高,,執(zhí)行效率也成倍提高,如TIAN X H[6]通過利用流水線的方式來減少數(shù)據(jù)相關(guān)性, 并設(shè)計(jì)了一種完全支持RDO 的上下文存儲(chǔ)器管理機(jī)制,,能夠達(dá)到每個(gè)時(shí)鐘周期處理一個(gè)符號(hào)的速度,,但它沒有了可編程的靈活性,無法適應(yīng)多標(biāo)準(zhǔn)的發(fā)展?,F(xiàn)有編解碼器體系結(jié)構(gòu)無法完全滿足視頻處理的需求,,研究創(chuàng)新的可編程可重構(gòu)統(tǒng)一處理陣列體系結(jié)構(gòu),能夠解決視頻處理的計(jì)算高效性和編程靈活性問題[7-9],,但在視頻陣列處理器中數(shù)據(jù)加載已逐步成為陣列處理器的瓶頸,。如何減少數(shù)據(jù)的訪存冗余,提高視頻陣列處理效率,,是一個(gè)亟待解決的問題,。

本文將要介紹可編程可重構(gòu)數(shù)據(jù)加載單元的設(shè)計(jì)與實(shí)現(xiàn),從而提升視頻處理的效率與性能,。

1 運(yùn)動(dòng)估計(jì)算法對(duì)存儲(chǔ)結(jié)構(gòu)要求

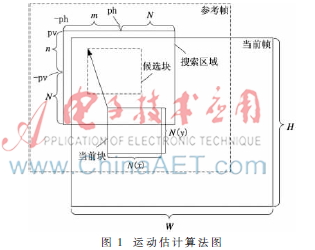

目前在視頻編解碼標(biāo)準(zhǔn)中,,運(yùn)動(dòng)估計(jì)算法主要是為了除去幀間冗余,使視頻傳輸過程中的比特?cái)?shù)大大減少,。運(yùn)動(dòng)估計(jì)基本算法就是要對(duì)當(dāng)前幀和參考幀進(jìn)行最小平均絕對(duì)值誤差(MAD)操作,,得到其運(yùn)動(dòng)矢量發(fā)送到解碼端。如圖1所示,,實(shí)線框分別表示當(dāng)前幀(W×H)和編碼的當(dāng)前塊(N×N),,虛線框分別表示參考幀(W×H)和計(jì)算的候選塊(N×N),點(diǎn)線框是參考幀的搜索區(qū)域(2pv+N×2ph+N),。

計(jì)算過程包括了六重循環(huán),,當(dāng)前塊和候選塊的每個(gè)像素計(jì)算絕對(duì)誤差和(SAA),候選塊遍歷了(2ph+N)×(2pv+N)個(gè)像素的搜索窗,,即在搜索窗內(nèi)選定了2ph×2pv比較塊,。一幀圖像計(jì)算絕對(duì)誤差和(SAA)就要進(jìn)行W×H×2pv×2ph次操作,每次絕對(duì)誤差和操作需要2個(gè)像素,,那么一幀圖像要訪問存儲(chǔ)2×W×H×2pv×2ph次,。若為1 080P 30 f/s,則總線將要讀取像素點(diǎn)7.962 64 Gpixel/s,,而實(shí)際當(dāng)前幀和參考幀的全部像素點(diǎn)僅為2×1 080×1 920×30=0.124 416 Gpixel,。訪存冗余規(guī)定如下:

若結(jié)構(gòu)不支持硬件緩存區(qū)域,訪存冗余將達(dá)到64,。那么存儲(chǔ)的帶寬BW=f×W×H×訪存冗余當(dāng)前幀+f×W×H×訪存冗余候選塊,。存儲(chǔ)帶寬由訪存冗余決定,,當(dāng)每個(gè)像素只進(jìn)行一次訪存操作時(shí),存儲(chǔ)器的帶寬最小,。所以必須在硬件內(nèi)部設(shè)置像素緩存區(qū)域,。若系統(tǒng)時(shí)鐘為100 MHz,進(jìn)行1 080P 30 f/s幀間預(yù)測(cè),,那么搜索一幀的最大時(shí)間為1/30 s,,搜索每個(gè)4×4子塊的時(shí)間為26個(gè)系統(tǒng)時(shí)鐘。pv=ph=32的搜索區(qū)域含有1 024個(gè)候選塊,,每個(gè)候選塊要進(jìn)行16次減法和15次加法,,即26個(gè)時(shí)鐘要處理1 024個(gè)候選塊31K次操作,,這顯然需要多個(gè)候選塊并行操作,,所以存儲(chǔ)系統(tǒng)要有能夠支持多個(gè)候選塊并行操作的能力。

2 視頻陣列處理器數(shù)據(jù)加載單元設(shè)計(jì)

2.1 視頻陣列處理器結(jié)構(gòu)

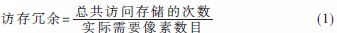

視頻陣列處理器可編程可重構(gòu)的統(tǒng)一體系結(jié)構(gòu)就是采用處理單元(PE)之間鄰接互連,,基于單指令多數(shù)據(jù)(SIMD)的數(shù)據(jù)級(jí)并行計(jì)算和多指令多數(shù)據(jù)(MIMD)的指令級(jí)并行計(jì)算,,解決了并行算法和非并行算法的計(jì)算高效性和編程靈活性。簡(jiǎn)單來說就是將算法中靈活的部分用編程方式執(zhí)行,,而算法中計(jì)算量較大的部分采用可重構(gòu)的方式并行處理,。圖2給出了完整的視頻陣列處理器系統(tǒng)結(jié)構(gòu),包含5個(gè)可編程可重構(gòu)陣列,,每個(gè)可編程可重構(gòu)陣列都是通過總線與主處理器連接且可編程可重構(gòu)陣列之間可以通過寄存器進(jìn)行通信,。每一個(gè)可編程可重構(gòu)陣列包含 16個(gè)可編程可重構(gòu)處理單元組以及一個(gè)單元組陣列控制器處理器;每一個(gè)處理單元組主要包含一個(gè)可重構(gòu)的4×4處理單元陣列以及一個(gè)可編程的處理單元組控制處理器,。

該視頻陣列處理器可編程可重構(gòu)的統(tǒng)一體系結(jié)構(gòu)可以完成視頻壓縮的計(jì)算任務(wù),,主處理器將不同的視頻壓縮算法映射到可編程可重構(gòu)陣列處理器上。根據(jù)算法特點(diǎn)分為可重構(gòu)處理部分和可編程處理部分,,用4×4陣列處理單元處理一些計(jì)算量大的算法,用可編程控制器處理比較靈活的算法,。

2.2 數(shù)據(jù)加載單元的設(shè)計(jì)

訪存時(shí),,需要局部存儲(chǔ)單元加載部分?jǐn)?shù)據(jù),以實(shí)現(xiàn)數(shù)據(jù)復(fù)用,。對(duì)當(dāng)前幀需要N×N存儲(chǔ)大小,,而數(shù)據(jù)復(fù)用重疊區(qū)域的大小為N×(N-1),;對(duì)參考幀搜索區(qū)域的存儲(chǔ)大小為2ph×2pv,,數(shù)據(jù)復(fù)用重疊區(qū)域的大小為2ph×(2pv-1),。由于處理單元(PE)不存在局部存儲(chǔ),,采用廣播策略分派數(shù)據(jù)。計(jì)算過程應(yīng)該是PC地址和數(shù)據(jù)地址的計(jì)算,,所有的操作指令都應(yīng)由PC和數(shù)據(jù)地址驅(qū)動(dòng),,系統(tǒng)根據(jù)PC取出相應(yīng)指令得到所需數(shù)據(jù),并由數(shù)據(jù)地址得到對(duì)應(yīng)的數(shù)據(jù),,由新數(shù)據(jù)或已有數(shù)據(jù)計(jì)算下一次操作的PC值和數(shù)據(jù)地址循環(huán)往復(fù),。其數(shù)據(jù)流經(jīng)計(jì)算部件輸出數(shù)據(jù)結(jié)果,,可編程大多是自主申請(qǐng)所需數(shù)據(jù),,而可重構(gòu)或ASIC為了更高的性能大多使用地址生成的策略將數(shù)據(jù)“灌入”計(jì)算單元,以節(jié)省讀取數(shù)據(jù)的時(shí)間,,增加系統(tǒng)吞吐率,。如圖3所示數(shù)據(jù)存儲(chǔ)結(jié)構(gòu),,塊區(qū)域存儲(chǔ)(Block Area Mem)需要兼顧申請(qǐng)讀取和“灌入”數(shù)據(jù)兩種模式,。實(shí)線表示加載數(shù)據(jù)通過總線分別加載到各個(gè)塊區(qū)域存儲(chǔ)中;而當(dāng)多個(gè)PE組需要加載相同數(shù)據(jù)時(shí),,如虛線表示可以通過一個(gè)發(fā)出讀請(qǐng)求的塊區(qū)域存儲(chǔ)廣播到其他需要數(shù)據(jù)的塊區(qū)域存儲(chǔ)中實(shí)現(xiàn)數(shù)據(jù)的共享,。

塊區(qū)域存儲(chǔ)(Block Area Mem)負(fù)責(zé)與總線通信,以及數(shù)據(jù)的緩存,,即需要當(dāng)前幀緩存,、參考幀緩存和寫入數(shù)據(jù)緩存。當(dāng)前幀緩存負(fù)責(zé)當(dāng)前塊的緩存和預(yù)取,,參考幀緩存負(fù)責(zé)參考?jí)K的緩存和預(yù)取,,寫入緩存負(fù)責(zé)重建幀和相關(guān)變量的寫入。若使用灌入模式,,為了達(dá)到高的處理能力,,塊區(qū)域存儲(chǔ)(Block Area Mem)對(duì)當(dāng)前塊和參考?jí)K進(jìn)行緩存和預(yù)取,為陣列處理器提供不間斷的數(shù)據(jù)源,。在數(shù)據(jù)加載中搜索窗口的數(shù)據(jù)量要多于當(dāng)前塊數(shù)據(jù),,能滿足搜索窗口的加載即可滿足當(dāng)前塊的加載,若要實(shí)時(shí)加載32×32搜索區(qū)域,,每個(gè)搜索區(qū)域的最大處理時(shí)間是4 115 ns,,即410個(gè)時(shí)鐘要加載1 024個(gè)像素分量,每時(shí)鐘應(yīng)加載3個(gè)像素,。塊區(qū)域存儲(chǔ)(Block Area Mem)采用一次加載4個(gè)像素分量設(shè)計(jì),,即32 bit的數(shù)據(jù)位寬,256個(gè)時(shí)鐘可以加載一個(gè)32×32搜索區(qū)域的像素分量,。對(duì)16×16宏塊和32×32搜索區(qū)域數(shù)據(jù)采用乒乓操作,,使當(dāng)前塊和參考幀在“灌入”模式下不間斷地提供數(shù)據(jù),。根據(jù)幀間預(yù)測(cè)算法對(duì)存儲(chǔ)需求,,電路工作在100 MHz下,,對(duì)于pv=ph=32的搜索區(qū)域,,每26個(gè)系統(tǒng)時(shí)鐘要處理1 024個(gè)候選塊,若16×16 PE組的每個(gè)PE只求一個(gè)當(dāng)前塊像素和候選塊像素差的絕對(duì)值,,剩余操作由其他PE組的PE流水完成,,那么一個(gè)16×16的PE組可以處理16個(gè)4×4子塊像素差的絕對(duì)值,。這樣要完成1 080P 30 f/s實(shí)時(shí)整數(shù)運(yùn)動(dòng)估計(jì),,需要讀取數(shù)據(jù)的16×16 PE組有1 024/(26×16)=2.462個(gè),,且這3個(gè)PE組可以利用數(shù)據(jù)共享減少對(duì)存儲(chǔ)的訪問,而總線可以對(duì)各塊區(qū)域存儲(chǔ)進(jìn)行數(shù)據(jù)廣播,,為減少對(duì)內(nèi)部總線帶寬的要求,,塊區(qū)域存儲(chǔ)(Block Area Mem)應(yīng)具備從總線讀取相同數(shù)據(jù)的能力。在Cache模式下20 KB的當(dāng)前塊緩存和參考?jí)K緩存共同構(gòu)成了16個(gè)2路直接相聯(lián)Cache,。

如圖4所示,,塊區(qū)域存儲(chǔ)(Block Area Mem)由互連檢測(cè)模塊(connect_chk),、讀寫控制模塊(rd_wt_ctrl),、16×16 Buf和32×32 Buf構(gòu)成。

(1)互連檢測(cè)模塊:主要用于檢測(cè)相鄰塊區(qū)域存儲(chǔ)與本塊區(qū)域存儲(chǔ)的互連情況,,根據(jù)配置的互連情況與周圍模塊建立連接,,傳遞數(shù)據(jù)以實(shí)現(xiàn)數(shù)據(jù)的廣播。

(2)讀寫控制模塊:負(fù)責(zé)在“灌入”模式時(shí)計(jì)算下次讀取數(shù)據(jù)的首地址,、緩沖區(qū)的切換及數(shù)據(jù)寫入,;在Cache模式時(shí),負(fù)責(zé)對(duì)2 KB寄存器進(jìn)行管理,,構(gòu)成16個(gè)2路直接相聯(lián)Cache,。

(3)16×16 Buf:用于存儲(chǔ)當(dāng)前塊數(shù)據(jù),受讀寫控制模塊的控制,。

(4)32×32 Buf:用于存儲(chǔ)參考?jí)K及搜索區(qū)域數(shù)據(jù),,受讀寫控制模塊的控制。

3 結(jié)果及分析

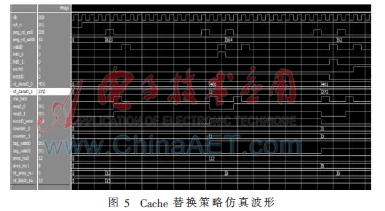

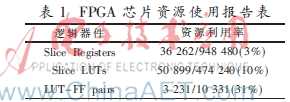

用Synopsys公司Desgin Compiler在SMIC 0.13 ?滋m CMOS工藝標(biāo)準(zhǔn)單元庫(kù)下綜合,,頻率可達(dá)197.3 MHz,。選用Xilinx公司Virtex6系列芯片Virtex XC6VLX550T進(jìn)行FPGA驗(yàn)證,綜合后的芯片資源使用情況如表1所示,。本結(jié)構(gòu)采用Verilog硬件描述,,在Questasim 10.1d下完成了功能仿真和驗(yàn)證;圖5所示為Cache模式時(shí)一組2路直接相連Cache替換策略仿真波形圖,。

第1次訪問的數(shù)據(jù)地址peg_rd_add0為25’d823區(qū)號(hào)塊號(hào)(rd_area_nu,rd_block_nu)即(12,13),,在輸出有效信號(hào)valid0有效時(shí),,hit0_0、hit0_1均為低,,此次訪問沒有命中,,替換id(excid0)為低表示本次讀取數(shù)據(jù)應(yīng)寫入本組2路ram中的0號(hào)數(shù)據(jù)ram。第2次訪問的地址仍是25’d823,,在輸出有效信號(hào)valid0有效時(shí),,hit0_0有效表示0號(hào)ram命中,且0號(hào)ram的訪問計(jì)數(shù)counter_0為0,,1號(hào)ram的訪問計(jì)數(shù)counter_1為1,,表明ram0最近被訪問過而ram1沒有被訪問。第3次訪問的地址為25’d564區(qū)號(hào)塊號(hào)(rd_area_nu,rd_block_nu)為(8,13)與823的塊號(hào)一致,,但ram1數(shù)據(jù)有效標(biāo)志tag_valid1無效,,表示不發(fā)生替換exch0為低。第4次訪問地址為上次的564,,hit0_1有效表示ram1命中,。第5次訪問的地址為25’d52區(qū)號(hào)塊號(hào)(rd_area_nu,rd_block_nu)為(0,13),此次exch0為高表示需要替換cache數(shù)據(jù)塊,,且excid0為低表示要替換ram0的數(shù)據(jù),。從上述描述可知,Cache替換策略得以正確實(shí)現(xiàn),,電路功能正確,。

從上述分析可知,在Cache模式時(shí)對(duì)寄存器進(jìn)行管理,。驗(yàn)證結(jié)果表明,,灌入和Cache模式可以滿足1 080P實(shí)時(shí)處理對(duì)數(shù)據(jù)加載的需求。

4 結(jié)束語

本文在研究分析了視頻處理編碼中運(yùn)動(dòng)估計(jì)算法的基礎(chǔ)上,,制定了視頻陣列處理器數(shù)據(jù)加載電路設(shè)計(jì)的詳細(xì)方案,,通過功能仿真驗(yàn)證了電路功能的正確性,并綜合電路,,得到了資源占用率,、工作頻率等指標(biāo)。結(jié)果表明,,該電路能夠滿足1 080P視頻處理對(duì)數(shù)據(jù)加載的要求,。該研究對(duì)于靈活性和高效性的可編程可重構(gòu)視頻陣列處理器結(jié)構(gòu)的設(shè)計(jì)有重要意義,后期將選用更多的視頻算法對(duì)該設(shè)計(jì)進(jìn)行驗(yàn)證,。

參考文獻(xiàn)

[1] 畢厚杰.新一代視頻壓縮編碼標(biāo)準(zhǔn)—H.264/AVC(第二版)[M].北京:人民郵電出版社,,2009.

[2] CHEN T C,CHIEN S Y,HUANG Y W,,et al.Analysis and architecture design of an HDTV720p 30 frames/s H.264/AVC encoder[J].IEEE Trans.Circ.Syst.Video Technol.,,2006,16(6):673-688.

[3] LIN Y L S,,KAO C Y,,KUO H C,et al.VLSI design for video coding[M].Springer,,2010.

[4] 劉定佳.H_264視頻編碼算法研究及DSP實(shí)現(xiàn)[D].西安:西安電子科技大學(xué),,2010.

[5] 黃小平,樊曉椏,,張盛兵,,等.32位雙發(fā)射雙流水線結(jié)構(gòu)RISC微處理器設(shè)計(jì)[J].西北工業(yè)大學(xué)學(xué)報(bào),2011,,29(1):6-11.

[6] TIAN X H,,LE T M,HO B L,,et al.A CABAC encoder design of H.264/AVC with RDO support[C].IEEE Interna-tional Workshop on Rapid System Prototyping,,2007:167-173.

[7] 陶文卿.面向媒體處理的可重構(gòu)陣列的結(jié)構(gòu)設(shè)計(jì)與研究[D].上海:上海交通大學(xué),2010.

[8] 張鵬,,杜建國(guó),,解曉東,等.一種基于多核流水的多標(biāo)準(zhǔn)視頻編解碼器體系結(jié)構(gòu)[J].計(jì)算機(jī)研究與發(fā)展,,2008,,45(11):1985-1993.

[9] PASTUSZAK G,,TROCHIMIUK M.Architecture design and evaluation for the high-throughput interpolation in the HEVC encoder[C].Digital System Design(DSD),,Euromicro,Los Alamitos CA,,2013:423-428.