文獻(xiàn)標(biāo)識碼: A

DOI:10.16157/j.issn.0258-7998.2015.09.039

中文引用格式: 李超,邱柯妮,張偉功,等. 基于PCIE總線主模式DMA高速數(shù)據(jù)傳輸系統(tǒng)設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2015,41(9):142-145.

英文引用格式: Li Chao,Qiu Keni,Zhang Weigong,et al. Design of a high speed data transmission system based on PCIE bus master DMA mode[J].Application of Electronic Technique,2015,41(9):142-145.

0 引言

PCIE總線是新一代的I/O互連標(biāo)準(zhǔn),它可提供點(diǎn)到點(diǎn)的串行差分信號鏈路的互連設(shè)備,且具有高性能、高帶寬、雙單工等特點(diǎn)。因此,取代了早期并行PCI總線,從而滿足了發(fā)展迅速的微處理器及存儲器對速率和帶寬的要求。PCIE總線主要特點(diǎn)如下[1]:

(1)PCIE設(shè)備在電氣上使用差分驅(qū)動器和差分接收器來發(fā)送和接收信號,一條PCIE通道(簡稱x1)由兩對LVDS差分信號線來實(shí)現(xiàn)接收和發(fā)送。

(2)可以根據(jù)需求配置為x1,x2,x4,x8,x16,x32模式,且x1通道峰值總帶寬可達(dá)0.5 Gb/s,其余的是乘相應(yīng)通道數(shù)[2]。

(3)數(shù)據(jù)使用數(shù)據(jù)包的格式,在鏈路上串行傳輸,用以保障數(shù)據(jù)的可靠性及完整性。

通過上述PCIE總線的特點(diǎn),總結(jié)出PCIE總線具有高速的傳輸特性,特別是在高速DMA控制器傳輸方式下[3],具有更廣闊的應(yīng)用前景。

本文利用PCIE總線的高速串行傳輸?shù)忍攸c(diǎn),采用Xilinx公司V5系列的FPGA芯片[4],基于PCIE2.0協(xié)議,設(shè)計(jì)出一個在FPGA板卡與PC之間以總線主模式DMA傳輸?shù)母咚?a class="innerlink" href="http://forexkbc.com/tags/數(shù)據(jù)傳輸系統(tǒng)" title="數(shù)據(jù)傳輸系統(tǒng)" target="_blank">數(shù)據(jù)傳輸系統(tǒng)。實(shí)現(xiàn)了數(shù)據(jù)的單字讀寫及總線主模式DMA讀寫通信方式,并利用上位機(jī)軟件和ChipScope(嵌入式邏輯分析工具)觀察并驗(yàn)證了讀寫數(shù)據(jù)的正確性。該系統(tǒng)為FPGA板卡作為數(shù)據(jù)采集板奠定了基礎(chǔ),可滿足數(shù)據(jù)采集卡對速率及正確性的需求。

1 PCIE簡介

與網(wǎng)絡(luò)的分層協(xié)議類似,PCIE協(xié)議規(guī)范對設(shè)備的設(shè)計(jì)也采用分層的結(jié)構(gòu),如圖1所示,從上到下有事務(wù)層、數(shù)據(jù)鏈路層、物理層,各層又都分為發(fā)送和接收部分。在發(fā)送部分根據(jù)設(shè)備核及應(yīng)用程序的信息,在事務(wù)層形成事務(wù)層包(TLP),然后數(shù)據(jù)鏈路層在TLP包上附加一些信息用于檢測等然后發(fā)送至下層,在物理層對其進(jìn)行8B/10B編碼然后發(fā)送至鏈路層。在接收部分是相反的操作。

信息以包的形式在PCIE設(shè)備間傳送,由于本設(shè)計(jì)中利用了V5芯片內(nèi)部的PCIE硬核,只有傳輸?shù)陌^和數(shù)據(jù)需要在代碼中實(shí)現(xiàn),其余的都是PCIE硬核自動生成并加到包頭或包尾。如圖2所示為給出的一個包頭的通用字段[5],包頭長為3DW或者4DW,分別可支持32 bit和64 bit存儲器尋址。PCIE協(xié)議規(guī)定Fmt指示包的格式,Type指示包的類型,根據(jù)Fmt及Type的不同組合來定義不同類型的事務(wù)包。本系統(tǒng)主要實(shí)現(xiàn)單字讀寫及DMA讀寫,因此主要使用了事務(wù)層包中的存儲器請求包及完成包兩種。如果是一個存儲器寫事務(wù),請求者會填寫正確的TLP內(nèi)容及地址并將數(shù)據(jù)放在TLP包頭后發(fā)送給完成者,完成者會解析收到的包并將數(shù)據(jù)放到自己的存儲空間中。如果是一個存儲器讀事務(wù),請求者會填寫滿足存儲器讀事務(wù)的Fmt及Type字段等,完成者接收到該包后會根據(jù)要求生成完成包發(fā)送給請求者,請求者解析完成包并將數(shù)據(jù)存儲。

每個PCIE設(shè)備的功能與其配置空間是相關(guān)聯(lián)的,配置空間由配置寄存器構(gòu)成,是軟件與設(shè)備硬件進(jìn)行交互與聯(lián)系的區(qū)域,是實(shí)現(xiàn)即插即用的基礎(chǔ)。軟件可通過配置空間檢測到一個PCIE設(shè)備的存在并通過它訪問該設(shè)備,為設(shè)備申請其需要的資源(包括存儲器、IO、中斷等)。

2 軟件、驅(qū)動程序及硬件設(shè)計(jì)

2.1 系統(tǒng)介紹

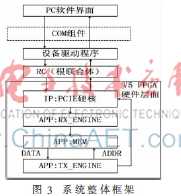

基于PCIE總線主模式DMA高速數(shù)據(jù)傳輸系統(tǒng)的設(shè)計(jì)框架圖如圖3所示,其中包括上位機(jī)軟件、COM組件、設(shè)備驅(qū)動程序及硬件部分。其中上位機(jī)軟件的主要功能是顯示測試速度、DMA命令的設(shè)置與啟動以及顯示數(shù)據(jù)結(jié)果。COM組件封裝了與驅(qū)動程序交互的函數(shù),使得開發(fā)層次更加分明。設(shè)備驅(qū)動程序用于與PC內(nèi)根聯(lián)合體(RC)交互,最終通過根聯(lián)合體的PCIE控制器與硬件FPGA進(jìn)行通信。本文實(shí)現(xiàn)了單字讀寫及總線主模式DMA讀寫兩種模式。總線主模式指的是以硬件PCIE總線端為主,向PC寫入數(shù)據(jù)或者從PC讀出數(shù)據(jù)。

2.2 軟件及驅(qū)動

本系統(tǒng)的上位機(jī)軟件界面采用Visual Studio2010編寫,調(diào)用COM組件使其與驅(qū)動程序進(jìn)行交互,COM組件封裝了與驅(qū)動程序交互的函數(shù),包括打開設(shè)備、單字讀寫、DMA讀寫的函數(shù)等,可以供上層軟件使用,使用COM組件的好處是可以使得程序變得更加通用,上層的界面實(shí)現(xiàn)可以更加多樣(例如可以是MFC、VB、網(wǎng)頁或者是WIN32控制臺)。如果需要增加一些功能,那么只需修改COM組件即可,使上層程序與驅(qū)動分離,各層的功能更加專一。

PCIE驅(qū)動程序的設(shè)計(jì)是參考Xilinx官網(wǎng)的驅(qū)動標(biāo)準(zhǔn),該驅(qū)動是基于WDM模式的,參考該驅(qū)動作了相應(yīng)的修改,利用WDK生成Win7系統(tǒng)使用的驅(qū)動文件并在系統(tǒng)檢測到實(shí)驗(yàn)板后加載該驅(qū)動,使得COM組件可以實(shí)現(xiàn)單字讀寫及DMA的讀寫方式,并將DMA寫的數(shù)據(jù)在軟件界面中顯示或者保存下來。

2.3 硬件設(shè)計(jì)

硬件設(shè)計(jì)部分主要包括PCIE的硬核及應(yīng)用邏輯模塊兩部分,PCIE的硬核(IP)是利用ISE工具生成的,包括PCIE物理層及鏈路層模塊,而應(yīng)用邏輯模塊(APP)包括接收引擎模塊、發(fā)送引擎模塊及存儲訪問模塊。

2.3.1 模塊簡介

RX_ENGINE模塊是接收引擎處理模塊,負(fù)責(zé)解析IP核的數(shù)據(jù)包以及單字讀、DMA讀接收數(shù)據(jù)包的狀態(tài)機(jī)。TX_ENGINE模塊是發(fā)送引擎處理模塊,負(fù)責(zé)單字寫、DMA寫狀態(tài)及和中斷控制。MEM模塊是存儲訪問模塊,里面包含DMA狀態(tài)及控制寄存器用以控制DMA讀寫,這里的寄存器是利用PIO的方式寫入的(即單字讀寫)。上層軟件在界面中設(shè)置的長度、數(shù)量的值等將會寫入到這些寄存器中。本設(shè)計(jì)中使用V5芯片中自帶的PCIE IP硬核完成PCIE協(xié)議中物理層及數(shù)據(jù)鏈路層的功能。

2.3.2 DMA寫流程

由于采用的是總線主模式的DMA方式,即一次DMA寫的過程是由FPGA的RAM寫入PC的存儲器中,并在上位機(jī)軟件中顯示出來的過程。在TX引擎向硬核發(fā)送數(shù)據(jù)前,首先需要填充正確的TLP包頭,包頭的信息需要由上位機(jī)軟件控制。DMA寫的過程如下:

(1)在軟件界面中設(shè)置本次DMA寫的大小、數(shù)量、地址等及DMA寫啟動命令。

(2)驅(qū)動程序?qū)⒌谝徊街性O(shè)置的內(nèi)容通過PIO(程控輸入/輸出)的方式,最終以TLP包的形式發(fā)送給硬件并寫入到MEM中的DMA狀態(tài)控制寄存器中。

(3)根據(jù)DMA狀態(tài)與控制寄存器的內(nèi)容,在收到DMA寫啟動命令后,TX引擎開始從RAM中讀取數(shù)據(jù)并按第一步設(shè)置的DMA大小數(shù)量來組裝TLP包然后發(fā)送到EP模塊。在EP模塊加入鏈路層及物理層的包頭等信息后發(fā)送到主機(jī)存儲器中。

(4)COM組件將DMA寫地址的數(shù)據(jù)映射到上位機(jī)一個緩沖區(qū)中,上位機(jī)軟件通過讀取對應(yīng)地址的緩沖區(qū)數(shù)據(jù)來驗(yàn)證數(shù)據(jù)并顯示在其界面中。

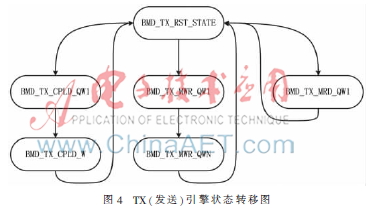

其中TX引擎的狀態(tài)轉(zhuǎn)移過程如圖4所示。在BMD_TX_RST_STATE狀態(tài)中收到寫啟動命令后,填寫存儲器寫TLP包頭的前64 bit內(nèi)容,包括圖中的FMT、TYPT、LENGTH、ID等。然后跳轉(zhuǎn)進(jìn)入BMD_TX_MWR_QW1狀態(tài),該狀態(tài)完成存儲器寫TLP包頭的第二個64 bit內(nèi)容,包括有地址及需要傳輸數(shù)據(jù)的高32位數(shù)據(jù)。最后跳轉(zhuǎn)進(jìn)入BMD_TX_MWR_QWN狀態(tài)來發(fā)送剩余的數(shù)據(jù),當(dāng)發(fā)送數(shù)據(jù)的數(shù)量達(dá)到軟件設(shè)置的DMA寫大小后,跳轉(zhuǎn)回BMD_TX_RST_STATE狀態(tài)。其他的狀態(tài)分別對應(yīng)發(fā)送單字讀完成包及存儲器讀包的狀態(tài)。

2.3.3 DMA讀流程

DMA讀的過程是將上位機(jī)一個存儲空間的數(shù)據(jù)讀入到FPGA的RAM中,從硬件的角度上看是FPGA向PC發(fā)送存儲器讀命令,然后PC向FPGA返回帶數(shù)據(jù)的完成包。但實(shí)現(xiàn)時是軟件設(shè)置本次DMA讀的地址、數(shù)量等然后啟動本次傳輸,由FPGA接收數(shù)據(jù)并存入到RAM里,通過ChipScope可觀察到數(shù)據(jù)。DMA讀的過程如下:

(1)在軟件界面中設(shè)置本次DMA讀的地址、大小、數(shù)量等及DMA讀啟動命令。

(2)這些命令通過COM組件與驅(qū)動程序交互,并生成相應(yīng)的TLP包發(fā)送給硬件,寫入圖MEM的DMA狀態(tài)控制寄存機(jī)中。

(3)根據(jù)DMA狀態(tài)與控制寄存器的內(nèi)容,收到DMA讀啟動命令后,在TX引擎中根據(jù)剛剛軟件設(shè)置的命令組裝存儲器讀TLP包后發(fā)送給EP模塊,在EP模塊中加入數(shù)據(jù)鏈路層及物理層所需的包頭等最后串行傳出到上位機(jī)中。

(4)上位機(jī)根據(jù)收到的存儲器讀包,在指定的地址讀取數(shù)據(jù)后形成帶數(shù)據(jù)完成包(CPLD)返回給FPGA,并存儲在FPGA內(nèi)的一個RAM里。

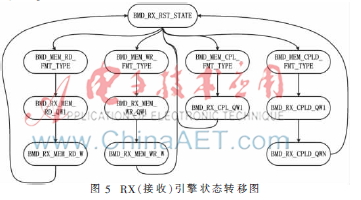

其中RX引擎的狀態(tài)轉(zhuǎn)移過程如圖5所示。在BMD_RX_RST_STATE狀態(tài)中根據(jù)收到的包頭類型來判斷轉(zhuǎn)入的下一個狀態(tài),如果收到的是一個完成包頭類型則轉(zhuǎn)入BMD_MEM_CPLD_FMT_TYPE狀態(tài),從收到的包中截取完成包的大小等進(jìn)入BMD_RX_CPLD_QW1,從包中截取地址等信息后跳轉(zhuǎn)進(jìn)入BMD_RX_CPLD_QWN狀態(tài),在這里根據(jù)軟件界面設(shè)置的DMA讀的大小將讀出的數(shù)據(jù)寫入到完成包RAM中。完成后回到BMD_RX_RST_STATE狀態(tài)。

3 仿真與實(shí)現(xiàn)結(jié)果

本文設(shè)計(jì)的總線主模式高速數(shù)據(jù)傳輸系統(tǒng)在將硬件部分燒錄到板卡的FPGA芯片后,通過板卡的PCIE金手指插入到PC的主板上,PC重啟檢測到新的硬件插入后便可安裝對應(yīng)的PCIE驅(qū)動文件,成功安裝去驅(qū)動后,便可使用上位機(jī)軟件進(jìn)行測試。

上位機(jī)軟件界面如圖6所示,包括有單字讀寫設(shè)置模塊、DMA讀寫設(shè)置模塊、傳輸速率顯示模塊、DMA寫數(shù)據(jù)顯示模塊。

以一次DMA寫為例來介紹上述模塊,在軟件上設(shè)置本次DMA寫的TLP大小及TLP數(shù)量,將寫模式復(fù)選框勾選并點(diǎn)擊開始按鈕,可在界面上看到傳輸數(shù)據(jù)的結(jié)果及本次測試DMA寫的速度。

經(jīng)多次實(shí)驗(yàn)測試,在上位機(jī)軟件界面上設(shè)置DMA讀、寫TLP事務(wù)層包(即數(shù)據(jù)包)大小為128 B,傳輸數(shù)據(jù)包的數(shù)量為16,其中某次測得的寫速度結(jié)果為3 390 Mb/s=423 MB/s,速度的大小與一次DMA傳輸?shù)腡LP數(shù)量及TLP包的大小有關(guān)。界面中顯示的周期數(shù)(Cycles)為完成本次DMA所用的Cycle數(shù)量,實(shí)驗(yàn)板上采用V5LX85t芯片,且鏈路上采用差分信號傳輸,一個cycle用時為16/1 000 000 ns,由此可計(jì)算出傳輸128 B×16×8=16 384 B的數(shù)據(jù)用時為16×302/1 000 000 ns,速度約為3 390 Mb/s即423 MB/s,分析代碼得出可能是由于存儲及讀取數(shù)據(jù)的過程會占用一定的時間影響速率,才使得速度沒有達(dá)到pcie中x1通道的0.5 Gb/s的峰值帶寬。將來也可根據(jù)需求將PCIE硬核配置x2、x4通道,會加快通信速率。

在DMA讀測試中,F(xiàn)PGA向上位機(jī)讀數(shù)據(jù),并將數(shù)據(jù)存入另一個RAM中,上位機(jī)初始化時向一片地址的緩沖區(qū)內(nèi)寫入固定的數(shù)0x12345678,利用DMA方式讀取該地址的數(shù)據(jù),在ChipScope中可以看到寫入的數(shù)據(jù)都是12345678,如圖7所示。這里由于設(shè)定RAM是64 bit的,所以是兩個重復(fù)的數(shù)字,且由于計(jì)算機(jī)內(nèi)采用的是小端存儲,所以顯示的數(shù)為78563412。

本系統(tǒng)通過軟件、驅(qū)動、硬件的協(xié)調(diào)設(shè)置,實(shí)現(xiàn)了基于PCIE總線的高速數(shù)據(jù)傳輸系統(tǒng),首先通過軟件界面設(shè)置讀寫的方式來配置硬件中的DMA狀態(tài)與控制寄存器,然后在硬件代碼中根據(jù)寄存器的內(nèi)容完成單字讀寫或DMA讀寫的過程,最后將測得的數(shù)據(jù)及速率顯示在軟件界面上。

4 結(jié)束語

本文實(shí)現(xiàn)的基于PCIE的總線主模式DMA高速數(shù)據(jù)傳輸系統(tǒng)可以完成上位機(jī)與實(shí)驗(yàn)板卡通過PCIE進(jìn)行單字讀寫或DMA讀寫大量數(shù)據(jù),并達(dá)到較高的傳輸速率,x1通道速率可穩(wěn)定在400 MB/s左右,為該實(shí)驗(yàn)板將來作為數(shù)據(jù)采集模塊采集有用數(shù)據(jù)并提供給上位機(jī)分析奠定了基礎(chǔ)。通過測試發(fā)現(xiàn),在FPGA中利用core_gen生成的RAM還存在一定的缺陷,如容量不夠大、占用芯片資源等問題,將來應(yīng)替換成板卡上的SDRAM,以此來提高傳輸數(shù)據(jù)的數(shù)量,將該系統(tǒng)用于實(shí)際應(yīng)用中。

參考文獻(xiàn)

[1] 馬鳴錦,朱劍冰,何紅旗,等.PCI、PCI-X和PCI Express的原理及體系結(jié)構(gòu)[M].北京:清華大學(xué)大學(xué)出版社,2006.

[2] BUDRUK R.PCI Express系統(tǒng)體系結(jié)構(gòu)標(biāo)準(zhǔn)教材[M].田玉敏,王崧,張波,譯.北京:電子工業(yè)出版社,2005.

[3] 張偉達(dá).基于PCI Express的高速數(shù)據(jù)傳輸系統(tǒng)研究與開發(fā)[J].計(jì)算機(jī)測量與控制,2009,12(17):2555-2557.

[4] 王嘉良,趙曙光.用FPGA實(shí)現(xiàn)PCI-E接口和DMA控制器設(shè)計(jì)[J].計(jì)算機(jī)技術(shù)與發(fā)展,2011,21(6):181-184.

[5] 任連芳.基于PCI Express總線的數(shù)據(jù)傳輸與存儲[D].南京:南京理工大學(xué),2010.