文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.2016.08.008

中文引用格式: 孫豐軍,李文強,陳思若. 高度整合硬件加速器的原型驗證平臺Protium[J].電子技術(shù)應(yīng)用,2016,42(8):41-43.

英文引用格式: Sun Fengjun,Li Wenqiang,Chen Siruo. Highly integrated hardware acceleration platform Protium[J].Application of Electronic Technique,2016,42(8):41-43.

1 展訊手機芯片性能驗證的挑戰(zhàn)

隨著智能手機的快速發(fā)展,用戶對手機芯片的性能要求也越來越高,與之對應(yīng)的是芯片的規(guī)模也越來越大,軟件也越來越復(fù)雜,為了提高用戶體驗,加速芯片上市時間,在芯片流片回來前,需要盡早啟動大量的軟硬件系統(tǒng)調(diào)試工作,而傳統(tǒng)的FPGA流程已經(jīng)很難滿足要求。比如芯片性能測試中必須用到的GPU模塊,對應(yīng)傳統(tǒng)的FPGA測試,一片Xilinx公司的Virtex7芯片已經(jīng)無法容納一款中高性能手機芯片的GPU模塊,GPU模塊的特殊性又使得該模塊在FPGA上做partition變得很繁瑣困難。同時FPGA調(diào)試板由于其調(diào)試復(fù)雜性往往延遲到項目后期才能成熟和使用,對于軟件團隊來說存在著無米下炊的困惑。

2 現(xiàn)有仿真平臺在軟件調(diào)試上的局限

硬件加速器現(xiàn)在已經(jīng)成為驗證流程里一個不可或缺的關(guān)鍵平臺。由于相對于軟件仿真(simulation)巨大的速度優(yōu)勢和全面的debug調(diào)試能力,硬件加速器已經(jīng)廣泛應(yīng)用在硬件加速仿真,系統(tǒng)級驗證,軟件開發(fā)調(diào)試等各個階段,是整個驗證周期最早可以獲得的軟硬件協(xié)同的系統(tǒng)級驗證平臺。然而當(dāng)RTL開發(fā)進入到成熟期后,硬件加速器的硬件debug能力已經(jīng)不是必需的,反而是運行速度成為軟件工程師關(guān)注和體驗的焦點。硬件加速器的典型速度約在1 MHz~2 MHz,對于軟件工程師來說還是不夠快。另外當(dāng)多個軟件工程師同時需要硬件加速器的資源進行調(diào)試時,將加劇硬件加速器的資源短缺,也增加了軟件調(diào)試開發(fā)的成本。

自研FPGA原型板或者是選擇商用FPGA原型板由于其運行速度的優(yōu)勢也是目前廣泛使用的配套解決方案。可是其缺點也是非常明顯的。調(diào)試FPGA原型板往往由于FPGA先天調(diào)試能力的欠缺而使得整個調(diào)試周期冗長且不可控,而且也需要投入大量的人力資源做專門的維護,這對于時間預(yù)算緊張的項目來說往往意味著風(fēng)險。有沒有一種解決方案可以結(jié)合硬件加速器調(diào)試能力和商用FPGA原型板的速度優(yōu)勢呢?

3 Protium的基本特點和優(yōu)勢

Protium是Cadence新近推出的基于FPGA的快速原型驗證解決方案,適用于早期軟件開發(fā),回歸測試和高性能系統(tǒng)級驗證。Protium應(yīng)用了最新一代的超大規(guī)模FPGA,提供了一整套從編譯到軟件調(diào)試的流程,具有快速啟動和簡單易用的特點。最有價值的是Protium完全兼容Cadence硬件加速器Palladium的編譯流程,可重用硬件加速器上廣泛使用的降速橋(speedbridge),用戶因此可以平滑快捷地從Palladium仿真環(huán)境過渡到更高性能的快速原型驗證平臺上來。Protium具有以下特點及優(yōu)勢:

(1)基本特點

最大支持8 x Xilinx Virtex-7 2000T FPGA。

(2)與硬件加速器Palladium完美整合

①可重用Palladium仿真編譯環(huán)境,包括編譯和運行時腳本;

②兼容Palladium的speedbridge系列加速橋;

③自動生成post-partition 數(shù)據(jù)庫,可返回Palladium進行快速模型驗證。

(3)全自動的FPGA后端實現(xiàn)

①全自動的FPGA partition和布局布線(PNR);

②全自動的Memory Model轉(zhuǎn)換和模型化;

③全自動時鐘樹轉(zhuǎn)換(包括 gated clock, multiplexed clocks, latch etc.);

④全自動的timing closure,自動消除setup/hold time violations。

(4)多樣化的調(diào)試解決方案

①支持對存儲單元的數(shù)據(jù)上載和下載;

②支持force和release;

③可選的black-box解決方案,可支持高速設(shè)計模塊和接口;

④提供擴展子板支持用戶定制接口;

⑤可返回Palladium進行復(fù)雜調(diào)試。

4 Protium編譯運行流程

4.1 Protium系統(tǒng)級驗證環(huán)境

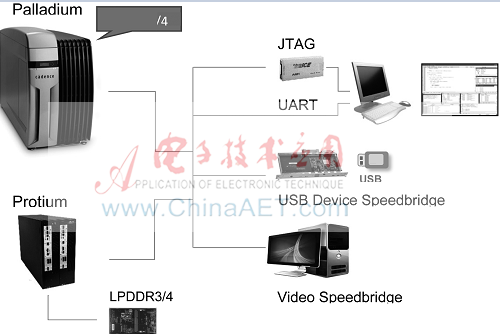

實驗室系統(tǒng)級驗證環(huán)境如圖1所示。

圖1 Protium系統(tǒng)驗證環(huán)境

(1)Palladium PXPII X16:硬件加速器72M gate。

(2)Protium:FPGA快速原型驗證系統(tǒng),支持8 Xilinx Virtex-7 FPGA。

(3)JTAG & UART:通過SOC的JTAG接口連接ARM debugger;通過SOC的UART接口連接PC串口,用于打印軟件debug信息。

(4)Video speedbridge:通過SOC視頻輸出接口顯示實時視頻圖像。

(5)USB Device speedbridge:通過SOC USB接口連接U盤文件存儲器。

(6)DDR daughter board:Protium專用子卡,用于支持SOC外接的DDR。

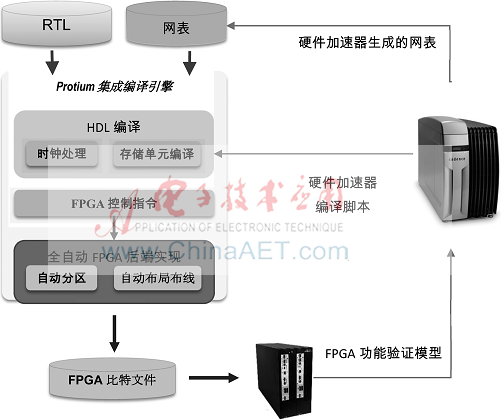

4.2 Protium的編譯及運行流程

Protium編譯運行流程如圖2所示,主要步驟如下:

(1)在Palladium上做回歸仿真測試,確保RTL和主要端口工作正常,比如串口,JTAG,LPDDR4。

(2)復(fù)用Palladium的編譯腳本,加入FPGA控制命令,如board file, probes等。

(3)將步驟(1)產(chǎn)生的Palladium網(wǎng)表作為設(shè)計輸入,執(zhí)行步驟(2)更新后的腳本完成HDLICE編譯和FPGA布局布線并產(chǎn)生最終FPGA可用的bitfile。

(4)下載步驟(3)產(chǎn)生的bitfile到Protium。

(5)復(fù)用Palladium仿真過程中使用的初始化腳本,以執(zhí)行必要的初始化過程,比如 load image文件到ROM/SRAM/LPDDR4, force/release, setup trigger等。

(6)執(zhí)行run命令。

圖2 Protium編譯運行流程

5 硬件調(diào)試過程

如果硬件運行不正常,可通過以下三種途徑調(diào)試:

(1)設(shè)置觸發(fā)條件,并通過Xilinx Chipscope下載信號波形調(diào)試。

(2)返回Palladium運行,執(zhí)行同一運行時初始化命令腳本,排除RTL版本差異導(dǎo)致的功能性問題。

(3)利用編譯中產(chǎn)生的verification model直接在Palladium上運行,以排除FPGA后端處理階段可能產(chǎn)生的時序和功能性問題。

6 軟件調(diào)試過程

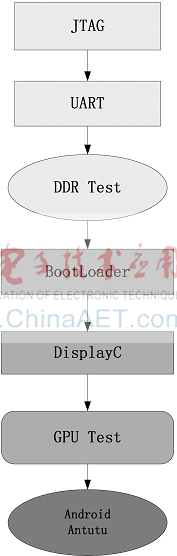

軟件測試目的為:Boot Android及Benchmark測試,包括Memory Copy,Antutu跑分等。

軟件的調(diào)試過程如圖3所示,首先是健全測試,包括JTAG連接,UART打印,DDR初始化及讀寫測試,這些是軟件調(diào)試的必要條件。主要步驟如下:

圖3 軟件調(diào)試過程

(1)JTAG & UART打印:相對簡單,調(diào)試比較順利。

(2)DDR測試:在Emulator平臺,包括Palladium XP及Protium,用的是專用DDR PHY與DDR 顆粒,與EDA仿真平臺用的Model不同,對于DDR的初始化及讀寫測試,需要軟件工程師與ASIC 設(shè)計工程師的緊密配合。在這個過程中,Palladium XP強大的Debug功能為Protium平臺DDR的調(diào)試工作提供了有力支持。

(3)Bootloader及DisplayC測試:不論是Boot Android及Benchmark測試,都需要屏幕顯示,Protium外接與Palladium XP相同的Video Speedbridge,在液晶顯示器上顯示圖像。

(4)GPU測試:包括GPU的driver調(diào)試,功能測試及GPU本身BenchMark評估。

(5)Android及Antutu相關(guān)的測試:包括ANTUTU-MEMORY Operation,ANTUTU-RAMSPEED,ANTUTU-SINGLE_INTEGER,ANTUTU-SINGAL-FLOAT等。

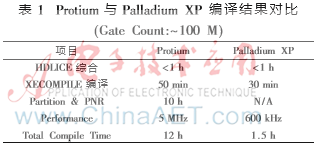

7 測試結(jié)果

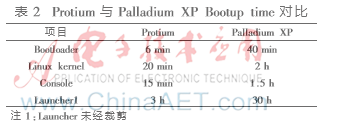

測試結(jié)果如表1和表2所示。

8 總結(jié)

借助Protium平臺,在芯片流片前,成功完成了軟硬件協(xié)同的性能測試,包括Boot Android及Antutu跑分。Protium和Palladium XP相得益彰的特性,使得在Protium開發(fā)過程中遇到問題時,可以遷移回退到Palladium XP平臺進行Debug,問題解決后,再利用Protium的速度優(yōu)勢,回歸到Protium平臺進行開發(fā),如此縮短了項目的開發(fā)周期,加速了芯片的上市進程。