革命性突破!Cadence新一代系統(tǒng)動(dòng)力雙劍為IC設(shè)計(jì)創(chuàng)造“芯”動(dòng)力

2021-06-30

作者:韋肖葳

來(lái)源:電子技術(shù)應(yīng)用

2021年6月9日,Cadence新一代硬件驗(yàn)證產(chǎn)品發(fā)布會(huì)在京舉辦。最新發(fā)布的Palladium Z2企業(yè)級(jí)硬件仿真加速系統(tǒng)和Protium X2企業(yè)級(jí)原型驗(yàn)證系統(tǒng)基于下一代硬件仿真核心處理器和Xilinx UltraScale+ VU19P FPGA,這一全新的系統(tǒng)為當(dāng)前數(shù)十億門規(guī)模的片上系統(tǒng)(SoC)設(shè)計(jì)提供最佳的硅前硬件糾錯(cuò)效率和最高的軟件調(diào)試吞吐率。

作為一家做EDA軟件起家的公司,Cadence一直以來(lái)的核心競(jìng)爭(zhēng)力是做計(jì)算型軟件。不過(guò)隨著行業(yè)的持續(xù)發(fā)展,Cadence意識(shí)到客戶的需求遠(yuǎn)超公司原先的設(shè)定,進(jìn)入到一個(gè)新的領(lǐng)域,即——“系統(tǒng)”。目前,Cadence的整體戰(zhàn)略思維就集中在智能系統(tǒng)設(shè)計(jì)上。

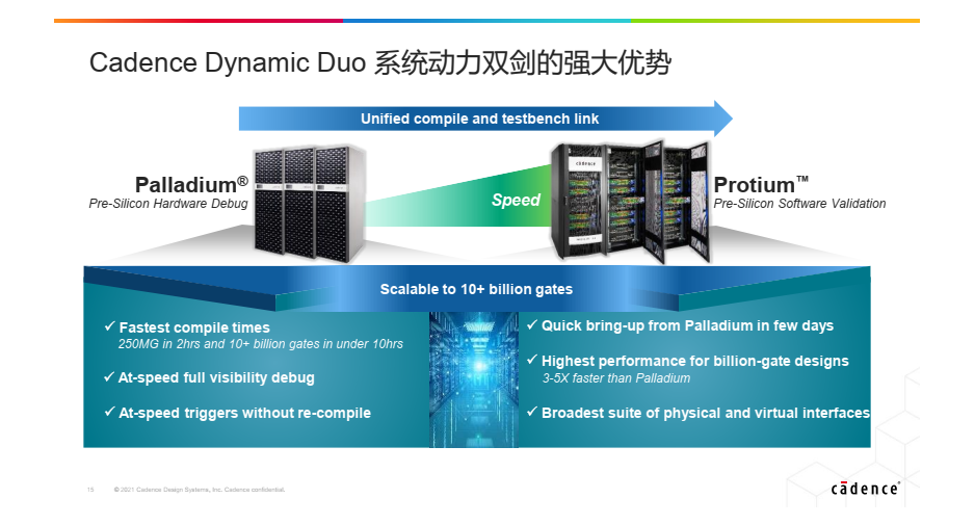

為了加速設(shè)計(jì)周期、提升算力、增強(qiáng)軟硬件協(xié)同,Cadence提出了兩個(gè)思路:第一,通過(guò)硬件的方式加速仿真;第二,引用原型驗(yàn)證的方法。基于此,Cadence推出了Palladium Z2和Protium X2系統(tǒng)動(dòng)力雙劍(dynamic duo),即Palladium? Z2企業(yè)級(jí)硬件仿真加速系統(tǒng)以及Protium? X2企業(yè)級(jí)原型驗(yàn)證系統(tǒng)。對(duì)比2015年推出的第一代,此次全新的系統(tǒng)動(dòng)力雙劍組合基于下一代定制化的硬件仿真核心處理器和Xilinx UltraScale+ VU19P FPGA,將容量提高2倍,性能提高1.5倍。以更少的時(shí)間為大規(guī)模芯片驗(yàn)證完成更多次數(shù)的迭代。

在AMD全球院士、方法學(xué)架構(gòu)師Alex Starr看來(lái),系統(tǒng)動(dòng)力雙劍加速了芯片開(kāi)發(fā)流程并優(yōu)化了AMD的左移戰(zhàn)略,這是AMD成功的重要成果之一。Xilinx關(guān)鍵應(yīng)用市場(chǎng)資深總監(jiān)Hanneke Krekels也認(rèn)為,系統(tǒng)動(dòng)力雙劍的應(yīng)用可以讓軟件工程師將寶貴的時(shí)間用于設(shè)計(jì)驗(yàn)證和軟件開(kāi)發(fā),而非耗時(shí)的原型驗(yàn)證初啟。

在正確的時(shí)間和使用場(chǎng)景中使用正確的工具

“為什么Cadence用于仿真驗(yàn)證有兩個(gè)硬件產(chǎn)品呢?事實(shí)上在項(xiàng)目的不同時(shí)間節(jié)點(diǎn)所使用的工具是不一樣的。在前期RTL驗(yàn)證、功耗分析這段時(shí)間,會(huì)使用仿真加速的方式,當(dāng)80%、90%的設(shè)計(jì)都已成熟的時(shí)候,軟件團(tuán)隊(duì)開(kāi)始介入,就會(huì)慢慢將設(shè)計(jì)遷移到原型驗(yàn)證平臺(tái),直到最后芯片Tape Out。這種流程會(huì)讓流片成功率大大提升。” Cadence亞太區(qū)系統(tǒng)解決方案資深總監(jiān)張永專先生表示。

Cadence亞太區(qū)系統(tǒng)解決方案資深總監(jiān) 張永專先生

Cadence在新一代產(chǎn)品上做了哪些升級(jí)?

制程

第一個(gè)升級(jí)是在Palladium Z2的制程上。“我們?cè)谥瞥躺嫌幸恍┬碌倪M(jìn)展。”張永專說(shuō)道,“簡(jiǎn)單來(lái)說(shuō)就是未來(lái)我們的仿真器可以做到幾乎跟軟件仿真是一樣的功能。我們做了一些特殊的設(shè)計(jì),可以讓原來(lái)的硬件仿真,我們叫2 State,0跟1之外,可以加入叫4 State,這個(gè)是一個(gè)非常先進(jìn)的一個(gè)做法,能夠讓系統(tǒng)兼容效率更好一點(diǎn)。”

FPGA

第二個(gè)突破點(diǎn)則是在Protium的FPGA上。據(jù)悉,Protium X1使用的是Xilinx UltraScale440,而新一代則應(yīng)用了VU-19P。這使得單克容量變大,同時(shí)效能也有顯著提升。“我們?cè)谡麄€(gè)跟主機(jī)的接連這部分,接口做了一些很大的改進(jìn),可以跟Palladium Z2這個(gè)硬件加速兼容,也就是說(shuō)在硬件加速可以跑這樣的一個(gè)設(shè)計(jì),很快也可以遷移到Protium來(lái)。”張永專講到,“所以想象一下,以后軟件仿真,硬件加速,原型驗(yàn)證,未來(lái)可能合成一體,Compile完全是同一個(gè)平臺(tái)。”

系統(tǒng)動(dòng)力雙劍,因何獨(dú)霸一方?

快

據(jù)張永專介紹,Palladium Z2是目前全世界業(yè)界里編譯速度最快的,能夠達(dá)到數(shù)十個(gè)Billion Gate。“我可以在十個(gè)小時(shí)內(nèi)就拿到Compile。”張永專說(shuō)道,“早上去上班,晚上下班之前就可以拿到,每?jī)蓚€(gè)小時(shí)可以Compile 250 Million Gate。”

全面的糾錯(cuò)(Debug)功能

Debug的能力實(shí)際上取決于兩方面,一個(gè)是可觀測(cè)性(Visibility),另外一個(gè)就是可控制性。與基于FPGA的仿真器有所不同,基于處理器的仿真器的優(yōu)勢(shì)就在于Debug。Palladium Z2在設(shè)計(jì)上較為特殊,不同于商用處理器,Palladium Z2使用的是Cadence全新的自定制處理器,因此具有強(qiáng)大的Debug功能。“當(dāng)你的設(shè)計(jì)進(jìn)到Palladium這個(gè)機(jī)器之后,我們的編譯器會(huì)把你的設(shè)計(jì),再將我的排程工具轉(zhuǎn)化成我的指令級(jí),放到我這里來(lái)執(zhí)行,所以我一Compile,馬上就可以運(yùn)行,不需要Place & Route。當(dāng)你的Design放到我的Palladium里面的時(shí)候,所有的訊號(hào)我都看得到,所以準(zhǔn)確率是100%。”張永專介紹到。

不需要重新編譯

當(dāng)想要在Debug過(guò)程當(dāng)中觸發(fā)一些條件來(lái)偵錯(cuò)(即:Trigger Condition)時(shí),不需要重新編譯。這一點(diǎn)就意味著可以通過(guò)快速迭代的方式,讓設(shè)計(jì)收驗(yàn),達(dá)到較好的質(zhì)量。

可快速遷移

Palladium可以快速遷移到Protium,可能在幾天之內(nèi)就可以達(dá)到原型驗(yàn)證的平臺(tái)。這項(xiàng)工作以往是需要投入很大的時(shí)間成本和人力成本才可實(shí)現(xiàn)的。

為10億門芯片設(shè)計(jì)提供最優(yōu)的硅前驗(yàn)證表現(xiàn)

據(jù)介紹,Protium的速度是Palladium的3-5倍。在Arm公司設(shè)計(jì)服務(wù)資深總監(jiān)Tran Nguyen看來(lái),系統(tǒng)動(dòng)力雙劍的使用使Arm在最新設(shè)計(jì)上實(shí)現(xiàn)了超過(guò)50%的性能提升和2倍的容量增加,為其提供了驗(yàn)證下一代IP和產(chǎn)品所需的強(qiáng)大的硅前驗(yàn)證能力。

應(yīng)用層面廣闊

“Protium也提供了所謂的In-circuit Emulation, Virtualization(虛擬原型), Memory Model。”張永專說(shuō)道,“意味著你可以用實(shí)體的卡在上面跑,比方說(shuō)PCIe,或者是虛擬的PCIe在上面跑,再或者虛擬的模型都可以。所以應(yīng)用的層面非常廣。”

Palladium,讓硬件加速惠及整個(gè)產(chǎn)業(yè)

“目前整個(gè)業(yè)界的使用狀況是——全球大概有90%的客戶都應(yīng)用了Palladium。它有最快的硅前Performance,它有強(qiáng)大的功能,像這樣一個(gè)機(jī)架可以容納144個(gè)用戶同時(shí)在上面上線使用。”張永專講到。據(jù)悉,Palladium可以支持所有的硬件設(shè)計(jì),RTL Design、Verilog、VHDL都可以接受。另外,Palladium也可以跟外界的虛擬模型放在一起,可以跟仿真一起同時(shí)仿真,看起來(lái)就像軟件仿真一樣。此外,Palladium提供非常豐富的內(nèi)存模型(Memory Model),例如:DDR5、DDR4、 HBM或UFS。 Palladium有一個(gè)特殊的模擬方式,可以把內(nèi)存直接放到硬件加速器上,因此可以解決所有在復(fù)雜系統(tǒng)上用得到的內(nèi)存模型。最后,Palladium為PCIE、USB、Ethernet等標(biāo)準(zhǔn)界面都提供相應(yīng)的物理接口,例如降速墻或虛擬模型。“就目前看來(lái),我們現(xiàn)在還沒(méi)有任何一個(gè)設(shè)計(jì)說(shuō)不能上Palladium,它可以讓整個(gè)產(chǎn)業(yè)都能夠得到硬件加速的好處。” 張永專如是說(shuō),“另外,Cadence對(duì)中小客戶也會(huì)提供很好的支持,例如使用云、租用等比較靈活的方式為有資金問(wèn)題困擾的企業(yè)創(chuàng)造更為便利的條件。”

提速安全兩不誤

談及信息安全問(wèn)題,張永專表示,系統(tǒng)動(dòng)力雙劍在信息安全方面同樣提供保障。Cadence Palladium與服務(wù)器和主機(jī)的溝通通道是經(jīng)過(guò)加密的。所以,從整體來(lái)看它的需求是不容易被破解的。由于其設(shè)計(jì)是經(jīng)過(guò)編譯的,并非原來(lái)的,因此使用這樣的平臺(tái)來(lái)進(jìn)行仿真加速以及原型驗(yàn)證可以實(shí)現(xiàn)提速與與獲得信息安全保障的雙贏。

孿生兄弟雙引擎,聯(lián)手解決產(chǎn)業(yè)痛點(diǎn)

在英偉達(dá),對(duì)高端圖形和超大規(guī)模設(shè)計(jì)的每一次升級(jí)都意味著復(fù)雜性的增加,上市時(shí)間也會(huì)愈發(fā)緊張,而采用結(jié)合Cadence Palladium Z2和Protium X2系統(tǒng)的通用前端流程,英偉達(dá)可以優(yōu)化功能驗(yàn)證(verification)、功能確認(rèn)(validation)和硅前軟件初啟的工作負(fù)載分布,按時(shí)完成對(duì)最復(fù)雜GPU和SoC設(shè)計(jì)的全面驗(yàn)證。“這兩個(gè)系統(tǒng)動(dòng)力雙劍像孿生兄弟雙引擎,協(xié)助解決整個(gè)產(chǎn)業(yè)現(xiàn)在看到的比較大的問(wèn)題。”張永專最后總結(jié)道。