徐韋佳,田俊杰,施琴

(中國人民解放軍理工大學 理學院,江蘇 南京 211101)

摘要:為了實現(xiàn)逐次逼近型模數(shù)轉換器(Successive Approximation AnalogtoDigital Converter, SAR ADC),在MATLAB平臺上使用Simulink 工具,建立SAR ADC的理想模型,主要包括數(shù)模轉換器(DAC)、比較器、譯碼器和寄存器模塊。理論分析時鐘抖動、開關非線性、比較器失調、電容失配等非理想因素對系統(tǒng)性能的影響,在理想模型基礎上添加非理想因素,進行MATLAB仿真,通過分析輸出信號頻譜的變化,總結降低非理想因素對系統(tǒng)性能影響的方法,對實際電路設計具有指導意義。

關鍵詞:SAR ADC;MATLAB;非理想因素

中圖分類號:TN432文獻標識碼:ADOI: 10.19358/j.issn.1674-7720.2017.08.007

引用格式:徐韋佳,田俊杰,施琴.SAR ADC的系統(tǒng)級建模與仿真[J].微型機與應用,2017,36(8):19-22,25.

0引言

模數(shù)轉換器(AnalogtoDigital Converter, ADC)作為連接外界模擬信號和數(shù)字信號處理系統(tǒng)的橋梁,得到了廣泛應用。在諸多不同結構的ADC中,逐次逼近型ADC(SAR ADC)具有中等精度、尺寸小、功耗低、成本低等優(yōu)點,廣泛應用在工業(yè)控制、消費電子、信號采集等場合。近年來,隨著CMOS工藝特征尺寸的不斷減小,SAR ADC的速度跟精度不斷提高,功耗跟電源電壓不斷降低,如何從系統(tǒng)級設計角度減小各種非理想因素對SAR ADC性能的影響,優(yōu)化SAR ADC的架構設計,已成為當前研究熱點之一。

當前SAR ADC的發(fā)展趨勢是高速、高精度和低功耗。然而,由于一些非理想因素的存在,會影響SAR ADC系統(tǒng)的性能。當SAR ADC趨于高速的時候,任何微小的時鐘抖動都會影響模數(shù)轉換的精度。電源電壓不穩(wěn)定會造成系統(tǒng)性能的不穩(wěn)定。開關非線性、器件失配、比較器失調、噪聲等會造成系統(tǒng)精度的下降和功耗的增加,這些都是影響SAR ADC系統(tǒng)性能的非理想因素。因此,要設計出高性能的SAR ADC,總結降低非理想因素對系統(tǒng)影響的方法,尤為關鍵。

當前國內有關SAR ADC的研究大多著重于具體電路設計細節(jié),而在系統(tǒng)級設計和建模等頂層設計方面的關注比較少[1]。今后ADC的發(fā)展趨勢是片上系統(tǒng)(System on Chip, SOC),這是一個集成了IP核、具有專用目標的集成電路,同時也是一項從確定系統(tǒng)功能開始,到軟/硬件劃分,最終完成設計的新技術。但是SoC也會帶來新的噪聲以及工藝相容性等新問題,這就需要設計者從系統(tǒng)級設計和建模中來驗證后續(xù)電路設計的可行性和價值。

基于此,本文從系統(tǒng)級設計角度,使用Simulink工具構建理想模型,分析各種非理想因素對系統(tǒng)性能的影響,通過MATLAB工具仿真和對仿真結果的頻譜分析,總結降低非理想因素影響的方法,得出在所能考慮到的因素范疇內的最優(yōu)化架構設計。

1SAR ADC的工作原理和整體架構

圖1是8位八選一多通道輸入SAR ADC的電路結構示意圖,包括多通道選擇器、采樣保持電路S/H和DAC組成的采樣DAC網絡、比較器、控制邏輯電路、移位寄存器和時鐘電路。SAR ADC的工作原理基于二進制搜索算法。轉換開始,在時鐘信號作用下,首先控制邏輯電路將移位寄存器的上一級輸出清零,并將最高位置1,輸出結果D[0:7]被輸入給采樣DAC網絡,轉換為參考電壓Vref,比較器將Vin和Vref進行比較,比較完成后,控制邏輯電路就將比較器的輸出結果傳遞給移位寄存器,確定該位保持1還是清為0,同時將次高位置1,產生新的參考電壓,進行下一位的模數(shù)轉換。這樣從高位到低位,如此循環(huán),直到完成所有的比較,最后產生八位的數(shù)字編碼輸出[2]。

2SAR ADC的主要電路建模

2.18位DAC的理想模型

圖2是8位DAC的MATLAB理想模型,使用二進制指數(shù)形式的信號放大增益表示二進制指數(shù)電容陣列,加法器用來實現(xiàn)電荷再分配功能[3]。時鐘信號由SAR ADC的控制邏輯電路產生,控制DAC電容陣列的開關是連接地電位GND,還是連接采樣電壓Vin或是基準電壓Vref。采樣結束后,通過加法器,將各電容采集信號求和輸出,這就是DAC的輸出。

2.2比較器的理想模型

圖3比較器的MATLAB理想模型圖3是比較器的MATLAB理想模型,采樣信號 Vin和 DAC 的輸出 VDAC作為加法器的輸入,求和的結果與高電平1和低電平0相比較,如果 Vin>VDAC,則比較器輸出VCOM為高電平1;如果 Vin<VDAC,則VCOM為低電平1,實現(xiàn)了比較的功能[3 4]。

2.3控制邏輯電路的理想模型

以最高位D7和次高位D6的時序控制電路為例,圖4是控制邏輯電路的MATLAB理想模型。對于最高位D7,當采樣結束時采樣時鐘CLK處于低電平,最高位D7的置位信號到來,或者比較器的輸出結果VCOM為高電平,會導致要轉換的該位為高電平。此時邏輯控制電路控制DAC的最高位開關連接Vref,或者是維持該位的高電平。同樣,對于次高位D6,采樣結束時,CLK處于低電平,并且D7比較結束,置位信號恢復低電平,此時,如果D6的置位信號到來,或者該位的VCOM為高電平,最終的輸出結果都是高電平,控制DAC的次高位開關接Vref,或者維持該位的高電平[3]。

8位SAR ADC的MATLAB系統(tǒng)理想模型包括采樣保持電路、DAC、比較器、移位寄存器、輸入模擬信號Vin、時鐘信號CLK,輸出為八位二進制數(shù)字編碼[D7:D0]。

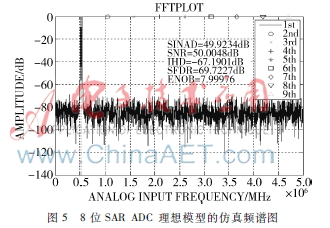

使用MATLAB仿真工具對該理想模型進行仿真[5],仿真結果如圖5所示。當采樣時鐘CLK頻率為10 MS/s、輸入信號頻率約為0.5 MHz 時,取4 096個點進行FFT分析,仿真結果顯示, ENOB=7.99 bit,SINAD=49.92 dB,SNR=50.00 dB,THD=-67.19 dB,SFDR=69.72 dB,說明該理想模型性能優(yōu)良,能夠實現(xiàn)模數(shù)轉換功能。

3SAR ADC的非理想因素分析

SAR ADC的結構主要包括控制邏輯電路、DAC和比較器。其中,控制邏輯電路的非理想因素主要包括開關非線性和噪聲,DAC的非理想因素主要包括電容陣列失配以及開關的非線性,比較器非理想因素主要是失調電壓以及外接 CLK信號的時鐘抖動造成的誤差。下面將具體分析這些非理想因素對SAR ADC系統(tǒng)性能的影響。

3.1時鐘抖動

時鐘抖動效應指由于實際采樣時刻的偏差,會導致采樣結果產生誤差。可以通過建模來確定系統(tǒng)能接受的時鐘抖動的大小[6]。

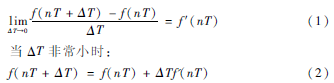

設信號函數(shù)為f(t),采樣保持電路理想時刻采樣值為f(nT),實際采樣值為f(nT+ΔT),所以:

因此采樣時鐘抖動模型的設置如圖6所示[7]。

3.2開關非線性

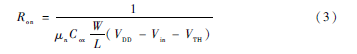

理想采樣開關的導通電阻為0,斷開時電阻無窮大。實際上,CMOS工藝下實現(xiàn)的MOS開關會出現(xiàn)時鐘饋通和電荷注入等一系列非線性因素。假設Vin是輸入,Vout是輸出,柵壓為高電平VDD時,MOS開關導通,則導通電阻Ron表示為[8]:

由公式(3)可知,開關的導通電阻Ron與輸入信號Vin有關,是一個非線性函數(shù),會限制輸入電壓范圍。為了減小導通電阻Ron,可以采用大寬長比的晶體管,但是增大了面積,增大了寄生電容,從而影響開關速度[9]。

由于開關的非線性特點,一般采用 CMOS 傳輸門開關。CMOS傳輸門開關由 NMOS 管和 PMOS 管并聯(lián)而成,總電阻相對穩(wěn)定,變化范圍小,彌補單個 MOS 管作為開關電阻值變化較大的缺陷,能夠有效解決開關非線性的問題[10]。

3.3比較器的失調

比較器的失調電壓主要包括靜態(tài)失調和動態(tài)失調兩部分[10]。靜態(tài)失調指比較器對稱的MOS管的遷移率μ、氧化層電容Cox和閾值電壓Vth的不匹配帶來的誤差用下式表示:

![}GWMMH~30ASYGGRJJE]1BAN.png }GWMMH~30ASYGGRJJE]1BAN.png](http://files.chinaaet.com/images/2017/05/27/6363147219354783295552130.png)

其中,AμCox、Avth、SμCox、Svth是工藝參數(shù),D是兩匹配晶體管間距。所以,可以通過增加晶體管面積并且減小兩管間距來減小比較器的靜態(tài)失調。

動態(tài)失調指寄生電容失配而引起的誤差。晶體管電容失配會導致充放電過程中電壓值的變化,從而產生動態(tài)失調誤差。可以通過增加晶體管面積來增加寄生電容,通過減小比值來減小比較器的動態(tài)失調誤差。

3.4電容陣列的失配

DAC的電容陣列的失配會影響整個SAR ADC的系統(tǒng)精度。假設電容失配誤差來自于單位電容C0的偏差,單位電容方差σ02,大小呈正態(tài)分布,每個輸出對應的電容值為:

Ck=2n-kC0+δk,E[δk]=0,E[δ2k]=2n-kσ20(6)

由電荷再分配原理,給定數(shù)字碼y,假設:

y=∑nk=12n-kBk(7)

計算可得,實際DAC與理想DAC的偏差,也就是DAC的INL為:

![F2}08XB0]L7_F2)4@2V7DQY.png F2}08XB0]L7_F2)4@2V7DQY.png](http://files.chinaaet.com/images/2017/05/27/6363147221331487873849922.png)

根據(jù)DNL的定義:

DNL(y)=|V(y)-V(y-1)-1LSB|

=|V(y)+Verr(y)-V(y-1)+Verr(y-1)-1LSB|

=ΔVerr(y)(9)

DNL方差為:

可以得出,電路的INL和DNL的方差與單位電容C0的平方成反比,與方差σ02成正比。因此可以通過增加C0來減小電容失配引起的誤差。

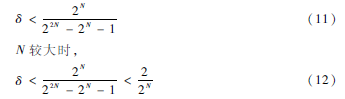

對于電荷再分配式DAC,ADC位數(shù)為N,二進制加權電容網絡允許的最大電容失配率δ滿足:

可以得出,隨著精度N的增加,電容網絡允許的最大電容失配率δ約成指數(shù)下降,當N很大時,電容網絡失配誤差與δ呈線性關系[11]。

4非理想因素仿真結果與分析

4.1時鐘抖動仿真

圖7是給SAR ADC理想模型加上采樣時鐘抖動后的系統(tǒng)仿真圖。采樣時鐘CLK頻率為10 MS/s,分別設置采樣時鐘抖動為0.1 ns,0.3 ns,0.5 ns,1 ns,進行FFT分析。仿真結果顯示,時鐘抖動為0.1 ns時,系統(tǒng)信噪比SNR為49.83 dB;時鐘抖動為0.3 ns時,SNR為48.70 dB;時鐘抖動為0.5 ns時,SNR為46.81 dB;時鐘抖動為1 ns時,SNR為44.39 dB。說明采樣時鐘抖動會造成采樣信號的偏差,從而降低系統(tǒng)SNR,進而降低系統(tǒng)的ENOB,因此為了降低抖動噪聲的影響,采樣時鐘抖動應當控制在0.3 ns之內。

4.2比較器失調仿真

圖8是給SAR ADC的理想模型加上比較器失調電壓后的仿真圖。采樣率為10 MS/s,設置比較器失調電壓為30 mV以內和50 mV以內。仿真結果顯示,比較器的失調越大,有效位數(shù)越低。當失調為30 mV以內時,ENOB為7.94 bit;當失調為50 mV以內時,ENOB為7.56 bit,所以說,考慮到一定的余量,實際電路設計中,比較器的失調電壓必須要控制在30 mV以內,否則會造成精度過低。

4.3電容失調仿真

圖9所示是DAC電容陣列失配的仿真頻譜圖。采樣率為10 MS/s,設置電容失配率分別為0.3%,0.392 2%,0.5%,1%。FFT仿真結果顯示,電容失配率為0.3%時,ENOB為7.83 bit;電容失配率為0.392 2%時,ENOB為7.61 bit;電容失配率為0.5%時,ENOB為7.02 bit;電容失配率為1%時,ENOB為5.61 bit。因此電容失配率越大,有效位數(shù)跟信噪比越差,系統(tǒng)性能變差。考慮到一定的余量,實際電路設計中,要控制電容失配率在0.5%以內。

5結論

本文從系統(tǒng)級角度,在MATLAB平臺上使用Simulink 工具,對8位SAR ADC進行系統(tǒng)級建模,包括DAC二進制權電容陣列、比較器、控制邏輯電路和移位寄存器。在理想模型基礎上,分析時鐘抖動、開關非線性、比較器失調、電容陣列失配等非理想因素對系統(tǒng)性能的影響,總結降低非理想因素影響的方法。給理想模型添加非理想因素,進行系統(tǒng)的整體仿真。FFT仿真結果顯示,要使SAR ADC實現(xiàn)較高的有效位數(shù)和信噪比,時鐘抖動要控制在0.3 ns以內,比較器失調控制在30 mV以內,DAC電容失配控制在0.5%以內,不斷優(yōu)化系統(tǒng)架構設計,對實際電路設計具有指導意義。

參考文獻

[1] 張郭敏. 流水線ADC的系統(tǒng)建模與架構設計[D]. 合肥: 合肥工業(yè)大學, 2010.

[2] 章大偉. 一種SAR ADC的設計與研究[D]. 合肥: 合肥工業(yè)大學, 2014.

[3] 徐韋佳. 一種異步逐次逼近型模數(shù)轉換器的研究與設計[D]. 合肥: 合肥工業(yè)大學, 2015.

[4] 陳幼青, 何明華. 應用于14 bit SAR ADC的高精度比較器的設計[J]. 微電子學與計算機, 2011, 28(6): 109-112.

[5] 劉旭東, 戴瀾. 14位100 MHz流水線ADC行為級建模與仿真[J]. 微電子學, 2013, 45(5): 686689.

[6] DEVRIM A, MOHAMMAD A S, FRANCO M. Switch boot strapping for precise sampling beyond supply voltage[J]. IEEE Journal of SolidState Circuits, 2006,41(8):1938- 1943.

[7] 孫肖林, 吳毅強. 4bit FLASH ADC行為級建模與仿真[J]. 現(xiàn)代電子技術, 2013,36(22): 120-123.

[8] 畢查德·拉扎維(美). 模擬CMOS集成電路設計[M]. 陳貴燦,程軍,張瑞智,譯.西安: 西安交通大學出版社, 2013.

[9] ALLEN P E, HOLBERG D R. COMS analog circuit design, Second Edition[M]. 北京: 電子工業(yè)出版社, 2002.

[10] 江向陽. 一種SigmaDelta調制器的研究與設計[D]. 合肥: 合肥工業(yè)大學, 2014.

[11] 周文婷, 李章全. SAR A/D轉換器中電容失配問題的分析[J]. 微電子學, 2007, 37(2): 199-203.