半導(dǎo)體行業(yè)技術(shù)高、進(jìn)步快,一代產(chǎn)品需要一代工藝,而一代工藝需要一代設(shè)備。SEMI 預(yù)計(jì) 2020 年半導(dǎo)體設(shè)備市場(chǎng)將增長(zhǎng) 20.7%,達(dá)到 719 億美元,創(chuàng)歷史新高。2017 年中國(guó)大陸市場(chǎng)需求規(guī)模約占全球的 15%左右, 2020 年預(yù)計(jì)占比將達(dá)到 20%,約 170 億美元。全球半導(dǎo)體設(shè)備市場(chǎng)集中度高,主要有美日荷廠(chǎng)商壟斷,國(guó)內(nèi)自給率僅有 5%左右,國(guó)產(chǎn)替代空間巨大。

隨著摩爾定律趨近極限,半導(dǎo)體行業(yè)技術(shù)進(jìn)步放緩,國(guó)內(nèi)廠(chǎng)商與全球龍頭技術(shù)差距正在逐漸縮短,我們認(rèn)為未來(lái) 3-5 年將是半導(dǎo)體設(shè)備國(guó)產(chǎn)替代黃金戰(zhàn)略機(jī)遇期。

全球壟斷,02 專(zhuān)項(xiàng)頂層設(shè)計(jì)求突破

半導(dǎo)體行業(yè)技術(shù)高、進(jìn)步快,一代產(chǎn)品需要一代工藝,而一代工藝需要一代設(shè)備。半導(dǎo)體產(chǎn)業(yè)技術(shù)進(jìn)步主要有兩大方向:一是制程越小→晶體管越小→ 相同面積上的元件數(shù)越多→性能越高→產(chǎn)品越好;二是硅片直徑越大→硅片面積越大→單個(gè)晶圓上芯片數(shù)量越多→效率越高→成本越低。

資料來(lái)源:《中國(guó)集成電路產(chǎn)業(yè)投融資研究》周子學(xué)

半導(dǎo)體工藝流程主要包括單晶硅片制造、IC 設(shè)計(jì)、IC 制造和 IC 封測(cè)。單晶硅片制造需要單晶爐等設(shè)備,IC 制造需要光刻機(jī)、刻蝕機(jī)、薄膜設(shè)備、擴(kuò)散離子注入設(shè)備、濕法設(shè)備、過(guò)程檢測(cè)等六大類(lèi)設(shè)備。半導(dǎo)體設(shè)備中,晶圓代工廠(chǎng)設(shè)備采購(gòu)額約占 80%,檢測(cè)設(shè)備約占 8%,封裝設(shè)備約占 7%,硅片廠(chǎng)設(shè)備等其他約占 5%。

半導(dǎo)體工藝流程

資料來(lái)源:清科研究中心

一般情況下,不同的晶圓尺寸和制程的 IC 制造產(chǎn)線(xiàn)所需的設(shè)備數(shù)量不同。以每 1 萬(wàn)片/月產(chǎn)能計(jì)算,12 寸產(chǎn)線(xiàn)所需的設(shè)備數(shù)量要比 8 寸產(chǎn)線(xiàn)多,12 寸先進(jìn)制程產(chǎn)線(xiàn)所需的設(shè)備數(shù)量要比 12 寸成熟制程產(chǎn)線(xiàn)設(shè)備多。

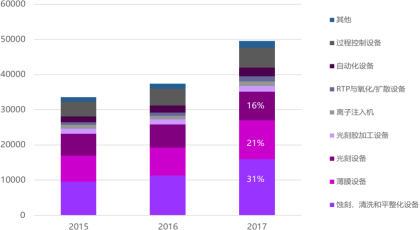

半導(dǎo)體設(shè)備屬于高端制造裝備,其價(jià)值量較高。比如高端 EUV 光刻機(jī)單價(jià)甚至超過(guò) 1 億美金。總體上看,IC 制造設(shè)備市場(chǎng)中刻蝕機(jī)、光刻機(jī)、薄膜設(shè)備的價(jià)值量占比較高。

半導(dǎo)體制造前道設(shè)備市場(chǎng)規(guī)模(百萬(wàn)美元)

資料來(lái)源:《臺(tái)積電南京專(zhuān)項(xiàng)環(huán)評(píng)報(bào)告》,中芯國(guó)際

2020 全球預(yù)計(jì)超 700 億美元,中國(guó)大陸占比超 20%

2020 年全球半導(dǎo)體設(shè)備市場(chǎng)規(guī)模預(yù)計(jì)超 700 億美元。根據(jù) 2018 年 12 月 12 日 SEMI 在SEMICON Japan 2018 展覽會(huì)上發(fā)布年終預(yù)測(cè)報(bào)告顯示,2018 年新的半導(dǎo)體制造設(shè)備的全球銷(xiāo)售額預(yù)計(jì)將增加 9.7%達(dá)到 621 億美元,超過(guò)2017 年創(chuàng)下的566 億美元的歷史新高。預(yù)計(jì)2019 年設(shè)備市場(chǎng)將收縮4.0%,至 596 億美元,但 2020 年將增長(zhǎng) 20.7%,達(dá)到 719 億美元,創(chuàng)歷史新高。

2020 年中國(guó)大陸市場(chǎng)規(guī)模占比超 20%,約 170 億美元。根據(jù) SEMI 數(shù)據(jù),2017 年中國(guó)大陸半導(dǎo)體設(shè)備銷(xiāo)售額 82.3 億美元,同比增長(zhǎng) 27%,約占全球的 15%,預(yù)計(jì) 2020 年占比將超過(guò) 20%,約 170 億美元。

全球半導(dǎo)體設(shè)備銷(xiāo)售額及增速預(yù)測(cè)(2018.12)

資料來(lái)源:SEMI 2018.12

半導(dǎo)體設(shè)備市場(chǎng)集中度高,CR10 超 60%。全球半導(dǎo)體設(shè)備生產(chǎn)企業(yè)主要集中于歐美、日本、韓國(guó)和我國(guó)臺(tái)灣地區(qū)等,以美國(guó)應(yīng)用材料、荷蘭阿斯麥、美國(guó)泛林集團(tuán)、日本東京電子、美國(guó)科天等為代表的國(guó)際知名企業(yè)起步較早, 經(jīng)過(guò)多年發(fā)展,憑借資金、技術(shù)、客戶(hù)資源、品牌等方面的優(yōu)勢(shì),占據(jù)了全球集成電路裝備市場(chǎng)的主要份額。

2017 年半導(dǎo)體制造設(shè)備前 10 強(qiáng)

資料來(lái)源:Gartner

2017 年半導(dǎo)體設(shè)備競(jìng)爭(zhēng)格局

資料來(lái)源:Gartner 2017

國(guó)產(chǎn)設(shè)備自給率低,技術(shù)加速追趕

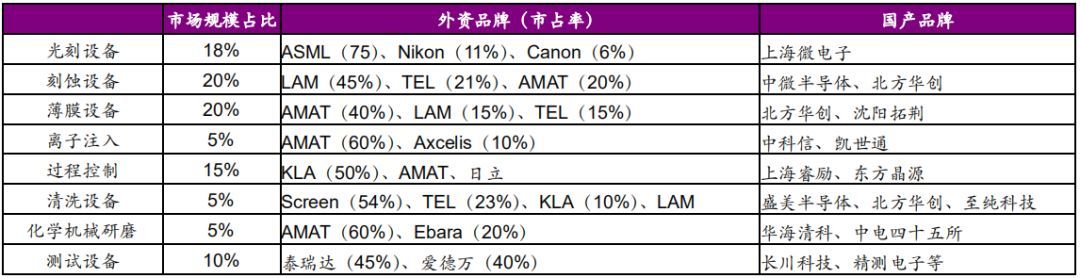

國(guó)產(chǎn)設(shè)備自給率低,進(jìn)口替代空間大。供給端看,根據(jù)中國(guó)電子專(zhuān)用設(shè)備工業(yè)協(xié)會(huì)對(duì)國(guó)內(nèi) 42 家主要半導(dǎo)體設(shè)備制造商的統(tǒng)計(jì),2017 年國(guó)產(chǎn)半導(dǎo)體設(shè)備銷(xiāo)售額為 89 億元,自給率約為 14.3%。中國(guó)電子專(zhuān)用設(shè)備工業(yè)協(xié)會(huì)統(tǒng)計(jì)的數(shù)據(jù)包括 LED、顯示、光伏等設(shè)備,我們認(rèn)為實(shí)際上國(guó)內(nèi)集成電路 IC 設(shè)備國(guó)內(nèi)市場(chǎng)自給率僅有 5%左右,在全球市場(chǎng)僅占 1-2%。

專(zhuān)項(xiàng)頂層設(shè)計(jì),技術(shù)加速追趕。2002 年之前,我國(guó)集成電路設(shè)備基本全進(jìn)口,中國(guó)只有 3 家集成電路設(shè)備廠(chǎng)商,由北方微電子、北京中科信和上海微電子分別承接國(guó)家“863”計(jì)劃中的刻蝕機(jī)、離子注入機(jī)和光刻機(jī)項(xiàng)目。2006 年,《國(guó)家中長(zhǎng)期科學(xué)和技術(shù)發(fā)展規(guī)劃綱要(2006-2020 年)》設(shè)立國(guó)家科技重大專(zhuān)項(xiàng)——極大規(guī)模集成電路制造裝備及成套工藝科技項(xiàng)目(簡(jiǎn)稱(chēng) 02 專(zhuān)項(xiàng))研發(fā)國(guó)產(chǎn)化設(shè)備,并于 2008 年開(kāi)始實(shí)施。2008 年之前我國(guó) 12英寸國(guó)產(chǎn)設(shè)備為空白,只有 2 種 8 英寸設(shè)備。

國(guó)家支持集成電路產(chǎn)業(yè)發(fā)展的部分重點(diǎn)政策

資料來(lái)源:賽迪智庫(kù)在 02 專(zhuān)項(xiàng)的統(tǒng)籌

規(guī)劃下,國(guó)內(nèi)半導(dǎo)體廠(chǎng)商分工合作研發(fā)不同設(shè)備,涵蓋了主要設(shè)備種類(lèi)。目前已有 20 種芯片制造關(guān)鍵裝備、17 種先進(jìn)封裝設(shè)備,通過(guò)大生產(chǎn)線(xiàn)驗(yàn)證進(jìn)入海內(nèi)外銷(xiāo)售。

02 專(zhuān)項(xiàng)支持下國(guó)產(chǎn)設(shè)備廠(chǎng)商產(chǎn)品布局

資料來(lái)源:《中國(guó)集成電路產(chǎn)業(yè)發(fā)展藍(lán)皮書(shū)》中國(guó)電子信息產(chǎn)業(yè)發(fā)展研究院

國(guó)內(nèi) IC 制造設(shè)備工藝覆蓋率仍比較低,國(guó)產(chǎn)廠(chǎng)商技術(shù)加速追趕。國(guó)產(chǎn)全部IC 設(shè)備在邏輯 IC 產(chǎn)線(xiàn)上 65/55nm 工藝覆蓋率才 31%,40nm 工藝覆蓋率僅17%,28nm 工藝覆蓋率僅 16%;在存儲(chǔ)芯片產(chǎn)線(xiàn)上的工藝覆蓋率大概約為15-25%。

隨著摩爾定律放緩,國(guó)產(chǎn)廠(chǎng)商技術(shù)加速追趕。以北方華創(chuàng)刻蝕機(jī)為例,2007 年研發(fā)出 8 寸 100nm 設(shè)備,比國(guó)際大廠(chǎng)晚 8 年;2011 年研發(fā)出 12 寸 65nm 設(shè)備,比國(guó)際大廠(chǎng)晚 6 年;2013 年研發(fā)出 12 寸 28nm 設(shè)備,比國(guó)際大廠(chǎng)晚 3~4 年;2016 年研發(fā) 12 寸 14nm 設(shè)備,比國(guó)際大廠(chǎng)晚 2~3 年。

北方華創(chuàng)刻蝕機(jī)研發(fā)進(jìn)展

資料來(lái)源:北方華創(chuàng)官網(wǎng)

硅片是半導(dǎo)體、光伏電池生產(chǎn)的主要原材料,90%以上的集成電路都是制作在高純、優(yōu)質(zhì)的硅片上的。1、半導(dǎo)體硅片的制造難度大于光伏硅片。半導(dǎo)體硅片純度要求達(dá)到 99.99999999999%,即 11 個(gè) 9 以上,而普通太陽(yáng)能硅片制造難度大,設(shè)備種類(lèi)多級(jí)多晶硅材料純度通常在5-8 個(gè) 9 左右。2、硅片直徑越大制造難度越大。硅片制備工藝流程包括:?jiǎn)尉L(zhǎng)→截?cái)唷鈴綕L磨(定位槽或參考面處理)→切片→倒角→表面磨削→(刻蝕)→邊緣拋光→雙面拋光→單面拋光→最終清洗→(外延/退火)→包裝等。

硅片制造流程

資料來(lái)源:《半導(dǎo)體制造技術(shù)》韓鄭生

硅片直徑的增大可降低單個(gè)芯片的制造成本,目前 300mm 硅片已成為業(yè)內(nèi)主流,2017 年全球 12 寸出貨面積約占硅片總體的 66.1%。

現(xiàn)在:政策需求雙輪驅(qū)動(dòng),大硅片國(guó)產(chǎn)化指日可待。根據(jù) IC Insights 2017數(shù)據(jù),2017 年全球硅片需求 1160 萬(wàn)片(等效 8 寸),國(guó)內(nèi)需求 110 萬(wàn)片。預(yù)計(jì) 2020 年國(guó)內(nèi)對(duì) 12 寸大硅片需求從 42 萬(wàn)片增加到 105 萬(wàn)片;2020 年對(duì) 8 寸硅片需求從 70 萬(wàn)片增加到 96.5 萬(wàn)片。受政策鼓勵(lì)與市場(chǎng)需求的雙重驅(qū)動(dòng),多家企業(yè)正在中國(guó)積極布局半導(dǎo)體大硅片項(xiàng)目。國(guó)內(nèi)規(guī)劃中的 12 寸大硅片合計(jì):145 萬(wàn)片,覆蓋國(guó)內(nèi)需求。國(guó)內(nèi)規(guī)劃中的 8 寸大硅片合計(jì):168 萬(wàn)片,總投資規(guī)模超過(guò) 500 億元,覆蓋國(guó)內(nèi)需求。

過(guò)去:受市場(chǎng)需求不足的影響,產(chǎn)業(yè)化推進(jìn)較為緩慢。我國(guó)的硅片制備設(shè)備經(jīng)過(guò)了 30 多年的發(fā)展,已可提供直徑 200mm 以下的硅片制備設(shè)備,但受市場(chǎng)需求量較少和國(guó)外二手設(shè)備的沖擊,國(guó)產(chǎn)設(shè)備發(fā)展的門(mén)類(lèi)并不齊全。在300mm 硅片制備設(shè)備的發(fā)展上,國(guó)內(nèi)研發(fā)了單晶爐、多線(xiàn)切割機(jī)等幾種關(guān)鍵設(shè)備,也通過(guò)了 300mm 硅片生產(chǎn)試驗(yàn)線(xiàn)的驗(yàn)證。但與國(guó)外設(shè)備相比,受市場(chǎng)需求不足的影響,產(chǎn)業(yè)化推進(jìn)較為緩慢,同時(shí)也影響了設(shè)備技術(shù)的進(jìn)步。

硅片設(shè)備產(chǎn)業(yè)化推進(jìn)加快,國(guó)產(chǎn)廠(chǎng)商迎來(lái)發(fā)展良機(jī)。單晶爐方面,晶盛機(jī)電承擔(dān)的 02 專(zhuān)項(xiàng)“300mm 硅單晶直拉生長(zhǎng)設(shè)備的開(kāi)發(fā)”、“8 英寸區(qū)熔硅單晶爐國(guó)產(chǎn)設(shè)備研制”兩大項(xiàng)目均已通過(guò)專(zhuān)家組驗(yàn)收,8 寸直拉單晶爐和區(qū)熔單晶爐均已實(shí)現(xiàn)產(chǎn)業(yè)化,客戶(hù)包括有研半導(dǎo)體、環(huán)歐半導(dǎo)體、金瑞泓等;12 寸直拉單晶爐產(chǎn)業(yè)化推進(jìn)中,未來(lái)有望為國(guó)內(nèi)大硅片項(xiàng)目供貨。南京晶能 12 寸直拉單晶爐已進(jìn)入新昇半導(dǎo)體大硅片產(chǎn)線(xiàn)。

光刻機(jī)發(fā)展歷史

在集成電路制造工藝中,光刻是決定集成電路集成度的核心工序,該工序的 作用是將電路圖形信息從掩模版上保真?zhèn)鬏敗⑥D(zhuǎn)印到半導(dǎo)體材料襯底上。光 刻工藝的基本原理是,利用涂敷在襯底表面的光刻膠的光化學(xué)反應(yīng)作用,記 錄掩模版上的電路圖形,從而實(shí)現(xiàn)將集成電路圖形從設(shè)計(jì)轉(zhuǎn)印到襯底的目的。

光刻工藝的基本原理

資料來(lái)源:SMEE

光刻機(jī)分為無(wú)掩模光刻機(jī)和有掩模光刻機(jī)兩大類(lèi)。

無(wú)掩模光刻機(jī)又稱(chēng)直寫(xiě)光刻機(jī),按照所采用的輻射源的不同可分為電子束直寫(xiě)光刻機(jī)、離子束直寫(xiě)光刻機(jī)、激光直寫(xiě)光刻機(jī),分別用于不同的特定應(yīng)用領(lǐng)域。例如,電子束直寫(xiě)光刻機(jī)主要用于高分辨率掩模版、集成電路原型驗(yàn)證芯片的制造,以及特種器件的小批量制造;激光直寫(xiě)光刻機(jī)主要用于特定的小批量芯片的制造。

光刻機(jī)分類(lèi)

資料來(lái)源:SMEE

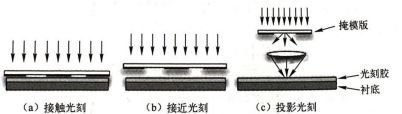

有掩模光刻機(jī)又分為接觸/接近式光刻機(jī)和投影式光刻機(jī)。接觸式光刻出現(xiàn)于20 世紀(jì) 60 年代,是小規(guī)模集成電路(SSI)時(shí)代的主要光刻手段,主要用于生產(chǎn)制程在 5μm 以上的集成電路。接近式光刻機(jī)于 20 世紀(jì) 70 年代在小規(guī)模集成電路與中規(guī)模集成電路(MSI)時(shí)代早期被廣泛應(yīng)用,主要用于生產(chǎn)制程在 3μm 以上的集成電路。目前接觸接近式光刻機(jī)的國(guó)外生產(chǎn)商主要有德國(guó)的蘇斯公司、奧地利 EVG 公司,國(guó)內(nèi)生產(chǎn)商主要有中電科 45 所、中科院光電技術(shù)研究所等。

接觸/接近式光刻機(jī)和投影式光刻機(jī)

資料來(lái)源:SMEE

投影光刻機(jī)自 20 世紀(jì) 70 年代中后期開(kāi)始替代接觸接近式光刻機(jī),是先進(jìn)集成電路大批量制造中的唯一光刻形式。早期的投影光刻機(jī)的掩模版與襯底 圖形尺寸比例為 1:1,通過(guò)掃描方式完成整個(gè)襯底的曝光過(guò)程。

隨著集成電路特征尺寸的不斷縮小和襯底尺寸的增大,縮小倍率的步進(jìn)重復(fù)光刻機(jī)問(wèn)世, 替代了圖形比例為 1:1 的掃描光刻方式。當(dāng)集成電路圖形特征尺寸小于0.25μm 時(shí),由于集成電路集成度的進(jìn)一步提高,芯片面積更大,要求一次曝光的面積增大,促使更為先進(jìn)的步進(jìn)掃描光刻機(jī)問(wèn)世。

通過(guò)配置不同的曝 光光源,步進(jìn)掃描技術(shù)可支撐不同的工藝技術(shù)節(jié)點(diǎn),從 KrF248mm 、ArF193mm、ArF193mm 浸沒(méi)式,直至 EUV 光刻。在 0.18μm 工藝節(jié)點(diǎn)后, 高端光刻機(jī)廠(chǎng)商基本采用步進(jìn)掃描技術(shù),并一直沿用至今。

投影光刻機(jī)的基本分辨率R=K1*λ/NA,其中 K1 為工藝因子,根據(jù)衍射成像原理,其理論極限值是 0.25;NA 為光刻機(jī)成像物鏡的數(shù)值孔徑;λ 為所使用的光源的波長(zhǎng)。提高投影光刻機(jī)分辨率的理論和工程途徑是增大數(shù)值孔徑NA,縮減波長(zhǎng) λ,減小 K1。

為了提高光刻分辨率,在采用準(zhǔn)分子光源后進(jìn)一步縮短曝光波長(zhǎng),引入波長(zhǎng)10~14mm 的極紫外光 EUV 作為曝光光源。EUV 光刻機(jī)研發(fā)難度及費(fèi)用極大,英特爾、三星和臺(tái)積電都曾對(duì)光刻機(jī)龍頭 ASML 投資,以支持 EUV 光刻設(shè)備研發(fā),并希望取得EUV 設(shè)備的優(yōu)先權(quán)。ASML 從事 EUV 光刻機(jī)的研制已是第 12 個(gè)年頭了,甚于“十年磨一劍”。2017 年,姍姍來(lái)遲的 EUV 光刻機(jī)終于進(jìn)入了量產(chǎn)階段。

ASML 光刻機(jī)發(fā)展歷程

資料來(lái)源:ASML

光刻機(jī)競(jìng)爭(zhēng)格局

步進(jìn)掃描投影光刻機(jī)的主要生產(chǎn)廠(chǎng)商包括ASML(荷蘭)、尼康(日本)、佳能(日本)和SMEE (中國(guó))。ASML 于 2001 年推出了 TWINSCAN 系列步進(jìn)掃描光刻機(jī),采用雙工件臺(tái)系統(tǒng)架構(gòu),可以有效提高設(shè)備產(chǎn)出率,已成為應(yīng)用最為廣泛的高端光刻機(jī)。ASML 在光刻機(jī)領(lǐng)域一騎絕塵,一家獨(dú)占全球 70%以上的市場(chǎng)份額。國(guó)內(nèi)廠(chǎng)商上海微電子 (SMEE)研制的 90nm 高端步進(jìn)掃描投影光刻機(jī)已完成整機(jī)集成測(cè)試,并在客戶(hù)生產(chǎn)線(xiàn)上進(jìn)行了工藝試驗(yàn)。

步進(jìn)式掃描光刻機(jī)主要廠(chǎng)商機(jī)型信息

資料來(lái)源:SMEE

晶圓制造設(shè)備——刻蝕機(jī)

刻蝕原理及分類(lèi)

刻蝕是使用化學(xué)或者物理方法有選擇地從硅片表面去除不需要材料的過(guò)程。通常的晶圓加工流程中,刻蝕工藝位于光刻工藝之后,有圖形的光刻膠層在刻蝕中不會(huì)受到腐蝕源的顯著侵蝕,從而完成圖形轉(zhuǎn)移的工藝步驟。

刻蝕原理示意圖

資料來(lái)源:《半導(dǎo)體制造技術(shù)》MichaelQuirk

刻蝕分為濕法刻蝕和干法刻蝕兩種。早期普遍采用的是濕法刻蝕,但由于其在線(xiàn)寬控制及刻蝕方向性等多方面的局限,3μm 之后的工藝大多采用干法刻蝕,濕法刻蝕僅用于某些特殊材料層的去除和殘留物的清洗。

干法刻蝕也稱(chēng)等離子刻蝕。干法刻蝕是指使用氣態(tài)的化學(xué)刻蝕劑(Etchant) 與圓片上的材料發(fā)生反應(yīng),以刻蝕掉需去除的部分材料并形成可揮發(fā)性的反應(yīng)生成物,然后將其抽離反應(yīng)腔的過(guò)程。刻蝕劑通常直接或間接地產(chǎn)生于刻蝕氣體的等離子體,所以干法刻蝕也稱(chēng)等離子體刻蝕。

等離子體刻蝕機(jī)可以根據(jù)等離子體產(chǎn)生和控制技術(shù)的不同而大致分為兩大類(lèi),即電容耦合等離子體(capacitively coupled plasma,CCP)刻蝕機(jī)和電感耦合等離子體(Inductively coupled plasma,ICP)刻蝕機(jī)。在集成電路生產(chǎn)線(xiàn)上,等離子體刻蝕設(shè)備通常按照被刻蝕材料的種類(lèi)分為硅刻蝕設(shè)備、金屬刻蝕設(shè)備和電介質(zhì)刻蝕設(shè)備三大類(lèi)。

CCP 刻蝕機(jī)主要用于電介質(zhì)材料的刻蝕工藝,如邏輯芯片工藝前段的柵側(cè)墻和硬掩模刻蝕,中段的接觸孔刻蝕,后段的鑲嵌式和鋁墊刻蝕等,以及在 3D 閃存芯片工藝(以氮化硅/氧化硅結(jié)構(gòu)為例)中的深槽、深孔和連線(xiàn)接觸孔的刻蝕等。

ICP 刻蝕機(jī)主要用于硅刻蝕和金屬刻蝕,包括對(duì)硅淺溝槽(STI)、鍺(Ge)、多晶硅柵結(jié)構(gòu)、金屬柵結(jié)構(gòu)、應(yīng)變硅(Strained-Si)、金屬導(dǎo)線(xiàn)、金屬焊墊(Pad)、鑲嵌式刻蝕金屬硬掩模和多重成像(Multiple Patteming)技術(shù)中的多道工序的刻蝕等。另外,隨著三維集成電路(3D IC)、CMOS 圖像傳感器(CIS)和微機(jī)電系統(tǒng)(MEMS)的興起,以及硅通孔(TSV)、大尺寸斜孔槽和不同形貌的深硅刻蝕應(yīng)用的快速增加,多個(gè)廠(chǎng)商推出了專(zhuān)為這些應(yīng)用而開(kāi)發(fā)的刻蝕設(shè)備。

隨著工藝要求的專(zhuān)門(mén)化、精細(xì)化,刻蝕設(shè)備的多樣化,以及新型材料的應(yīng)用, 上述分類(lèi)方法已變得越來(lái)越模糊。除了集成電路制造領(lǐng)域,等離子體刻蝕還被廣泛用于 LED、MEMS 及光通信等領(lǐng)域。

刻蝕機(jī)行業(yè)發(fā)展趨勢(shì)及競(jìng)爭(zhēng)格局

隨著芯片集成度的不斷提高,生產(chǎn)工藝越來(lái)越復(fù)雜,刻蝕在整個(gè)生產(chǎn)流程中的比重也呈上升趨勢(shì)。因此,刻蝕機(jī)支出在生產(chǎn)線(xiàn)設(shè)備總支出中的比重也在增加。而刻蝕機(jī)按刻蝕材料細(xì)分后的增長(zhǎng)速度,則根據(jù)工藝技術(shù)的發(fā)展階段不同呈現(xiàn)此消彼長(zhǎng)的狀況。例如,當(dāng) 0.13μm 工藝的銅互連技術(shù)出現(xiàn)時(shí),金屬刻蝕設(shè)備的占比大幅下降,而介質(zhì)刻蝕設(shè)備的占比大幅上升;30nm 之后的工藝中出現(xiàn)的多重圖像技術(shù)及越來(lái)越多的軟刻蝕應(yīng)用,則使得硅刻蝕設(shè)備的占比快速增加。

國(guó)際巨頭泛林集團(tuán)、東京電子、應(yīng)用材料均實(shí)現(xiàn)了硅刻蝕、介質(zhì)刻蝕、金屬刻蝕的全覆蓋,占據(jù)了全球干法刻蝕機(jī)市場(chǎng)的 80%以上份額。國(guó)內(nèi)廠(chǎng)商中微半導(dǎo)體在介質(zhì)刻蝕領(lǐng)域較強(qiáng),其產(chǎn)品已在包括臺(tái)積電、海力士、中芯國(guó)際等。

芯片生產(chǎn)商的 20 多條生產(chǎn)線(xiàn)上實(shí)現(xiàn)了量產(chǎn);5nm 等離子體蝕刻機(jī)已成功通過(guò)臺(tái)積電驗(yàn)證,將用于全球首條 5nm 工藝生產(chǎn)線(xiàn);同時(shí)已切入 TSV 硅通孔刻蝕和金屬硬掩膜刻蝕領(lǐng)域。北方華創(chuàng)在硅刻蝕和金屬刻蝕領(lǐng)域較強(qiáng),其55/65nm 硅刻蝕機(jī)已成為中芯國(guó)際Baseline 機(jī)臺(tái),28nm 硅刻蝕機(jī)進(jìn)入產(chǎn)業(yè)化階段,14nm 硅刻蝕機(jī)正在產(chǎn)線(xiàn)驗(yàn)證中,金屬硬掩膜刻蝕機(jī)攻破 28-14nm 制程。

晶圓制造設(shè)備——薄膜生長(zhǎng)設(shè)備

采用物理或化學(xué)方法是物質(zhì)(原材料)附著于襯底材料表面的過(guò)程即為薄膜生長(zhǎng)。薄膜生長(zhǎng)廣泛用于集成電路、先進(jìn)封裝、發(fā)光二極管、MEMS、功率器件、平板顯示等領(lǐng)域。

薄膜生長(zhǎng)工藝類(lèi)型

資料來(lái)源:北方華創(chuàng)《集成電路專(zhuān)用設(shè)備-薄膜設(shè)備》

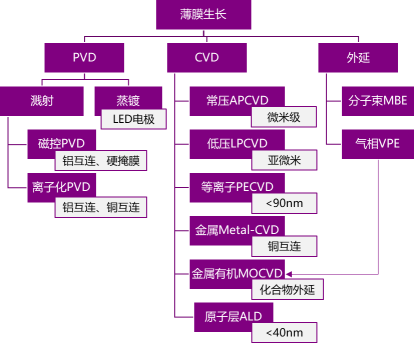

根據(jù)工作原理的不同,集成電路薄膜沉積可分為物理氣相沉積(PVD)、化學(xué)氣相沉積(CVD)和外延三大類(lèi)。

PVD 是指利用熱蒸發(fā)或受到粒子轟擊時(shí)物質(zhì)表面原子的濺射等物理過(guò)程,實(shí)現(xiàn)物質(zhì)原子從源物質(zhì)到襯底材料表面的物質(zhì)轉(zhuǎn)移,從而在襯底表面沉積形成薄膜的技術(shù)。PVD 可以分為真空蒸鍍和濺射兩種類(lèi)型。目前蒸鍍主要應(yīng)用于LED 電極制造,而主流 IC 制造領(lǐng)域已經(jīng)不再采用此類(lèi)設(shè)備進(jìn)行薄膜制備。濺射 PVD 廣泛應(yīng)用于集成電路后道互連工藝中金屬薄膜制備。

磁控直流DCPVD 可用于平面薄膜制備,如鋁互連和 28nm 氮化鈦硬掩膜,但在銅互連中應(yīng)用減少。離子化 PVD 是磁控 DCPVD 中的一種新技術(shù),可用于鋁互連的隔離層、鎢栓塞的粘附層,以及銅互連中的隔離層和籽晶層。同時(shí),離子化PVD 和金屬CVD 腔室可以結(jié)合在一個(gè)系統(tǒng)中,比如鎢栓塞的粘附層(鈦離子PVD)和隔離層(氮化鈦 CVD)。

薄膜生長(zhǎng)設(shè)備

資料來(lái)源:北方華創(chuàng) 《集成電路專(zhuān)用設(shè)備-薄膜設(shè)備》

CVD 是通過(guò)混合化學(xué)氣體并發(fā)生化學(xué)反應(yīng),從而在襯底表面沉積薄膜的一種工藝,用于沉積的材料包括金屬材料(W, TIN, Co)、介電材料(Si02、Si, N4、摻磷二氧化硅、摻硼磷二氧化硅)和半導(dǎo)體材料(多晶硅、無(wú)晶硅)等。

在微米技術(shù)代,化學(xué)氣相沉積均采取多片式的常壓化學(xué)氣相沉積設(shè)備(APCVD),其結(jié)構(gòu)比較簡(jiǎn)單,圓片的傳輸和工藝是連續(xù)的。

1、在亞微米技術(shù)代,低壓化學(xué)氣相沉積設(shè)備(LPCVD)成為主流設(shè)備, 其工作壓力大大降低,從而改善了沉積薄膜的均勻性和溝槽覆蓋填充能力。

2、從 90nm 技術(shù)代開(kāi)始,等離子體增強(qiáng)化學(xué)氣相沉積設(shè)備(PECVD) 扮演了重要的角色。由于等離子體的作用,化學(xué)反應(yīng)溫度明顯降低, 薄膜純度得到提高,薄膜密度得以加強(qiáng)。

3、從 180nm 技術(shù)代開(kāi)始,Cu 取代 Al 作為金屬互連材料。金屬栓塞工藝模塊中的 TIN 阻擋層和W 栓塞均是采用金屬化學(xué)氣相沉積(金屬 Metal-CVD)完成的。

4、從 45nm 技術(shù)代開(kāi)始,為了減小器件的漏電流,新的高介電材料(High k)材料及金屬柵(Metal Gate)工藝被應(yīng)用到集成電路工藝中, 由于膜層非常薄,通常在數(shù)納米量級(jí)內(nèi),所以不得不引入原子層沉積(ALD)的工藝設(shè)備,以滿(mǎn)足對(duì)薄膜沉積的控制和薄膜均勻性的需求。

5、MOCVD 主要用于制備半導(dǎo)體光電子、微電子器件領(lǐng)域的各種砷化鎵、氮化鎵等三五族化合物,在 LED、激光器、高頻電子器件和太陽(yáng)能電池等領(lǐng)域具有規(guī)模化生產(chǎn)的能力。

外延是一種在晶片等單晶襯底上按照襯底晶向生長(zhǎng)單晶薄膜的工藝過(guò)程。根據(jù)外延生長(zhǎng)材料的不同,外延可以分為同質(zhì)外延和異質(zhì)外延。同質(zhì)外延是指生長(zhǎng)的外延層和襯底是同一種材料,異質(zhì)外延是指外延生長(zhǎng)的薄膜材料與襯底材料不同,如 SPS 技術(shù)(在藍(lán)寶石或尖晶石上生長(zhǎng)硅)。根據(jù)外延技術(shù)可分為分子束外延、氣相外延、液相外延等。MOCVD 也可作為氣相外延的一種。

PVD 領(lǐng)域,AMAT 一家獨(dú)大,約占全球市場(chǎng)份額的 80%以上;CVD 領(lǐng)域, AMAT、LAM、TEL 三家約占全球市場(chǎng)份額的 70%以上。國(guó)內(nèi)設(shè)備廠(chǎng)商中北方華創(chuàng)薄膜設(shè)備產(chǎn)品種類(lèi)最多,目前其 28nm 硬掩膜 PVD 已實(shí)現(xiàn)銷(xiāo)售,銅互連PVD、14nm 硬掩膜PVD、Al PVD、LPCVD、ALD 設(shè)備已進(jìn)入產(chǎn)線(xiàn)驗(yàn)證。中微半導(dǎo)體的 MOCVD 在國(guó)內(nèi)已實(shí)現(xiàn)國(guó)產(chǎn)替代。沈陽(yáng)拓荊的 65nm PECVD 已實(shí)現(xiàn)銷(xiāo)售。

晶圓制造設(shè)備——擴(kuò)散及離子注入設(shè)備

在集成電路制造過(guò)程中,摻雜主要有擴(kuò)散和離子注入兩種工藝,擴(kuò)散屬于高溫工藝,而離子注入工藝屬于低溫工藝。

擴(kuò)散工藝是向硅材料中引人雜質(zhì)的一種傳統(tǒng)方法,控制圓片襯底中主要載流子的類(lèi)型、濃度和分布區(qū)域,進(jìn)而控制襯底的導(dǎo)電性和導(dǎo)電類(lèi)型。擴(kuò)散工藝設(shè)備簡(jiǎn)單,擴(kuò)散速率快,摻雜濃度高,但擴(kuò)散溫度高,擴(kuò)散濃度分布控制困難,難以實(shí)現(xiàn)選擇性擴(kuò)散。

離子注入工藝是指使具有一定能量的帶電粒子(離子)高速轟擊硅襯底并將其注入硅襯底的過(guò)程。離子注入能夠在較低的溫度下,可選擇的雜質(zhì)種類(lèi)多, 摻雜劑量控制準(zhǔn)確,可以向淺表層引人雜質(zhì),但設(shè)備昂貴,大劑量摻雜耗時(shí)較長(zhǎng),存在隧道效應(yīng)和注人損傷。

資料來(lái)源:光大證券研究所整理

擴(kuò)散爐分類(lèi)及競(jìng)爭(zhēng)格局

擴(kuò)散爐廣泛用于分立器件、電力電子、光電器件和光導(dǎo)纖維等行業(yè)的擴(kuò)散、氧化、退火、合金等工藝中,因此按照功能不同,有時(shí)也稱(chēng)擴(kuò)散爐為退火爐、氧化爐。擴(kuò)散爐主要分為臥式擴(kuò)散爐和立式擴(kuò)散爐。

臥室擴(kuò)散爐(一般用于 8 英寸以下)

資料來(lái)源:北方華創(chuàng)《集成電路專(zhuān)用設(shè)備-擴(kuò)散爐設(shè)備》

臥式擴(kuò)散爐是一種在圓片直徑小于 200mm 的集成電路擴(kuò)散工藝中大量使用的熱處理設(shè)備,其特點(diǎn)是加熱爐體、反應(yīng)管及承載圓片的石英舟(Quartz Boat) 均呈水平放置,因而具有片間均勻性好的工藝特點(diǎn)。

立式擴(kuò)散爐(一般用于 8 和 12 英寸)

資料來(lái)源:北方華創(chuàng)《集成電路專(zhuān)用設(shè)備-擴(kuò)散爐設(shè)備》

立式擴(kuò)散爐泛指應(yīng)用于直徑為 200mm 和 300mm 圓片的集成電路工藝中的- 種批量式熱處理設(shè)備,俗稱(chēng)立式爐。立式擴(kuò)散爐的結(jié)構(gòu)特點(diǎn)是,加熱爐體、反應(yīng)管及承載圓片的石英舟均垂直放置(圓片呈水平放置狀態(tài)),具有片內(nèi)均勻性好、自動(dòng)化程度高、系統(tǒng)性能穩(wěn)定的特點(diǎn),符合SEMI 標(biāo)準(zhǔn)要求,可以滿(mǎn)足大規(guī)模集成電路生產(chǎn)線(xiàn)的需求。立式擴(kuò)散爐是半導(dǎo)體集成電路生產(chǎn)線(xiàn)的重要設(shè)備之一,也常應(yīng)用于電力電子器件(如 ICBT)等領(lǐng)域的相關(guān)工藝。立式擴(kuò)散適用的工藝包括干氧氧化、氫氧合成氧化、DCE (二氯乙烯)氧化、氨氧化硅氧化等氧化工藝,以及二氧化硅、多晶硅(Poly-si)、氮化硅(SiN)、原子層沉積(ALD)等薄膜生長(zhǎng)工藝,也常用于高溫退火、銅退火(Cu Anneal) 及合金(Alloy)等工藝。

擴(kuò)散設(shè)備方面,臥室擴(kuò)散爐較為簡(jiǎn)單,國(guó)內(nèi)基本能實(shí)現(xiàn)自給自足,設(shè)備廠(chǎng)商主要有北方華創(chuàng)、中電科第 48 所等。立式擴(kuò)散/氧化爐設(shè)備門(mén)檻較高,全球主要廠(chǎng)商有東京電子(TEL)、日立國(guó)際(HKE)等,單臺(tái)平均售價(jià)約為 80 萬(wàn)美元,國(guó)內(nèi)仍主要依賴(lài)進(jìn)口,只有北方華創(chuàng)公司能夠小批量提供 300mm 立式爐產(chǎn)品。

傳統(tǒng)的退火爐使用類(lèi)似臥式擴(kuò)散爐的爐管系統(tǒng),一般用于直徑小于 200mm 的晶圓制造。而 200mm 或者 300mm 的大尺寸晶圓一般采用立式爐及單片快速熱處理(RTP)設(shè)備。相對(duì)于爐管加熱退火,RTP 具有熱預(yù)算少,摻雜區(qū)域中雜質(zhì)運(yùn)動(dòng)范圍小,沾污小和加工時(shí)間短等優(yōu)點(diǎn)。RTP 設(shè)備門(mén)檻高,主要由應(yīng)用材料公司、Axcelis Technology、Mattson Technology 和 ASM 等 4 家公司壟斷,約占全球 90%的市場(chǎng)份額。

離子注入機(jī)是集成電路裝備中較為復(fù)雜的設(shè)備之,根據(jù)注入離子的能量和劑量的不同,離子注入機(jī)大體分為低能大束流離子注入機(jī)、中束流離子注入機(jī)和高能離子注入機(jī) 3 種類(lèi)型。其中,低能大束流離子注入機(jī)是目前占有率最高的注入機(jī),適用于大劑量及淺結(jié)注入,如源漏極擴(kuò)展區(qū)注入、源漏極注入、柵極摻雜以及預(yù)非晶化注入等多種工藝。中束流離子注入機(jī)可應(yīng)用于半導(dǎo)體制造中的溝道、阱和源漏極等多種工藝。高能離子注入機(jī)在邏輯、存儲(chǔ)、成像器件、功率器件等領(lǐng)域應(yīng)用廣泛。

離子注入設(shè)備廠(chǎng)商主要有美國(guó)的 AMAT、Axcelis 等。國(guó)內(nèi)生產(chǎn)線(xiàn)上使用的離子注入機(jī)多數(shù)依賴(lài)進(jìn)口,國(guó)內(nèi)北京中科信、中電科 48 所、上海凱世通等也能提供少量產(chǎn)品。其中,中科信公司已具備不同種類(lèi)(低能大束流、中束流和高能)離子注入機(jī)上線(xiàn)機(jī)型的量產(chǎn)能力。

晶圓制造設(shè)備——濕法設(shè)備

濕法工藝是指在集成電路制造過(guò)程中需要使用化學(xué)藥液的工藝,主要有濕法清洗、化學(xué)機(jī)械拋光和電鍍?nèi)箢?lèi)。

濕法清洗是指針對(duì)不同的工藝需求,采用特定的化學(xué)藥液和去離子水,對(duì)圓片表面進(jìn)行無(wú)損傷清洗,以去除集成電路制造過(guò)程中的顆粒、自然氧化層、有機(jī)物、金屬污染、犧牲層、拋光殘留物等物質(zhì)。

清洗機(jī)主要分為槽式清洗機(jī)和單圓片清洗機(jī)。槽式清洗技術(shù)是由美國(guó)無(wú)線(xiàn)電公司(RCA)于 1970 年提出的,它是通過(guò)多個(gè)化學(xué)槽體、去離子水槽體和干燥槽體的配合使用,完成圓片清洗工藝。

隨著 28nm 及更先進(jìn)工藝的濕法清洗對(duì)圓片表面小顆粒的數(shù)量及刻蝕均勻性的要求越來(lái)越高,同時(shí)必須達(dá)到圖形無(wú)損干燥。而槽式圓片清洗機(jī)的槽體內(nèi)部化學(xué)藥液的差異性、干燥方式,以及與圓片接觸點(diǎn)過(guò)多,導(dǎo)致無(wú)法滿(mǎn)足這些工藝需求,現(xiàn)已逐漸被單圓片清洗機(jī)取代,目前槽式圓片清洗機(jī)在整個(gè)清洗流程中約占 20%的步驟。

槽式圓片清洗機(jī)主要廠(chǎng)商有日本的迪恩士(SCREEN)、東京電子(Tokyo Electron)和 JET,三家約占全球 75%以上的市場(chǎng)份額。韓國(guó)的 SEMES 和KCTECH 主要供給韓國(guó)市場(chǎng)。

單圓片清洗設(shè)機(jī)主要廠(chǎng)商有日本的迪恩士、東京電子和美國(guó)泛林集團(tuán)提供, 三家約占全球 70%以上的市場(chǎng)份額。在國(guó)內(nèi)的單圓片濕法設(shè)備廠(chǎng)商中,盛美半導(dǎo)體獨(dú)家開(kāi)發(fā)的空間交變相位移(SAPS)兆聲波清洗設(shè)備和時(shí)序氣穴振蕩控制(TEBO)兆聲波清洗設(shè)備已經(jīng)成功進(jìn)入韓國(guó)及中國(guó)的集成電路生產(chǎn)線(xiàn)并 用于大規(guī)模生產(chǎn)。北方華創(chuàng)的清洗機(jī)也成功進(jìn)入中芯國(guó)際生產(chǎn)線(xiàn)。

(SAPS)兆聲波清洗設(shè)備技術(shù)原理

資料來(lái)源:盛美半導(dǎo)體《集成電路專(zhuān)用設(shè)備-濕法設(shè)備》

化學(xué)機(jī)械拋光(CMP)是指圓片表面材料與研磨液發(fā)生化學(xué)反應(yīng)時(shí),在研磨頭下壓力的作用下進(jìn)行拋光,使圓片表面平坦化的過(guò)程。

圓片表面材料包括多晶硅、二氧化硅、金屬鎢、金屬銅等,與之相對(duì)應(yīng)的是不同種類(lèi)的研磨液。

化學(xué)機(jī)械拋光能夠?qū)⒄麄€(gè)圓片高低起伏的表面研磨成一致的厚度,是一種圓片全局性的平坦化工藝。

CMP 工藝在芯片制造中的應(yīng)用包括淺溝槽隔離平坦化(STI CMP)、多晶硅平坦化(Poly CMP)、層間介質(zhì)平坦化(ILD CMP)、金屬間介質(zhì)平坦化(IMDCMP)、銅互連平坦化(Cu CMP)。

CMP 設(shè)備主要分為兩部分,即拋光部分和清洗部分。拋光部分由 4 部分組成,即 3 個(gè)拋光轉(zhuǎn)盤(pán)和一個(gè)圓片裝卸載模塊。清洗部分負(fù)責(zé)圓片的清洗和甩干,實(shí)現(xiàn)圓片的“干進(jìn)干出”。

化學(xué)機(jī)械拋光(CMP)原理

資料來(lái)源:盛美半導(dǎo)體《集成電路專(zhuān)用設(shè)備-濕法設(shè)備》

化學(xué)機(jī)械拋光(CMP)配套設(shè)備

資料來(lái)源:盛美半導(dǎo)體《集成電路專(zhuān)用設(shè)備-濕法設(shè)備》

CMP 設(shè)備主要生產(chǎn)商有美國(guó) AMAT 和日本 Ebara,其中 AMAT 約占 CMP 設(shè)備市場(chǎng) 60%的份額,Ebara 約占 20%的份額。國(guó)內(nèi) CMP 設(shè)備的主要研發(fā)單位有天津華海清科和中電科 45 所,其中華海清科的拋光機(jī)已在中芯國(guó)際生產(chǎn)線(xiàn)上試用。

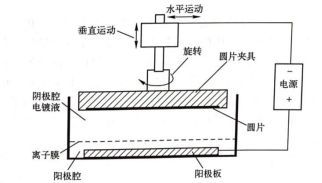

電鍍是指在集成電路制造過(guò)程中,用于加工芯片之間互連金屬線(xiàn)所采用的電化學(xué)金屬沉積。隨著集成電路制造工藝的不斷發(fā)展,目前電鍍已經(jīng)不限于銅線(xiàn)的沉積,還涉及錫、錫銀合金、鎳等金屬的沉+積,但金屬銅的沉積仍是其中最主要的部分。

電鍍?cè)?/p>

資料來(lái)源:盛美半導(dǎo)體《集成電路專(zhuān)用設(shè)備-濕法設(shè)備》

電鍍?cè)O(shè)備主要的生產(chǎn)商包括 Lam Research、AMAT 以及 TEL。其中,Lam Research 在前道的鑲嵌式技術(shù)電鍍銅設(shè)備中占據(jù) 90%以上的市場(chǎng)份額,日本的東京電子在先進(jìn)封裝領(lǐng)域約占據(jù) 50%市場(chǎng)。盛美半導(dǎo)體設(shè)備已經(jīng)掌握了電鍍機(jī)的核心專(zhuān)利技術(shù),包括多圓環(huán)陽(yáng)極技術(shù)和兆聲波輔助電鍍技術(shù)等, 自主開(kāi)發(fā)了Utra ECP 系列電鍍機(jī)。

晶圓制造設(shè)備——工藝檢測(cè)設(shè)備

工藝檢測(cè)設(shè)備是應(yīng)用于工藝過(guò)程中的測(cè)量類(lèi)設(shè)備和缺陷(含顆粒)檢查類(lèi)設(shè)備的統(tǒng)稱(chēng)。集成電路芯片制造工藝流程中在線(xiàn)使用的工藝檢測(cè)設(shè)備種類(lèi)繁多, 應(yīng)用于前段芯片制造工藝的主要檢測(cè)設(shè)備分為:圓片表面的顆粒和殘留異物檢查;薄膜材料的厚度和物理常數(shù)的測(cè)量;圓片在制造過(guò)程中關(guān)鍵尺寸(CD) 和形貌結(jié)構(gòu)的參數(shù)測(cè)量;套刻對(duì)準(zhǔn)的偏差測(cè)量。

隨著芯片結(jié)構(gòu)的不斷細(xì)微化和工藝的不斷復(fù)雜化,工藝檢測(cè)設(shè)備在先進(jìn)的前段生產(chǎn)線(xiàn)中起著越來(lái)越重要的作用。目前工藝檢測(cè)設(shè)備投資占整個(gè)前端工藝設(shè)備總投資的 10%~15%。

工藝檢測(cè)設(shè)備的供應(yīng)商主要有科磊半導(dǎo)體、應(yīng)用材料、日立高新等,國(guó)內(nèi)廠(chǎng)商主要有上海睿勵(lì)科學(xué)儀器和深圳中科飛測(cè)科技。

封裝測(cè)試設(shè)備

根據(jù) SEMI 數(shù)據(jù),2017 年全球封裝測(cè)試設(shè)備市場(chǎng)高速增長(zhǎng) 27.89%,銷(xiāo)售額達(dá)到 83.1 億美元。2017 年中國(guó)大陸半導(dǎo)體封裝測(cè)試設(shè)備與封裝模具市場(chǎng)增長(zhǎng)了18.6%,達(dá)到 206.1 億元,約為 30.53 億美元(按統(tǒng)計(jì)局 2017 年度平均匯率計(jì)笲:1 美元=6.75 元),其中封裝設(shè)備市場(chǎng) 14 億美元,測(cè)試設(shè)備與封裝模具市場(chǎng)為 16.53 億美元。2017 年國(guó)內(nèi)半導(dǎo)體設(shè)備市場(chǎng)規(guī)模為 82.3 億美元,封裝測(cè)試設(shè)備占比超過(guò) 1/3,達(dá)到 37.1%。

全球半導(dǎo)體封測(cè)設(shè)備市場(chǎng)規(guī)模及增速

資料來(lái)源:SEMI

國(guó)內(nèi)半導(dǎo)體封測(cè)設(shè)備市場(chǎng)規(guī)模及增速

資料來(lái)源:SEMI

封裝設(shè)備

封裝和組裝可分為四級(jí),即芯片級(jí)封裝(0 級(jí)封裝)、元器件級(jí)封裝(1 級(jí)封裝)、板卡級(jí)組裝(2 級(jí)封裝)和整機(jī)組裝(3 級(jí)封裝)。在 0 級(jí)封裝階段,為了實(shí)現(xiàn)圓片的測(cè)試、減薄、劃切工藝,與之對(duì)應(yīng)的主要封裝設(shè)備有圓片探針臺(tái)、圓片減薄機(jī)、砂輪和激光切割機(jī)等。在 1 級(jí)封裝階段,為了實(shí)現(xiàn)芯片的互連與封裝工藝,與之對(duì)應(yīng)的主要封裝設(shè)備有黏片機(jī)、引線(xiàn)鍵合機(jī)、芯片倒裝機(jī)、塑封機(jī)、切筋成型機(jī)、引線(xiàn)電鍍機(jī)和激光打標(biāo)機(jī)等。在此階段,為了實(shí)現(xiàn)圓片級(jí)芯片尺寸封裝(WLCSP)工藝,相應(yīng)的主要封裝設(shè)備還有植球機(jī)、圓片凸點(diǎn)制造設(shè)備、圓片級(jí)封裝的金屬沉積設(shè)備及光刻設(shè)備等。在 2 級(jí)封裝階段,為了實(shí)現(xiàn) PCB 組裝工藝,與之對(duì)應(yīng)的主要封裝設(shè)備有焊膏涂覆設(shè)備、絲網(wǎng)印刷機(jī)、點(diǎn)膠機(jī)、貼片機(jī)、回流爐、波峰焊機(jī)、清洗機(jī)自動(dòng)光學(xué)檢測(cè)設(shè)備等。

集成電路所有的關(guān)鍵參數(shù),所以花費(fèi)的時(shí)間較長(zhǎng),但對(duì)于保證產(chǎn)品質(zhì)量卻能起到關(guān)鍵作用。為加快集中檢測(cè)電學(xué)參數(shù)的速度,降低集成電路的測(cè)試成本, 半導(dǎo)體產(chǎn)業(yè)界開(kāi)發(fā)了相關(guān)的自動(dòng)測(cè)試設(shè)備(ATE)。利用計(jì)算機(jī)控制, ATE 能夠完成對(duì)集成電路的自動(dòng)測(cè)試。

ATE 價(jià)格昂貴,對(duì)測(cè)試環(huán)境要求苛刻,所以要求有高標(biāo)準(zhǔn)的測(cè)試場(chǎng)地,同時(shí)還要保證多臺(tái) ATE 并行運(yùn)行,以保證測(cè)試的速度和效率。對(duì)于每種集成電路都要開(kāi)發(fā)專(zhuān)門(mén)的ATE 測(cè)試程序,以保證測(cè)試自動(dòng)進(jìn)行。

近年來(lái),測(cè)試設(shè)備商經(jīng)過(guò)不斷整合,形成了以日本愛(ài)德萬(wàn)測(cè)試(ADVANTEST) 和美國(guó)泰瑞達(dá)(TERADYNE)兩大公司,其產(chǎn)品約占全球半導(dǎo)體企業(yè)測(cè)試設(shè)備市場(chǎng)份額的 80%以上。國(guó)內(nèi)測(cè)試設(shè)備廠(chǎng)商有長(zhǎng)川科技、華峰測(cè)控、廣立微等。

通過(guò)上文對(duì)全球設(shè)備龍頭的梳理,我們發(fā)現(xiàn):每大類(lèi)設(shè)備市場(chǎng)中,最終都形成了寡頭競(jìng)爭(zhēng)的格局,前三名廠(chǎng)商占據(jù)了絕大部分的市場(chǎng)份額,呈現(xiàn)強(qiáng)者恒強(qiáng)大者恒大的特點(diǎn)。