芯片設計老生常談,我國的芯片設計較其它發(fā)達國家而言,略顯劣勢。為增進全民對于芯片設計的了解,本文將對系統(tǒng)級芯片設計中的多領域集成策略予以講解。如果你對本文涉及的芯片設計內(nèi)容存在一定興趣,請繼續(xù)往下閱讀哦。

請注意,本文僅為上篇,如果你想了解更多系統(tǒng)級芯片設計多領域集成策略,請關注下篇文章哦。

大型多領域模擬混合信號(AMS)系統(tǒng)在電子行業(yè)中越來越常見,此類設計必須同時滿足進度和準確度要求,從而給設計工程師帶來了極大的挑戰(zhàn)。本文介紹了一種結合自上而下和自下而上的方法來實現(xiàn) “中間相遇”,可有效地克服這些挑戰(zhàn)。

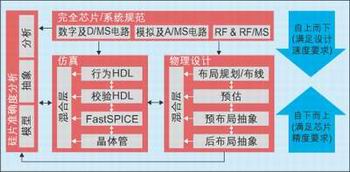

大型多領域AMS系統(tǒng)在電子行業(yè)中越來越常見,由于這些集成器件的設計中包括了RF器件、模擬器件、存儲器、定制化數(shù)字電路以及數(shù)字標準單元IP,全球工程師在設計AMS系統(tǒng)時也面臨著各種各樣的問題。要想成功地完成這些設計必須結合自上而下和自下而上的方法,最后實現(xiàn) “中間相遇”,并且需要采用多個領域的方法。Cadence的Virtuoso平臺用高級定制化設計(ACD)方法來開發(fā)適用于基于領域的設計流程藍圖并解決這些挑戰(zhàn)。

設計可預見性

可預見性是ACD方法的重要特性。可預測性主要包括兩方面:從設計開始便一直滿足進度要求從而盡快出帶(tap-out);滿足性能要求,實現(xiàn)一次性設計成功。

為滿足設計進度,要求設計過程必須足夠快,同時能支持徹底、全面的仿真和物理設計。設計過程包括多個任務,而且當前多數(shù)芯片都包含來自不同設計領域的多個模塊。因此,必須在設計中納入盡可能多的模塊,并盡可能地并行地執(zhí)行更多任務,并在設計過程中盡可能多地使用頂層IP。

在仿真和物理設計中均使用自上而下的設計方法可加快設計進程,它將從高級設計到具體的晶體管級設計的多個抽象層結合在一起,來支持一種混合層設計方案,完成測試前的所有細節(jié)設計。這種方法可利用頂層及相關信息進行模塊設計,隨后在頂層環(huán)境中對模塊進行再驗證。

另一方面,芯片必須具有足夠的準確度以實現(xiàn)設計性能要求。芯片的準確度與某些基本設計數(shù)據(jù)有關,如支持精確仿真的器件模型和支持互連、物理驗證和分析的技術文件。此外,這種方法還使用了靈敏度高、結構嚴謹?shù)臏y試芯片,以驗證設計工藝的可行性以及相應工藝設計套件(PDK)的準確度。為了支持某種特殊的設計風格,設計小組通常要在PDK中增加額外組件,同時還必須擴展器件模型,結合或增加臨界條件、統(tǒng)計建模或設計團隊所需的其它方法。

芯片準確度數(shù)據(jù)在整個設計過程和詳細的晶體管級的分析中都起著作用,包括版圖提取等詳細的晶體管層分析。這些構成了抽象鏈(abstracTIon chain)的較低層,反過來又支持將這些結果定標到更高抽象層。這就是高級定制化方法中的自下而上設計部分。

自上而下和自下而上的設計進程可以并行展開,產(chǎn)生“中間相遇”的設計方法。正是這種“中間相遇”法同時滿足了設計速度和芯片準確度要求,最后實現(xiàn)進度的可預測性并獲得一次性設計成功。

集成流程中的任何小毛病都會影響可預見性。通常在規(guī)劃進度時我們都假設集成過程中不會出現(xiàn)問題,但實際上如果我們不注意整體的設計方法,問題是必然會發(fā)生的,并且進而影響到進度,最終導致無法正確預估設計的進度或性能。

從整個設計項目來看,這些問題往往會使局面徹底失控。更糟糕的是,這種情況通常發(fā)生在出帶前的最后三周內(nèi)。設計流程中最難的一部分便是將芯片集成在一起進行驗證。由于多數(shù)設計都十分龐大,因此不允許出現(xiàn)一絲錯誤,由不同團隊獨立負責的模塊設計必須能迅速而準確地集成在一起。然而,這通常很難實現(xiàn)。更常見的情況是在即準備出帶前,工程師在數(shù)據(jù)庫上陷入永無止境的設計迭代循環(huán)中,進度被無限期地拖延。通常,芯片設計在未經(jīng)正確驗證便開始出帶,然后不可避免地造成返工,從而進一步推遲產(chǎn)品推出時間,也將影響贏利預期。

此外,如果設計中使用了前幾代設計中的IP,或從大型SoC設計中產(chǎn)生派生產(chǎn)品,情況將會更為復雜化。通常這樣做的原因可能是為了滿足額外的市場要求、使用了不同晶圓廠,或考慮到性能和成本的原因而換用了下一代工藝技術。在定制化設計領域中,“IP復用”一詞往往會引發(fā)爭議,因為IP移植/修改比純粹的數(shù)字設計涉及到更為全面設計。不過,這種設計其本身具有高度可用性,且對IP移植或修改工作來說也是一個十分有意義開始。這突顯了集成的問題:如果某個特殊模塊在首次設計中難于集成,它會給下一個派生產(chǎn)品和再次集成增加設計困難。因此,下次集成時除了會碰到首次集成的同樣問題外,這些增加的設計困難也會引發(fā)新的問題。因此,給這些支持未來在再利用和集成的設計選擇恰當?shù)脑O計過程十分關鍵。

以上便是此次小編帶來的“芯片設計”相關內(nèi)容,通過本文,希望大家對本文探討的內(nèi)容具備一定的了解。如果你喜歡本文,不妨持續(xù)關注我們網(wǎng)站哦,小編將于后期帶來更多精彩內(nèi)容。最后,十分感謝大家的閱讀,have a nice day!