毫不奇怪,每一種新的制造技術(shù)的出現(xiàn),都會讓晶圓變得越來越昂貴,因為節(jié)點往往需要更多的資金。臺積電最新的N5(5nm)制造工藝在每片晶圓上顯得特別昂貴,因為它是新晶圓,但其晶體管密度使其特別適合具有高晶體管數(shù)量的芯片。

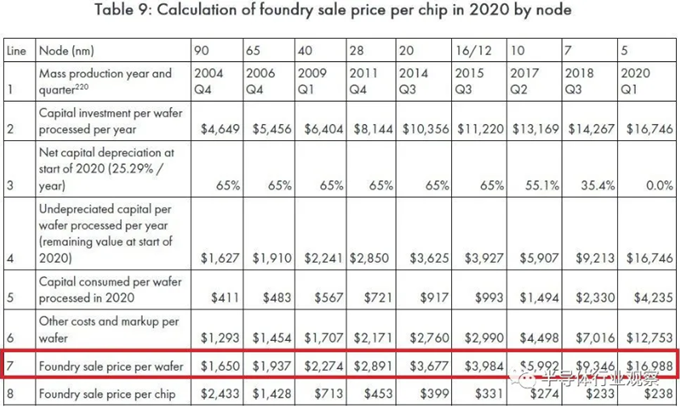

著名的半導(dǎo)體博客作者RetiredEngineer發(fā)布了一張表格,其中列出了臺積電在2020年每個節(jié)點的假想芯片銷售價格……

該模型基于假想的5nm芯片,該芯片大小為Nvidia P100 GPU(610 平方毫米,907億個晶體管,強度為148.2 MTr / mm2)。就每個圖案化的300毫米晶圓的晶圓代工銷售價格而言,該模型考慮了諸如CapEx,能耗,折舊,組裝,測試和封裝成本,晶圓代工營業(yè)利潤率以及其他一些因素。同時,每個芯片的代工廠銷售價格還包括設(shè)計成本,但是這個數(shù)字因公司而異,并且因節(jié)點而異(即,不同公司的610平方毫米的 5nm設(shè)計成本不同,并且610平方毫米芯片的實現(xiàn)方式也有所不同)由于設(shè)計規(guī)則和IP的不同,每個節(jié)點之間也是如此),因此應(yīng)謹(jǐn)慎對待。

據(jù)估計,臺積電使用N5技術(shù)處理的300mm晶圓售價約為16,988美元。相比之下,這家全球最大的半導(dǎo)體合同制造商對使用其N7節(jié)點圖案化的300mm晶圓的價格約為9,346美元,對于使用16nm或12nm技術(shù)制造的300mm晶圓的價格為3,984美元。

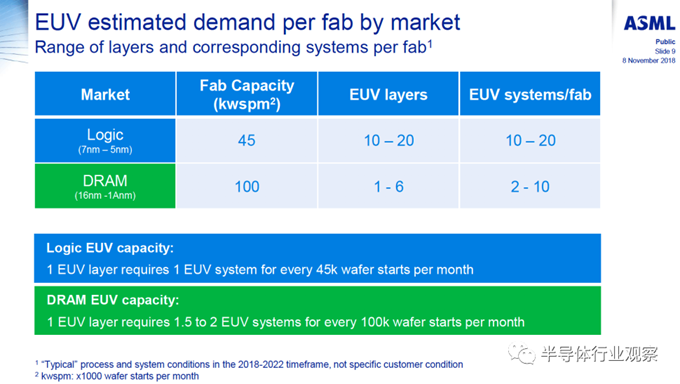

有許多因素使臺積電的N5節(jié)點如今使用起來如此昂貴。首先,臺積電在幾個月前開始生產(chǎn)5nm芯片,其晶圓廠及其使用的設(shè)備尚未貶值;其次,N5在很大程度上依賴于極紫外光刻技術(shù)的使用,并且最多可以在14層上使用。根據(jù)ASML的說法,每月每個大約45,000個晶圓的開始,一個EUV層就需要一個Twinscan NXE步進(jìn)掃描系統(tǒng)。據(jù)信,每個EUV光刻機的成本約為1.2億美元,而且這些掃描儀的運行成本也相當(dāng)高。鑒于臺積電的規(guī)模,其N5技術(shù)需要大量此類光刻機。因此,臺積電要折舊N5所用的晶圓廠和設(shè)備將花費一些時間。

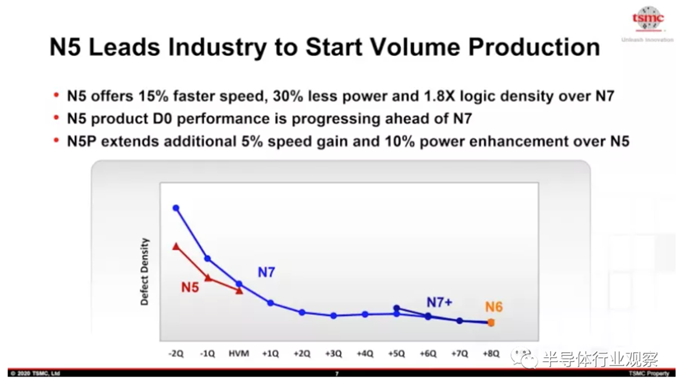

但是,即使按當(dāng)前成本計算,由于其高晶體管密度和性能,對于高度復(fù)雜的芯片制造商來說,使用臺積電的領(lǐng)先工藝也很有意義。根據(jù)提供的數(shù)字,使用N5制造610平方毫米芯片的成本為238美元,而使用N7生產(chǎn)相同芯片的成本為233美元。在16 / 12nm節(jié)點上,同一處理器將大得多,制造成本為331美元。與N7相比,在N5時,芯片不僅會相對較小(更精確地說為610平方毫米),而且在給定功率下運行速度也會快15%,在給定頻率下功耗也會減少30%。

臺積電(TSMC)表示,其N5的壽命同時具有比N7更低的缺陷密度,因此芯片設(shè)計人員可以預(yù)期,最終基于N5的芯片的產(chǎn)量通常會高于基于N7的IC。考慮到N5用EUV單圖案替代DUV多圖案的事實,后者是值得期待的。

在節(jié)點之間進(jìn)行這種比較時要記住的一件事是,盡管它是基于臺積電和整個半導(dǎo)體行業(yè)的數(shù)據(jù),但臺灣巨頭從未確認(rèn)過實際數(shù)字,因此它們可能不是100 %準(zhǔn)確。