日前,TechInsights高級技術(shù)研究員Joengdong Choe在2020年閃存峰會上作了兩次演講,詳細(xì)介紹了3D NAND和其他新興存儲器的未來。

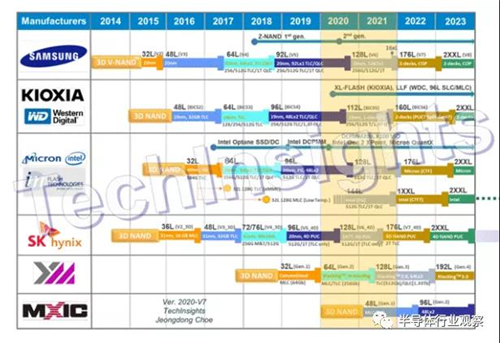

Choe在今年的演講中還披露了他們的2014-2023年路線圖,以及對閃存行業(yè)總體趨勢的一些討論。討論內(nèi)容涵蓋了所有主要制造商的TLC和QLC零件,包括三星,Kioxia(以前為東芝),英特爾,美光,SK hynix和YMTC。Choe涵蓋了這些設(shè)計的幾個方面,從層數(shù)到CMOS(外圍電路)放置以及其他可能影響位密度和成本的架構(gòu)因素。

TechInsights方面表示,字啊過去,公眾傾向于將注意力集中在3D閃存的層數(shù)上,這可能會產(chǎn)生誤導(dǎo),因為wordlines(帶有存儲單元的有源層)的實際數(shù)量會發(fā)生很大變化。例如,其他層可以用作偽字線,這有助于減輕由于層數(shù)過多而引起的問題。效率的一種衡量標(biāo)準(zhǔn)是分層字線的總數(shù)除以總層數(shù),通過這種衡量,三星擁有最好的設(shè)計之一。三星也沒有使用多個decks或stacks,并沒有像其他制造商當(dāng)前的閃存那樣看到“字符串堆棧”(string stacking)。

一種提高總體效率的方法是將CMOS或控制電路(通常稱為外圍電路)放置在閃存層下面。眾所周知,這有多個名稱,例如CMOS陣列下(CMOS-under-Array :CuA),單元下外圍(Periphery-Under-Cell :PUC)或外圍單元(Cell-On-Periphery :COP)。YMTC的設(shè)計有點例外,因為它在閃存頂部有一些電路,而CMOS是在綁定到閃存之前在更大的工藝節(jié)點中制成的。Choe說這種技術(shù)有潛力,但目前存在良率問題。

Choe還概述了3D NAND架構(gòu)的歷史以及電荷陷阱閃存(charge trap flash:CTF)和浮柵(Floating gate:FG)的分道揚鑣。在過去,英特爾和美光使用浮柵,直到美光在最近發(fā)布的176-D切換到替換門( replacement gate:RG),而其他制造商還是使用電荷陷阱。盡管英特爾的QLC受益于使用浮柵,因為它可以保持更好的磨損性能,但此處的差異可能會影響閃存的耐用性,可靠性,可擴展性以及其他方面。

Kioxia未來的split-gate或split-cell 技術(shù)也很有趣,它可以直接使閃存密度增加一倍,并且由于split-cell的半圓形形狀而具有增強的耐用性,這對于浮柵特別堅固。Choe預(yù)計,隨著平臺或堆棧數(shù)量的增加(目前最多為兩個),層數(shù)將繼續(xù)增加,每個閃存芯片的存儲量也會相應(yīng)增加。Choe認(rèn)為,這些技術(shù)與硅通孔(TSV),疊層封裝(PoP / PoPoP)以及向5LC / PLC的遷移等技術(shù)一樣,都指向下一個十年的500層以上和3 TB裸片的3D閃存。

Choe在第二次演講中詳細(xì)介紹了尖端閃存如何經(jīng)常首先進入移動和嵌入式產(chǎn)品領(lǐng)域,例如,電話(“ 5G”)是需求的主要推動力。他還指出,二維/平面閃存仍用于某些細(xì)分市場-通常像Optane或美光最近發(fā)布的X100一樣,將低延遲SLC用作3D XPoint的存儲級存儲器(SCM)替代品,盡管通常不再可見在消費市場。

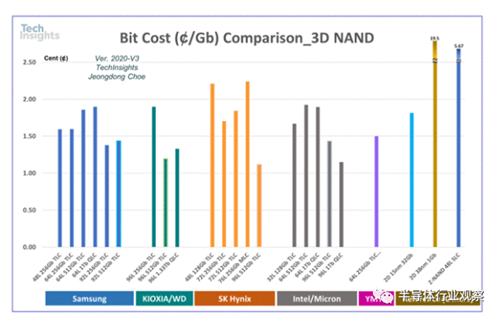

更重要的是,他詳細(xì)介紹了閃存成本,單位為美分/ GB,這展示了3D閃存價格趨于便宜的趨勢,而專用2D的價格仍然高出許多倍。無論如何,我們已經(jīng)出現(xiàn)了1xx層產(chǎn)品,例如已經(jīng)發(fā)布的SK hynix 128L Gold P31和Samsung 128L 980 PRO,美光最近發(fā)布的176L帶有閃存的產(chǎn)品,這些產(chǎn)品已經(jīng)出現(xiàn)在基于Phison E18的驅(qū)動器原型中。此外,來自WD / Kioxia的BiCS5預(yù)計將于明年與Intel的QLC產(chǎn)品一起提供144L。出色的控制器實施將能夠利用更高的閃存密度。

可以預(yù)見的是,在未來幾年內(nèi),將實現(xiàn)更快,容量更大的驅(qū)動器。