發(fā)展至今,NAND Flash已呈現(xiàn)白熱化階段。就在前不久,存儲(chǔ)廠商們還在128層“閃存高臺(tái)上觀景”,2019年6月SK海力士發(fā)布128層TLC 3D NAND;美光于2019年10月流片出樣128層3D NAND;長(zhǎng)江存儲(chǔ)于今年4月份宣布推出128層堆棧的3D NAND閃存。轉(zhuǎn)眼來(lái)到2020年末,美光和SK海力士相繼發(fā)布了176層3D NAND。這也是唯二進(jìn)入176層的存儲(chǔ)廠商。不得不說(shuō),存儲(chǔ)之戰(zhàn)沒(méi)有最烈,只有更烈。

2013年,三星推出的帶有850 pro SSD的垂直3D NAND閃存打響了3D NAND技術(shù)堆疊的第一槍?zhuān)鄬幼兊煤艹R?jiàn)。層數(shù)越高,NAND閃存可具有的容量就越大,因此,增加層數(shù)以及提高產(chǎn)量是衡量技術(shù)實(shí)力的標(biāo)準(zhǔn)。垂直堆疊迅速成為半導(dǎo)體行業(yè)的標(biāo)準(zhǔn),因?yàn)樗欣谧畲蟪潭鹊販p少彼此之間的干擾。此后,如美光和英特爾等廠商紛紛加入垂直堆疊的角逐中。如今,隨著使用微細(xì)加工工藝而增加的單元以及數(shù)據(jù)處理量的增長(zhǎng),對(duì)大容量NAND閃存的需求還在增加。

存儲(chǔ)廠商們各自努力,176層頂峰見(jiàn)真章

在全球NAND市場(chǎng)份額中,雖然美光排在第七位,但是在堆疊能力方面,美光卻毫不遜色。美光是第一家發(fā)布176層3D NAND的存儲(chǔ)廠商,其第五代3D NAND閃存是176層構(gòu)造,這也是自美光與英特爾的存儲(chǔ)器合作解散以來(lái)推出的第二代產(chǎn)品。2020年11月9日,美光宣布將批量發(fā)售世界上第一個(gè)176層3D NAND。

據(jù)美光官網(wǎng)介紹,該176層NAND采用了獨(dú)特的技術(shù),替換門(mén)架構(gòu)將電荷陷阱與CMOS陣列下(CuA)設(shè)計(jì)相結(jié)合,與同類(lèi)最佳競(jìng)爭(zhēng)產(chǎn)品相比,其die尺寸減小了約30%。

Micron-CuA技術(shù)

與美光的大容量浮柵96層NAND相比,其讀寫(xiě)時(shí)間縮短35%。與128層替換門(mén)NAND相比,美光公司176層NAND的讀取延遲和寫(xiě)入延遲均提高了25%以上。在開(kāi)放NAND閃存接口(ONFI)總線上,其最大數(shù)據(jù)傳輸速率為每秒1600兆傳輸(MT / s),據(jù)稱(chēng)是行業(yè)領(lǐng)先的。兩者共同意味著系統(tǒng)啟動(dòng)速度更快,存儲(chǔ)在NAND中的應(yīng)用程序啟動(dòng)速度更快。

美光的96L和128L NAND最高速度為1200 MT / s。與美光等效的96L產(chǎn)品相比,176L產(chǎn)品在移動(dòng)存儲(chǔ)中的混合工作負(fù)載性能提高了15%。據(jù)報(bào)道指出,在使用電荷陷阱單元設(shè)計(jì)替代柵極設(shè)計(jì)之后,美光似乎已大大降低了閃存每一層的厚度。數(shù)據(jù)顯示,176L裸片的厚度僅為45μm,總厚度與美光公司的64L浮柵3D NAND相同。

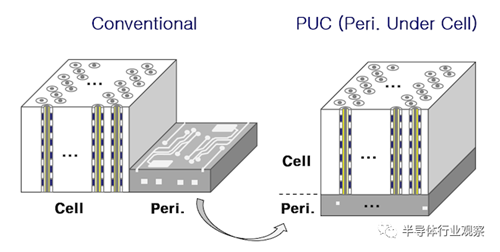

再就是SK海力士,據(jù)Anandtech報(bào)道,SK hynix日前發(fā)布了其最新一代的3D NAND。這是SK hynix的第三代產(chǎn)品,其PUC(Periphery under Cell)設(shè)計(jì)的特點(diǎn)是通過(guò)在存儲(chǔ)器單元陣列下放置外圍邏輯來(lái)減小芯片尺寸,類(lèi)似于英特爾和美光的CMOS下陣列設(shè)計(jì)。SK hynix將這種裸片布局及其charge trap閃存單元的組合稱(chēng)為“ 4D NAND”。SK hynix命名為“ 4D NAND Flash”,主要是以突出通過(guò)在2018年將來(lái)自96層NAND Flash的CTF單元結(jié)構(gòu)和PUC技術(shù)相結(jié)合而實(shí)現(xiàn)性能和生產(chǎn)率的差異。

這一代的變化包括位生產(chǎn)率提高了35%(僅比理論上從128層增長(zhǎng)到176層時(shí)的值稍低),單元讀取速度提高20%。NAND die和SSD控制器之間的最大IO速度已從128L NAND的1.2GT / s增加到176L NAND的1.6GT / s。

SK hynix計(jì)劃首先將其176層 NAND用于移動(dòng)產(chǎn)品(即UFS模塊),該產(chǎn)品將在明年中期左右推出,其讀取速度提高70%,寫(xiě)入速度提高35%。然后,消費(fèi)者和企業(yè)級(jí)固態(tài)硬盤(pán)將跟進(jìn)移動(dòng)產(chǎn)品。SK海力士還計(jì)劃基于其176層工藝推出1Tbit模具。

隨著六家制造商在全球范圍內(nèi)為贏利而激烈競(jìng)爭(zhēng),NAND閃存部門(mén)正在整合。今年10月20日,SK海力士和英特爾簽署了一項(xiàng)協(xié)議,根據(jù)該協(xié)議,SK海力士將以90億美元的價(jià)格收購(gòu)英特爾的NAND存儲(chǔ)器和存儲(chǔ)業(yè)務(wù)。該交易包括NAND SSD業(yè)務(wù),NAND組件和晶圓業(yè)務(wù)以及中國(guó)大連NAND存儲(chǔ)器制造廠。若交易達(dá)成,SK海力士將超越日本Kioxia,成為NAND內(nèi)存市場(chǎng)的全球第二大廠商,并進(jìn)一步縮小與行業(yè)領(lǐng)頭羊三星之間的差距。SK 海力士以90億美元收購(gòu)英特爾 NAND Flash 業(yè)務(wù),其核心是拿下作為3D NAND 存儲(chǔ)器生產(chǎn)重鎮(zhèn)的大連晶圓廠。

面對(duì)SK海力士和美光在3D閃存堆疊上的成就,其他閃存廠商也是在快馬加鞭加緊研發(fā)的步伐。

三星電子作為全球NAND領(lǐng)導(dǎo)者,占有33.8%的市場(chǎng)份額,如果三星想在很長(zhǎng)一段時(shí)間內(nèi)保持這一頭把交椅,就必須始終走在前面。畢竟,存儲(chǔ)芯片業(yè)務(wù)是該公司免于遭受COVID-19打擊的2020年第一季度遭受巨額利潤(rùn)下降的原因。根據(jù)韓國(guó)出版物The Bell的最新報(bào)告,該公司已經(jīng)在下一代閃存芯片的開(kāi)發(fā)方面取得了重大進(jìn)展。

全球NAND Flash市場(chǎng)份額

三星電子計(jì)劃在2021年上半年大規(guī)模生產(chǎn)具有170層或更多層的第七代V-NAND閃存,并將使用字符串堆疊方法,結(jié)合兩個(gè)88L模具,新芯片還將采用“雙棧”技術(shù)。行業(yè)觀察家表示,由于三星電子改變了其堆疊方法,該產(chǎn)品的發(fā)布已被推遲。今年6月初,三星宣布將在其位于韓國(guó)京畿道平澤工廠2號(hào)線的工廠中建設(shè)新的NAND閃存芯片生產(chǎn)設(shè)施。三星表示,將在新地點(diǎn)大規(guī)模生產(chǎn)其“尖端V-NAND存儲(chǔ)器”芯片。

三星之后,就是鎧俠(Kioxia),東芝存儲(chǔ)器是從去年2019年10月1日起正式改名為“KIOXIA鎧俠”,值得一提的是,NAND閃存由東芝于1987年首次提出的。今年10月,鎧俠表示,該公司將在日本中部三重縣的四日市工廠內(nèi)建立一個(gè)新的1萬(wàn)億日元(95億美元)工廠,以提高其尖端NAND閃存的產(chǎn)量,因?yàn)樵摴镜哪繕?biāo)是滿(mǎn)足5G增長(zhǎng)推動(dòng)的不斷增長(zhǎng)的需求網(wǎng)絡(luò)。這項(xiàng)投資將與美國(guó)合作伙伴Western Digital進(jìn)行。該工廠將從明年春季開(kāi)始分兩個(gè)階段進(jìn)行建設(shè)。這家占地40,000平方米的工廠將是Kioxia最大的工廠。

在2020年英特爾架構(gòu)日期間,英特爾談到了他們的3D NAND技術(shù)。早在2019年9月于韓國(guó)首爾舉行的英特爾存儲(chǔ)日上,英特爾宣布他們將跳過(guò)業(yè)界大多數(shù)人正在開(kāi)發(fā)的128層NAND閃存節(jié)點(diǎn),并將直接跳到144層。英特爾表示,他們的144層QLC NAND閃存仍在按計(jì)劃進(jìn)行。英特爾希望到2020年底,將其144層QLC NAND閃存用于銷(xiāo)售產(chǎn)品!144層QLC NAND的比特密度基本上比Intel目前生產(chǎn)的96層QLC NAND閃存高50%。因此,當(dāng)144層QLC NAND閃存進(jìn)入市場(chǎng)時(shí),應(yīng)允許SSD繼續(xù)侵蝕消費(fèi)者的旋轉(zhuǎn)硬盤(pán)市場(chǎng)。

英特爾3D NAND路線圖2020

而西部數(shù)據(jù)于今年1月份宣布,它已經(jīng)成功開(kāi)發(fā)了其第五代3D NAND技術(shù)BiCS5,BiCS5設(shè)計(jì)使用112層,而B(niǎo)iCS4使用96層。BiCS5技術(shù)是與技術(shù)和制造合作伙伴鎧俠共同開(kāi)發(fā)的。他們的第五代BiCS 3D NAND已以512 Gbit TLC部件的形式開(kāi)始生產(chǎn),但要到今年下半年才能增加到“有意義的商業(yè)量”。計(jì)劃用于這一代的其他部件包括1Tbit TLC和1.33 Tbit QLC die。

BiCS5采用了廣泛的新技術(shù)和制造創(chuàng)新技術(shù),是西部數(shù)據(jù)迄今為止最高密度和最先進(jìn)的3D NAND技術(shù)。第二代多層存儲(chǔ)孔技術(shù),改進(jìn)的工程工藝和其他3D NAND單元增強(qiáng)功能顯著提高了整個(gè)晶片上水平的單元陣列密度。這些“橫向擴(kuò)展”的進(jìn)步與112層垂直存儲(chǔ)功能相結(jié)合,使BiCS5與Western Digital的96層BiCS4技術(shù)相比,每個(gè)晶片的存儲(chǔ)容量提高了40%以上,同時(shí)優(yōu)化了成本。新的設(shè)計(jì)增強(qiáng)功能還提高了性能,使BiCS5的I / O性能比BiCS4快50%。

國(guó)內(nèi)長(zhǎng)江存儲(chǔ)進(jìn)步非凡

此前,長(zhǎng)江存儲(chǔ)科技有限責(zé)任公司CEO楊士寧在“2020北京微電子國(guó)際研討會(huì)暨IC World學(xué)術(shù)會(huì)議”上也談到,集成電路由二維向三維發(fā)展是必行趨勢(shì)。這可能不是一條唯一的路徑,但確是一條需要強(qiáng)烈探索的路徑。

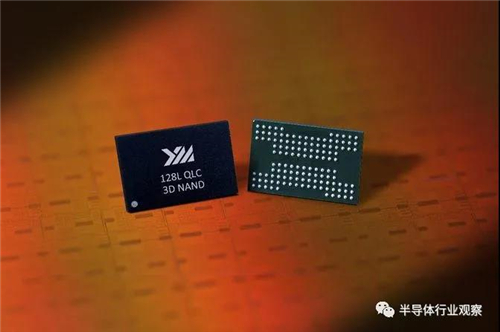

平地一聲雷,今年4月份長(zhǎng)江存儲(chǔ)宣布推出128層堆棧的3D NAND閃存,國(guó)外同行發(fā)現(xiàn),長(zhǎng)江存儲(chǔ)跳級(jí)了,因?yàn)?D NAND是從32層、64層、96層逐漸移到128層,但是長(zhǎng)江存儲(chǔ)并未推出過(guò)96層堆棧,這是怎么一回事呢?

長(zhǎng)江存儲(chǔ)X2-6070 128L QLC 1.33Tb 3D NAND,來(lái)源:長(zhǎng)江存儲(chǔ)

這就要追溯下長(zhǎng)江存儲(chǔ)的歷史淵源,長(zhǎng)江存儲(chǔ)前身是武漢新芯,2016年7月,紫光聯(lián)合大基金共同出資,在武漢新芯的基礎(chǔ)上,創(chuàng)立長(zhǎng)江存儲(chǔ),長(zhǎng)江存儲(chǔ)將精力放在與中科院微電子所的合作研究上。2017年年底,長(zhǎng)江存儲(chǔ)正式推出了國(guó)產(chǎn)首個(gè)真正意義上的32層 3D NAND閃存,中國(guó)終于有了自主知識(shí)產(chǎn)權(quán)的閃存芯片。

而國(guó)際閃存市場(chǎng)競(jìng)爭(zhēng)激烈,此時(shí)長(zhǎng)江存儲(chǔ)開(kāi)始探索一條適合自己的3D NAND技術(shù),這是一條充滿(mǎn)未知的道路,長(zhǎng)江存儲(chǔ)堅(jiān)持創(chuàng)新發(fā)展,走差異化的路線,于2018年7月正式推出自家的獨(dú)門(mén)絕技Xtacking?架構(gòu)。

傳統(tǒng)3D NAND架構(gòu)中,外圍電路約占芯片面積的20~30%,降低了芯片的存儲(chǔ)密度。隨著3D NAND技術(shù)堆疊到128層甚至更高,外圍電路可能會(huì)占到芯片整體面積的50%以上。Xtacking?技術(shù)將外圍電路置于存儲(chǔ)單元之上,從而實(shí)現(xiàn)比傳統(tǒng)3D NAND更高的存儲(chǔ)密度。

采用Xtacking?,可在一片晶圓上獨(dú)立加工負(fù)責(zé)數(shù)據(jù)I/O及記憶單元操作的外圍電路。這樣的加工方式有利于選擇合適的先進(jìn)邏輯工藝,以讓NAND獲取更高的I/O接口速度及更多的操作功能。存儲(chǔ)單元同樣也將在另一片晶圓上被獨(dú)立加工。當(dāng)兩片晶圓各自完工后,創(chuàng)新的Xtacking?技術(shù)只需一個(gè)處理步驟就可通過(guò)數(shù)十億根金屬VIA(Vertical Interconnect Accesses,垂直互聯(lián)通道)將二者鍵合接通電路,而且只增加了有限的成本。

長(zhǎng)江存儲(chǔ)始終與國(guó)際水平差一代的距離,如果還跟著別人后面跑,任何市場(chǎng)上實(shí)現(xiàn)不了商業(yè)化就只有死路一條,所以長(zhǎng)江存儲(chǔ)做出了一個(gè)瘋狂的舉措:決定直接跳過(guò)96層堆棧閃存的研發(fā),直接向128層的堆棧上探索。2020年4月,長(zhǎng)江存儲(chǔ)搶先推出了128層QLC 3D NAND閃存芯片X2-6070。目前長(zhǎng)江存儲(chǔ)的技術(shù)已經(jīng)處于全球一流的水準(zhǔn),下一步就是解決產(chǎn)能的問(wèn)題。

楊士寧介紹,Xtacking主要具有四方面優(yōu)勢(shì):一是速度快,具有更好的性能表現(xiàn);二是工藝更結(jié)實(shí);三是成本低,因?yàn)槊芏雀撸凰氖蔷哂懈叩撵`活性。與國(guó)際存儲(chǔ)大廠相比,長(zhǎng)江存儲(chǔ)表示,公司用短短3年時(shí)間實(shí)現(xiàn)了從32層到64層再到128層的跨越。長(zhǎng)江存儲(chǔ)3年完成了他們6年走過(guò)的路,楊士寧直言,長(zhǎng)江存儲(chǔ)不做最后一名,爭(zhēng)取公司的下一代產(chǎn)品能夠達(dá)到行業(yè)最前沿。

3D NAND 技術(shù)堆疊將走向何方?

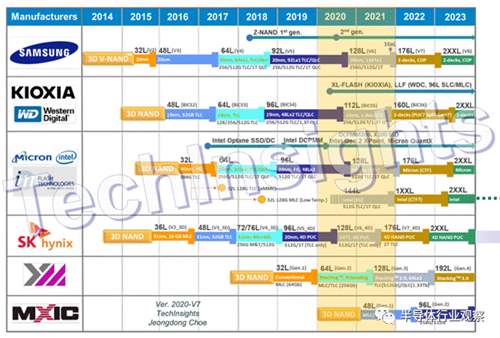

3D NAND技術(shù)正在迅速發(fā)展,許多分析師認(rèn)為,廠商將繼續(xù)在3D NAND閃存中添加層,直到不再可行為止。2015年還只有32層存儲(chǔ)單元,僅僅四五年之后,我們看到了96層、128層、112層、144層、176層等結(jié)構(gòu)的發(fā)布。到2022年,256層結(jié)構(gòu)成為可能。

圖源:techinsights

Forward Insights總裁兼首席分析師Gregory Wong表示,NAND閃存的未來(lái)不可避免地圍繞著每個(gè)單元的位數(shù)。Wong說(shuō),在過(guò)去的一年中,QLC NAND的使用主要集中在PC上,但是這種情況將會(huì)改變。“今年,我們期望看到用于超大規(guī)模數(shù)據(jù)中心的QLC驅(qū)動(dòng)器及其在企業(yè)存儲(chǔ)系統(tǒng)中的引入。” 事實(shí)也正是如此,越來(lái)越多的供應(yīng)商開(kāi)始談?wù)換LC設(shè)備的生產(chǎn)或生產(chǎn)。

但是,Wong說(shuō),擴(kuò)展位密度和降低閃存設(shè)備的成本變得越來(lái)越困難。“盡管如此,NAND閃存將存在很長(zhǎng)一段時(shí)間,因?yàn)槟壳斑€沒(méi)有一種技術(shù)可以在比特密度和成本上競(jìng)爭(zhēng)。

TechInsights,Inc.高級(jí)技術(shù)研究員Joengdong Choe在2020年閃存峰會(huì)上作了兩次演講,詳細(xì)介紹了3D NAND和其他新興存儲(chǔ)器的未來(lái)。

他講到,公眾傾向于將注意力集中在層數(shù)上,這可能會(huì)產(chǎn)生誤導(dǎo),因?yàn)樽志€(帶有存儲(chǔ)單元的有源層)的實(shí)際數(shù)量會(huì)發(fā)生很大變化。例如,可以將其他層用作偽字線,以幫助緩解由較高層數(shù)引起的問(wèn)題。效率的一項(xiàng)衡量標(biāo)準(zhǔn)是分層字線的總數(shù)除以總層數(shù),通過(guò)這種衡量,三星擁有最佳設(shè)計(jì)之一。三星也沒(méi)有使用多個(gè)卡座或堆棧-不像其他制造商當(dāng)前的閃存那樣使用”字符串堆棧“。一種提高總體效率的方法是將CMOS或控制電路(通常稱(chēng)為外圍電路)放置在閃存層下面,例如CMOS陣列下(CuA),單元下外圍(PUC)或外圍單元(COP)。

Choe還概述了3D NAND架構(gòu)的歷史以及電荷陷阱閃存(charge trap flash:CTF)和浮柵(Floating gate:FG)的分道揚(yáng)鑣的過(guò)程。在過(guò)去,英特爾和美光使用浮柵,但美光在最近發(fā)布的176-D切換到替換門(mén)( replacement gate:RG),而其他制造商還是使用電荷陷阱。盡管英特爾的QLC受益于使用浮柵,因?yàn)樗梢员3指玫哪p性能,但此處的差異可能會(huì)影響閃存的耐用性,可靠性,可擴(kuò)展性以及其他方面。

Choe預(yù)計(jì),隨著平臺(tái)或堆棧數(shù)量的增加(目前最多為兩個(gè)),層數(shù)將繼續(xù)增加,每個(gè)閃存芯片的存儲(chǔ)量也會(huì)相應(yīng)增加。Choe認(rèn)為,這些技術(shù)與硅通孔(TSV),疊層封裝(PoP / PoPoP)以及向5LC / PLC的遷移等技術(shù)一樣,都指向下一個(gè)十年的500層以上和3 TB裸片的3D閃存。

結(jié)語(yǔ)

就像摩爾定律走到現(xiàn)在,技術(shù)難度和成本要求越來(lái)越苛刻,隨著3D NAND高樓越蓋越高,以后也是非同一般的高難度技術(shù),即便如此,也要硬著頭干下去,直到干不動(dòng)為止!可以預(yù)見(jiàn),未來(lái),NAND閃存制造商之間的競(jìng)爭(zhēng)將會(huì)愈演愈烈。