前言:

半導體行業(yè)正在經歷一個技術進步和創(chuàng)新浪潮的復興時期,。EDA工具至此也進入2.0時代,。

作者 | 方文

芯片制作必需品

一顆芯片從設計到制造成成品,少不了各種設備的輔助,。大眾熟知的光刻機,、刻蝕機等機器,,都屬于硬件設備,它們在芯片行業(yè)的地位極高,。除了硬件設備,,很少被人們提及的軟件工具也十分重要。

目前EDA需要變得更加AI化,,它能幫助客戶設計達到最優(yōu)化的PPA目標(性能、功耗,、面積),,開發(fā)性能更高的終端產品,并進一步減少設計迭代,,縮短設計周期,,加快上市速度。最終,,具備AI特性的EDA工具將助力客戶設計出更好的芯片,,并快速推向市場。

EDA處于芯片產業(yè)鏈的最上游,,是芯片設計和生產的必備工具,。利用EDA工具,芯片的電路設計,、性能分析,、設計IC版圖的整個過程都可以由計算機自動處理完成,提高了工作效率及芯片精度,。

離開專業(yè)的EDA工具,,集成電路及半導體的設計和制造,都是不可想象的事情,。雖然EDA十分重要,但是EDA的市場規(guī)模很小,,目前全球總量為70億美元左右,,只占整個集成電路市場的九牛一毛,。

EDA市場中的新思科技

如今的EDA市場,,是標準的寡頭市場,。三家公司共同瓜分了全球92%的份額,,新思科技(Synopsys)就是其中之一。

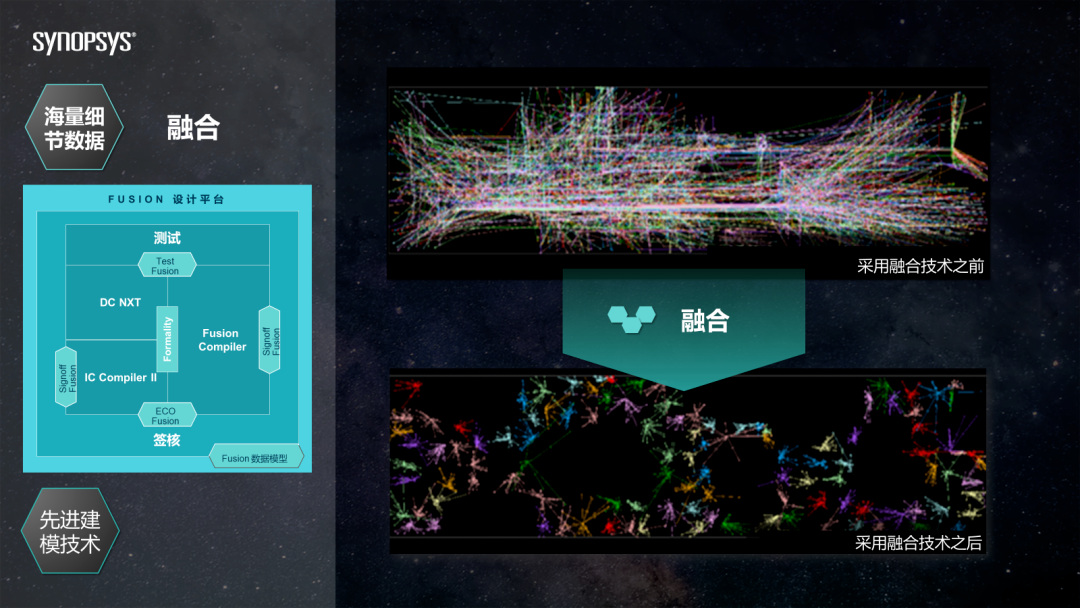

新思科技強調數(shù)字芯片設計技術的融合,,通過融合同類最佳的優(yōu)化功能以及行業(yè)經典signoff工具改善了RTL到GDSII設計流程,幫助開發(fā)者以業(yè)界最佳的全流程質量和最短的獲得結果時間加速交付其下一代設計,。

融合技術重新定義了EDA工具進入2.0時代,它在綜合,、布局布線以及signoff這些業(yè)界首要的數(shù)字設計工具間共享引擎,,并使用了獨特的數(shù)據(jù)模型表達邏輯及物理信息,。

此外,,在數(shù)字芯片設計過程中,,新思科技亦提供ECO 、Signoff,、Test等融合技術,,使得RTL到GDSII的設計實現(xiàn)流程具有最高的可預見性,同時能夠以最少的設計迭代次數(shù)得到卓越的設計時序,、功耗和面積結果。

該技術基于共用的大規(guī)模并行及機器學習就緒的基礎架構,,使設計規(guī)則和設計意圖在整個流程中有著一致的解讀。

新思科技下一代EDA設計

數(shù)字設計邁進新紀元,,融合技術也可以應用到EDA工具本身,。每款工具從前到后需要經過多道工序,且每一個算法不是都往同一個方向去優(yōu)化,,比如有些算法是為了讓芯片跑得更快,,有些算法是讓芯片變得更小,有些算法讓芯片功耗更低,。

如果沒有早期采用融合技術,,后期的不確定性會變大。因此新思科技推出創(chuàng)新性的RTL-to-GDSII產品Fusion Compiler,,來解決先進工藝節(jié)點設計的復雜性,。

Fusion Compiler通過把新型高容量綜合技術與布局布線技術相結合,以更好地預測結果質量,,來應對行業(yè)最先進設計所帶來的挑戰(zhàn),;并能夠在RTL-to-GDSII流程中共享技術,從而形成一套高度收斂的系統(tǒng),,將QoR提升20%,,TTR縮短2倍,。

同時Fusion Compiler提供的RTL-to-GDSII的單座艙(single-cockpit)解決方案,可實現(xiàn)高效率,、靈活性和吞吐量,,并可最大限度地提高性能,、功耗和面積(PPA),。

新思科技發(fā)展趨勢

①要整合各種先進工藝,新思的DTCO設計方法學將是半導體產業(yè)數(shù)字化的重要里程碑,,從創(chuàng)造工藝的開始就考慮到設計者的需求,打通設計到制造工藝的數(shù)據(jù)鏈條,。目前DTCO已經幫助客戶實現(xiàn)2nm工藝設計,。

此外,,新思還能夠通過3DIC Compiler將異質芯片整合在同一微系統(tǒng),,統(tǒng)一數(shù)據(jù)結構。

②使用AI做為生產工具提升數(shù)據(jù)價值和效能,,提升EDA的性能,協(xié)助開發(fā)者創(chuàng)造出更好的芯片,,如DSO.ai是業(yè)界首款AI自主芯片設計解決方案,。

③以數(shù)據(jù)提升客戶捕捉終端應用需求的能力,。新一代EDA還能夠為客戶提供數(shù)據(jù)化模型,,了解需求,,讓軟件開發(fā)更容易,,并通過收集,、整合,、分析半導體產業(yè)鏈上的離散數(shù)據(jù),,讓客戶體驗數(shù)據(jù)化,。

④以新一代EDA的理念構建新的產業(yè)生態(tài),促進產業(yè)鏈垂直合作,,實現(xiàn)數(shù)據(jù)共享,、產業(yè)互聯(lián),讓中國更早實現(xiàn)產業(yè)互聯(lián)網(wǎng),,賦能未來數(shù)字社會,。

新思科技中國董事長兼全球資深副總裁葛群認為,下一代EDA不僅僅是解決制造問題,,還要支持產業(yè)互聯(lián)網(wǎng),。未來EDA需要和AI與云計算協(xié)作,來更有效的處理任務,;還需要整合各種先進工藝,,統(tǒng)一數(shù)據(jù)結構。

新思還在更高層面上思考如何讓開發(fā)者更好地通過數(shù)據(jù)了解終端應用需求,、帶來更好體驗,,實現(xiàn)需求、應用,、體驗的數(shù)字化以及拓展產業(yè)生態(tài)鏈,。

EDA進入2.0時代

云計算+EDA:云技術的應用主要有三大優(yōu)點:快速部署可提高工程效率并加速項目完成;通過靈活的解決方案和大規(guī)??蓴U展的云就緒工具實現(xiàn)無痛采用,;經過驗證的解決方案具有很好的安全性,被許多客戶信賴和使用,。

人工智能+EDA:芯片敏捷設計是未來發(fā)展的一個主要方向,,深度學習等算法能夠提高EDA軟件的自主程度,,提高IC設計效率,,縮短芯片研發(fā)周期,。機器學習在EDA的應用可專門為芯片設計工程師提供仿真和驗證工具的EDA細分行業(yè)是整個半導體行業(yè)生態(tài)鏈中最上游,,最高端的節(jié)點,。

因此,,把AI引入EDA工具來支持大規(guī)模并行運算,,實現(xiàn)云端部署EDA,,將是未來的趨勢,。

結尾:

半導體行業(yè)持續(xù)驅動著工藝沿摩爾定律發(fā)展,為EDA帶來了日益增長的技術挑戰(zhàn)。未來的芯片挑戰(zhàn)來自于工藝,、豐富的應用場景,、整體設計規(guī)模以及成本,。

為了應對這些挑戰(zhàn),,除了要把工具做得更好外,,還需要積極探索EDA工具與AI和云技術的融合,,讓芯片開發(fā)者可以把研發(fā)的重點轉移到如何創(chuàng)造出更有意義的芯片。