如今幾乎所有數(shù)字元件背后的邏輯電路都依賴于兩種成對(duì)的晶體管– NMOS 和PMOS,。相同的電壓信號(hào)會(huì)將其中一個(gè)晶體管打開,而將另一個(gè)關(guān)閉,。將它們放在一起意味著只有發(fā)生些微變化時(shí)電流才會(huì)流通,,進(jìn)而大大降低了功耗。這些成對(duì)的晶體管已經(jīng)彼此櫛次鱗比在一起好幾十年,,但是如果電路要繼續(xù)縮小,,它們就必須靠得更近。

英特爾(Intel)在本周的IEEE 國際電子元件大會(huì)(IEEE International Electron Devices Meeting, IEDM)上展示全然不同的排列方式:把一對(duì)晶體管堆疊在另一對(duì)上面,。該方案有效地將一個(gè)簡單的CMOS 電路所占面積減半,,這意味著未來IC 集成電路芯片上的晶體管密度可能會(huì)增加一倍。

該方案首先使用了被廣泛認(rèn)可的下一代晶體管結(jié)構(gòu),,該結(jié)構(gòu)有不同的稱呼,包括納米片(Nanosheet),、納米帶(Nanoribbon),、納米線(Nanowire)或環(huán)繞式結(jié)構(gòu)(Gate- All-Around, GAA)元件。和當(dāng)前晶體管主要部分是由垂直硅鰭片組成之常見做法不同的是,,英特爾納米片的通道區(qū)是由多個(gè)相互堆疊之水平納米級(jí)薄片組成,。

采用自我對(duì)準(zhǔn)制程配方,,修改制造步驟成為制程重點(diǎn)

英特爾工程師使用這些元件來打造極簡的CMOS 邏輯電路,亦即所謂反向器(Inverter),。它需要兩個(gè)晶體管,,兩個(gè)電源接線,一個(gè)輸入連線和一個(gè)輸出連線,。即使晶體管也采取像當(dāng)前并排的放置方式,,但排列得非常緊湊。透過堆疊晶體管并調(diào)整互連,,反向器面積得以減半,。

英特爾用于打造堆疊式納米片的配方被稱為「自我對(duì)準(zhǔn)」(Self-Aligned)制程,因?yàn)槠鋵?shí)質(zhì)上可透過相同的步驟中構(gòu)建兩種元件,。這很重要,,因?yàn)槎嗉拥诙襟E(比如,在個(gè)別的晶圓上構(gòu)建他們,,然后再將晶圓接合在一起)可能會(huì)導(dǎo)致晶圓定位偏移,,進(jìn)而造成任何潛在電路的破壞。

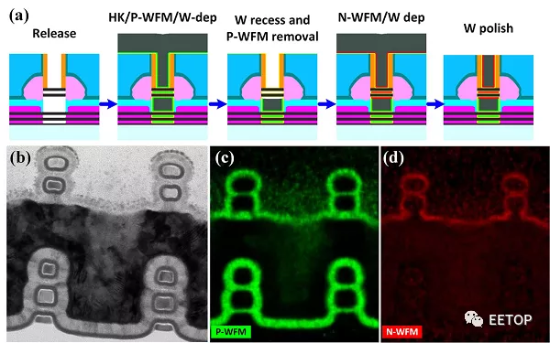

該制程的核心重點(diǎn)是對(duì)納米片晶體管的制造步驟進(jìn)行修改,。它首先從重復(fù)的硅層和硅鍺層開始,。然后將其蝕刻成一個(gè)又高又窄的鰭片,然后再將硅鍺蝕刻掉,,留下一組懸浮的硅納米片,。通常,所有的納米片都會(huì)形成單一的晶體管,。但在此,,最上面兩個(gè)納米片會(huì)連接到摻磷硅(Phosphorous-Doped Silicon)上,其目的為了形成一個(gè)NMOS 元件,,而底部兩個(gè)納米片則連接到了摻硼硅鍺(boron- doped silicon germanium)上,,以產(chǎn)生PMOS。

簡化整合流程,,將應(yīng)變引進(jìn)自家元件中

這整個(gè)「整合流程」當(dāng)然要復(fù)雜得多,,但是英特爾研究人員一直在努力使其盡可能地簡單,英特爾資深研究員暨元件研究總監(jiān)Robert Chau 表示,?!刚狭鞒滩荒芴^復(fù)雜,因?yàn)檫@將影響到以堆疊式CMOS 制造芯片的可行性,。結(jié)果證明這是一個(gè)非常實(shí)用的流程,,并取得了可觀的成果?!?/p>

他表示:「一旦掌握了這個(gè)訣竅,,下一步就可以開始追求效能表現(xiàn)了,。」這可能包括PMOS 元件的改進(jìn)作業(yè),,目前它們?cè)隍?qū)動(dòng)電流方面落后NMOS,。Chau 進(jìn)一步指出,該問題的答案可能是要在晶體管通道中引進(jìn)「應(yīng)變」(Strain),。此一構(gòu)想是透過快速通過載流子(Charge Carrier,,在這種情況下為電洞)的這種方式來扭曲硅晶體晶格。英特爾早在2002年就將應(yīng)變引進(jìn)至自家元件中,。在IEDM 大會(huì)的另一項(xiàng)研究中,,英特爾展示了一種能在納米帶晶體管中同時(shí)產(chǎn)生壓縮應(yīng)變(Compressive Strain)和拉伸應(yīng)變(Tensile Strain)的方法。

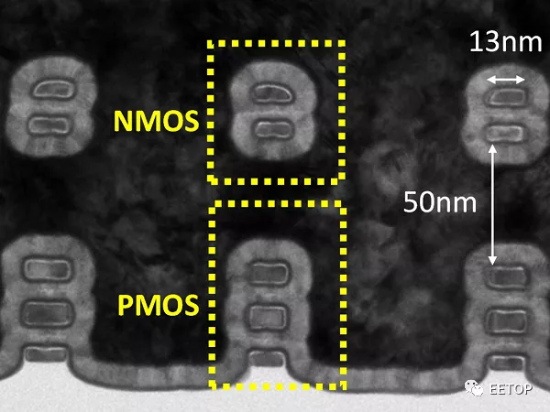

其他研究組織也正展開堆疊式納米片的設(shè)計(jì)研究,,盡管有時(shí)將它們稱為互補(bǔ)式場效晶體管(Complementary FET, CFET),。比利時(shí)研究組織Imec 率先提出了CFET 概念,并于去年6 月的IEEE超大型集成電路技術(shù)研討會(huì)(VLSI Symposia)上發(fā)表了實(shí)作CFET 的研究報(bào)告,。但是,,Imec 元件并非完全由納米片晶體管制作而成。其底層反而是由鰭式場效晶體管(FinFET)組成,,頂層則為單一納米片,。中國臺(tái)灣研究人員曾發(fā)表一篇有關(guān)CFET實(shí)作的研究報(bào)告,該結(jié)構(gòu)上的PMOS 和NMOS 各有一片納米片,。相比之下,,英特爾的電路在3 納米之納米片PMOS 上面有一個(gè)2 納米之納米片NMOS,這更接近當(dāng)堆疊有必要時(shí)元件該有的樣子,。