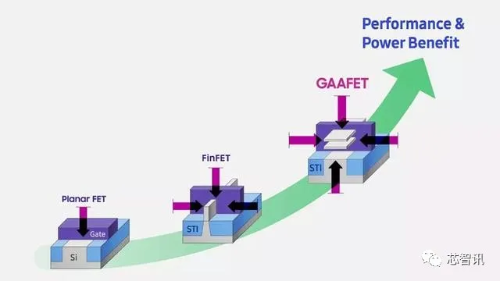

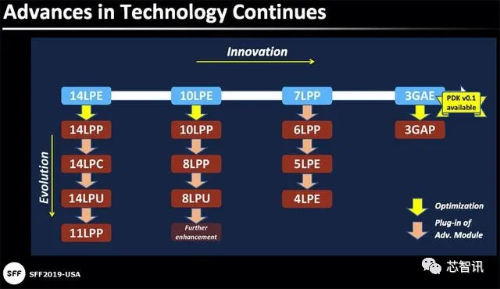

三星在去年年初就宣布他們攻克了3nm工藝的關(guān)鍵技術(shù)GAAFET全環(huán)繞柵極晶體管工藝,,預(yù)計(jì)會(huì)在2022年正式推出這種工藝,目前關(guān)于此工藝的消息甚少,。不過(guò),,近日外媒tomshardware報(bào)道稱(chēng)三星在近日的IEEE國(guó)際集成電路會(huì)議上,首次公布了采用3nm工藝制造的SRAM存儲(chǔ)芯片,,并透露了3GAE工藝的一些細(xì)節(jié),。

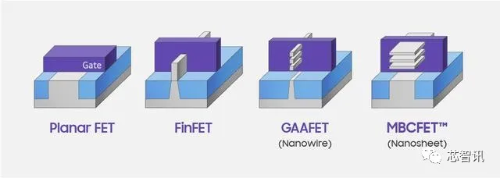

GAAFET其實(shí)有兩種,一種是使用納米線作為電子晶體管鰭片的常見(jiàn)GAAFET,,另外一種則是以納米片形式出現(xiàn)的較厚鰭片的多橋通道場(chǎng)效應(yīng)電子晶體管MBCFET,。兩種都在柵極材料所在側(cè)面上圍繞溝道區(qū),納米線與納米片的實(shí)現(xiàn)方式很大程度上取決于設(shè)計(jì),,一般而言都用GAAFET來(lái)描述兩者,。

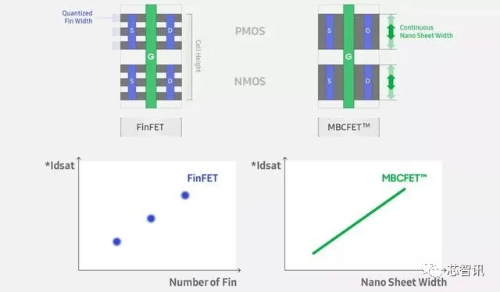

GAAFET其實(shí)早在1988年就出現(xiàn)了,這種晶體管的結(jié)構(gòu)使得設(shè)計(jì)人員可以通過(guò)調(diào)節(jié)晶體管通道的寬度來(lái)精確地對(duì)其進(jìn)行調(diào)諧,,以實(shí)現(xiàn)高性能或低功耗,。較寬的薄片可以在更高的功率下實(shí)現(xiàn)更高的性能,而較薄/較窄的薄片可以降低功耗和性能,。在FinFET上實(shí)現(xiàn)類(lèi)似的設(shè)計(jì)時(shí),,工程師必須使用額外的鰭來(lái)改善性能。但是在這種情況下,,晶體管通道的“寬度”只能增加一倍或兩倍,,精度不是很好,有時(shí)效率很低,。

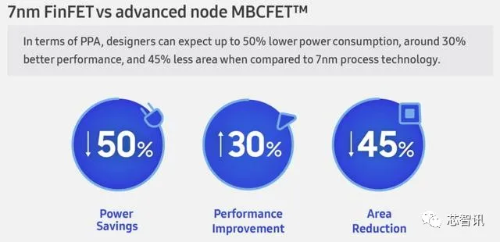

三星表示,,與7LPP工藝相比,3GAE工藝可在同樣功耗下讓性能提高30%,,同樣頻率下能讓功耗降低50%,,晶體管密度最高可提高80%。

三星展示了首個(gè)使用MBCFET技術(shù)的SRAM芯片,,這個(gè)256Gb芯片的面積是56mm?,,與現(xiàn)有芯片相比這個(gè)用MBCFET技術(shù)的寫(xiě)入電壓降低了230mV,可見(jiàn)MBCFET確實(shí)能讓降低功耗,。

SRAM其實(shí)是比較簡(jiǎn)單的芯片,,目前還沒(méi)有見(jiàn)到三星能用這種技術(shù)生產(chǎn)復(fù)制芯片的能力,但相信給些時(shí)間三星就能解決這問(wèn)題,,預(yù)計(jì)3nm MBCFET制程會(huì)在2022年投產(chǎn),。