引言:生態(tài)是使小芯片(Chiplet)技術(shù)得到采用并獲得長期成功的必要部分,而生態(tài)是圍繞標(biāo)準(zhǔn)建立的。這些標(biāo)準(zhǔn)正在慢慢被構(gòu)建起來。

目前對(duì)小芯片的需求還在增加,但對(duì)大多數(shù)公司來說,這種轉(zhuǎn)變是緩慢進(jìn)行的,直到可驗(yàn)證的標(biāo)準(zhǔn)被行業(yè)接受。

互操作性和兼容性依賴于供應(yīng)鏈的諸多層級(jí)達(dá)成的一致。不幸的是,分散的行業(yè)需求可能會(huì)導(dǎo)致冗余的解決方案。

標(biāo)準(zhǔn)有利于促進(jìn)專門化。在芯片行業(yè)的早期,一個(gè)公司必須完成設(shè)計(jì)、實(shí)現(xiàn)和制造的全部流程。然而,對(duì)于大多數(shù)公司來說,通過定義良好的接口和模型(如PDKs、BSIM模型和庫),是可以將制造與設(shè)計(jì)分離開來的。

IP行業(yè)的出現(xiàn)使公司能夠?qū)W⒂谙到y(tǒng)和差異化部分的設(shè)計(jì),但他們?nèi)匀恍枰约和瓿纱蟛糠值膶?shí)現(xiàn)工作。在IP供應(yīng)商和客戶之間銜接的連接器和模型的標(biāo)準(zhǔn)化為減輕負(fù)擔(dān)提供了可能。

今天,我們正處在另一個(gè)等級(jí)的專業(yè)化風(fēng)口,在這個(gè)等級(jí)上,一個(gè)公司只需要設(shè)計(jì)系統(tǒng),并設(shè)計(jì)和實(shí)現(xiàn)差異化部分,而不用考慮商品化部分的實(shí)現(xiàn)制造。這種模式可以通過小芯片的形式來實(shí)現(xiàn),小芯片是已經(jīng)完全實(shí)現(xiàn)和制造出的小部件,并可以定制化地構(gòu)建系統(tǒng)。為了達(dá)到這個(gè)目標(biāo),行業(yè)需要一些新的標(biāo)準(zhǔn)。

一些大型系統(tǒng)公司已經(jīng)完成了開拓性工作,這些公司都在自研系統(tǒng)和小芯片模塊(圖1)。這使它們能夠提供更大或更加模塊化的產(chǎn)品,并在這個(gè)過程中解決許多難題。他們制造這些系統(tǒng)的方法也都各有不同。

毫不奇怪,這些解決方案差異很大。OpenFive SOC IP產(chǎn)品營銷高級(jí)總監(jiān)KetanMehta表示:“僅僅針對(duì)ASIC公司的需求,行業(yè)就可以被劃分為一系列供應(yīng)產(chǎn)品。這些公司需要的是定制化芯片,而且需要快速的解決方案,他們不想等到標(biāo)準(zhǔn)制定和發(fā)展差不多了才開展業(yè)務(wù)。因此,所有這些公司都在開發(fā)和驗(yàn)證專有的實(shí)現(xiàn)。”

圖1:一些2.5D集成的早期開拓者。圖源:OpenFive第一個(gè)部分開放系統(tǒng)(IP和系統(tǒng)由不同的公司開發(fā))是高帶寬內(nèi)存(high bandwidth memory, HBM)。在這個(gè)系統(tǒng)中,DRAM由一家公司提供,并被集成到另一家公司設(shè)計(jì)的系統(tǒng)中,然后由第三家公司封裝起來。這為適用范圍有限的應(yīng)用提供了一個(gè)解決方案,除此外,還有其他制造/封裝技術(shù)也專注于使內(nèi)存更接近邏輯。

當(dāng)使用現(xiàn)成的小芯片對(duì)邏輯進(jìn)行互聯(lián)時(shí),將獲得更大的受益。這將打破所有部分必須來自同一技術(shù)節(jié)點(diǎn)的限制。盡管這存在諸如差異擴(kuò)展和翹曲導(dǎo)致的可靠性問題,但隨著時(shí)間的推進(jìn),這些問題很可能得到解決。除此外,仍亟待開發(fā)出可行的商業(yè)模式。

對(duì)小芯片的需求來自多個(gè)方向。CHIPS聯(lián)盟執(zhí)行董事RobMains表示:“我們遇到了一個(gè)可以幫助緩解公司在該領(lǐng)域遇到的許多挑戰(zhàn)的真正機(jī)會(huì)。我們需要一個(gè)標(biāo)準(zhǔn)化的交互接口,一個(gè)標(biāo)準(zhǔn)化的物理接口,必須針對(duì)特定的芯片處理技術(shù)或封裝技術(shù)進(jìn)行實(shí)例化。除了這些,需要一個(gè)EDA生態(tài)。DARPA的愿景是正確的,讓全球各個(gè)水平的設(shè)計(jì)團(tuán)隊(duì)合作是很重要的。這有助于達(dá)成共識(shí),并有助于產(chǎn)品的質(zhì)量保障,從而產(chǎn)生有效的結(jié)果。”

今天的行業(yè)并非如此。這與計(jì)算機(jī)科學(xué)家Andrew Tanenbaum的觀察更接近:“標(biāo)準(zhǔn)的好處是有很多選擇。” 但是,隨著越來越多的參與者試圖鞏固該領(lǐng)域并嘗試解決制造封裝與電氣標(biāo)準(zhǔn)息息相關(guān)的問題,這種情況開始發(fā)生變化。我們需要協(xié)議以確保整個(gè)系統(tǒng)中的數(shù)據(jù)完整性。除此之外,還需要解決許多其他問題,例如物理布局,供電網(wǎng)絡(luò),測試,調(diào)試,監(jiān)測以及許多其他問題。大家已經(jīng)開始著手調(diào)查其中的一些問題。

先前的文章討論了小芯片的總體推動(dòng)力以及對(duì)開發(fā)流程的影響。本文的重點(diǎn)是不斷發(fā)展的標(biāo)準(zhǔn),這些標(biāo)準(zhǔn)可能推動(dòng)市場的發(fā)展,雖然這并不能說明所有人的立場或者彼此的關(guān)系。

直播信息

集成400G以太網(wǎng)、GDDR6、PECIe5 高性能7nm FPGA 應(yīng)用公開課(點(diǎn)擊查看)

物理層

從單一封裝布局到多模塊的集成封裝極大地改變了互連。西門子EDA高級(jí)封裝解決方案總監(jiān)Tony Mastroianni說:“傳統(tǒng)的ASIC需要大型I/O驅(qū)動(dòng)器來驅(qū)動(dòng)通過封裝、電路板和外部接口的信號(hào),范圍可能從幾十毫米到幾米。2.5D die-to-die接口部署了較小的I/O驅(qū)動(dòng)器,僅需要通過中介層來驅(qū)動(dòng)與相鄰模塊的水平連接即可,其大小可能在幾十到數(shù)百微米之間。3D die-to-die接口甚至部署了更小的I/O驅(qū)動(dòng)器,僅需要將垂直連接直接驅(qū)動(dòng)到堆疊在其上或下的模塊即可,這些可能在幾納米到幾百納米的數(shù)量級(jí)。2.5和3D方法在本質(zhì)上擁有較低的驅(qū)動(dòng)強(qiáng)度和較短的走線長度,可顯著降低功耗并增加I/O帶寬,從而將能源效率(pJ/bit)提高了幾個(gè)數(shù)量級(jí)。”

在這一方面有幾個(gè)可用方法。“一種小芯片的集成方法完全避免了使用精細(xì)幾何互連,” Kandou標(biāo)準(zhǔn)副總裁Brian Holden說,“通過這種方法,小芯片之間的互連僅僅建立在有機(jī)封裝基板上。這避免了復(fù)雜的制造過程以及與硅中介層相關(guān)的額外成本和良率損失。低功率超短距離(ultra-short reach, USR)SerDes可以用于小芯片之間的高速互連。”

我們可以找到一種物理接口的解決方案。OpenFive的Mehta說:“當(dāng)你將一個(gè)模塊分解為多個(gè)小模塊時(shí),可以將其放在基板上,也可以放在中介層上。這二者之間差別很大。使用中介層可以處理數(shù)千個(gè)信號(hào),而使用基板,最多只能處理幾百個(gè)信號(hào)。例如,如果客戶實(shí)現(xiàn)的是同時(shí)具有HBM的大型模塊,則他們別無選擇,只能在中介層上實(shí)現(xiàn)。這需要并行接口,因?yàn)橹薪閷訉⑷菁{數(shù)千個(gè)信號(hào)。”

英特爾已經(jīng)在圍繞其嵌入式多芯互連橋(Embedded Multi-die Interconnect Bridge , EMIB)開發(fā)自己的小芯片技術(shù)。與2.5D方法特有的大的硅中介層不同,EMIB使用具有多個(gè)布線層的非常小的電橋。這種電橋在基板制造過程中被嵌入并作為其中的一部分。

并行還是串行?

并行和串行之間的爭論可能會(huì)持續(xù)很長時(shí)間,而且不可能有單一的解決方案。每個(gè)不斷發(fā)展的標(biāo)準(zhǔn)都是許多不同因素之間的權(quán)衡。

Synopsys高速SerDes高級(jí)產(chǎn)品經(jīng)理Manmeet Walia解釋說:“客戶真正關(guān)心的是最低延遲,最低功率,各岸端(beachfront)的帶寬,可達(dá)性能以及成本,而這基本都和收益相關(guān)。”

圖2:定義可接受的接口。圖源:Cadence

標(biāo)準(zhǔn)正在朝著多個(gè)方向發(fā)展,以優(yōu)化各種設(shè)計(jì)因素。“串行連接使用非常輕巧的SerDes,” Walia說,“它們具有簡單的物理接口,只基于DLL時(shí)鐘的轉(zhuǎn)發(fā)方法,不需要任何決策反饋等化。”

串行標(biāo)準(zhǔn)由光學(xué)互聯(lián)網(wǎng)絡(luò)論壇(Optical Internetworking Forum, OIF)推動(dòng)。他說:“這被稱為112G USR或超短距離(extra short reach, XSR)連接。這些應(yīng)該最遲在2021年內(nèi)得到批準(zhǔn)。但是要記住各項(xiàng)活動(dòng)不是基于標(biāo)準(zhǔn)批準(zhǔn)書開展的。它們是根據(jù)已經(jīng)可用的草案而進(jìn)行的。OIF的草案現(xiàn)在可以獲取了。”

在并行方面有一些標(biāo)準(zhǔn)的提出。首先是開放式高帶寬互連(Open High Bandwidth Interconnect, OpenHBI)。這是由開放計(jì)算項(xiàng)目(Open Compute Project's , OCP)的開放領(lǐng)域?qū)S皿w系結(jié)構(gòu)(Open Domain-SpecificArchitecture, ODSA)子項(xiàng)目領(lǐng)導(dǎo)的。預(yù)計(jì)在今年年中批準(zhǔn)。

英特爾已經(jīng)開發(fā)了高級(jí)接口總線(Advanced Interface Bus, AIB)。英特爾可編程解決方案小組CTO辦公室高級(jí)總監(jiān)Jose Alvarez說:“ AIB 2.0的規(guī)范已經(jīng)可以在CHIPS Alliance GitHub找到。這項(xiàng)工作正在進(jìn)行中,馬上要發(fā)布了。我們的目標(biāo)是達(dá)到每條線每秒4GB,每個(gè)接口每秒約7.6TB的帶寬。但這不僅僅和帶寬有關(guān),而且和能耗有關(guān)。目前每比特的能源利用率是0.85pJ,我們達(dá)到了每比特0.5pJ,而DARPA PIPES項(xiàng)目希望將其提高到每比特0.1pJ。這是一個(gè)更長的范圍,但是我們正在朝著這個(gè)方向努力。”

許多公司已經(jīng)部署了一種稱為“電線束”(Bunch Of Wires, BOW)的方法。GUC在2020年11月發(fā)布的新聞稿中展示了這種接口的一些性能數(shù)據(jù),并展示了一些性能權(quán)衡。它引用了模塊之間的無差錯(cuò)通信,每1 mm 各岸端全雙工帶寬為0.7 Tbps,消耗0.25 pJ/bit。GUC相信,下一代產(chǎn)品將支持每1 mm各岸端 1.3Tbps的無錯(cuò)全雙工帶寬,而使用TSMC 5nm工藝的功耗則為0.25 pJ /bit。

與串行連接相比如何?GUC表示,與使用超短距離基于SerDes的封裝基板通信的替代解決方案相比,并行連接的功耗要低6至10倍。

協(xié)議

芯片之間可靠的數(shù)據(jù)傳輸不僅僅需要物理接口。Fraunhofer IIS自適應(yīng)系統(tǒng)工程部高級(jí)系統(tǒng)集成小組負(fù)責(zé)人兼高效電子部門負(fù)責(zé)人Andy Heinig表示:“未來需要更高級(jí)別的標(biāo)準(zhǔn),而不是非常低級(jí)的接口標(biāo)準(zhǔn)。這種更高級(jí)別的協(xié)議可能是面向應(yīng)用程序的。它們?cè)谙窆鈱W(xué)前端的模擬-數(shù)字應(yīng)用或像數(shù)據(jù)中心AI應(yīng)用加速器的數(shù)字加速器之間將有所不同。”

生產(chǎn)力和可重用性與抽象層級(jí)有關(guān)。“互連的下一層是在通信結(jié)構(gòu)、協(xié)議、總線、網(wǎng)絡(luò)方面。” Arteris IP的研究員兼系統(tǒng)架構(gòu)師Michael Frank說,“ CCIX和CXL即將到來。人們正在對(duì)其進(jìn)行構(gòu)建,但是缺乏可以使不同小芯片通信的標(biāo)準(zhǔn)。”

計(jì)算表示連接(Compute Express Link, CXL)是用于處理器、內(nèi)存擴(kuò)展和加速器的緩存一致性互連。其2.0規(guī)范于2020年11月發(fā)布。目標(biāo)是保持CPU內(nèi)存空間與連接設(shè)備上的內(nèi)存之間的內(nèi)存一致性,從而實(shí)現(xiàn)資源共享并降低軟件堆棧的復(fù)雜性。

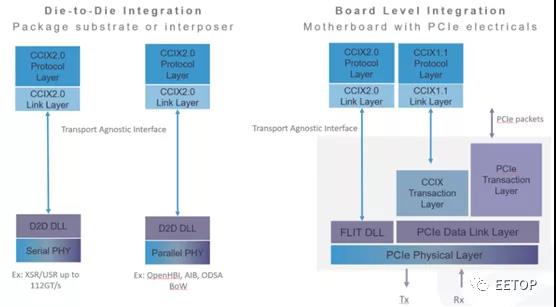

同樣,用于加速器的高速緩存一致性互連(Cache Coherent Interconnect for Accelerators, CCIX)已從系統(tǒng)內(nèi)應(yīng)用程序轉(zhuǎn)移到封裝內(nèi)應(yīng)用程序。“隨著2.5D和小芯片的推動(dòng),我們基本上擺脫了長延遲和高功率SerDes或接口,并具有并行接口或非常低延遲的XSR或短距離SerDes,”CCIX聯(lián)合體技術(shù)指導(dǎo)委員會(huì)主席,并在Xilinx擔(dān)任CCIX、CXL和ODSA聯(lián)合體的技術(shù)負(fù)責(zé)人Millind Mittal說道,“ CCIX利用了PCIe的數(shù)據(jù)鏈路層,但之后將其分離為優(yōu)化路徑。我們正在定義下一個(gè)版本,以適應(yīng)新的傳輸方式。對(duì)于2.0,我們正在考慮適應(yīng)封裝內(nèi)集成選項(xiàng)。”(見圖3)

圖3:CCIX 2.0集成選項(xiàng)。圖源:CCIX聯(lián)盟

Arm也提出了一個(gè)標(biāo)準(zhǔn)。Walia說:“這是結(jié)構(gòu)的一部分,他們擁有所謂的相干網(wǎng)格網(wǎng)絡(luò)(Coherent Mesh Network, CMN)結(jié)構(gòu)。如果你在模塊到模塊的接口上有兩個(gè)計(jì)算芯片互相通信,那么結(jié)構(gòu)到結(jié)構(gòu)的接口須看起來像是單個(gè)結(jié)構(gòu)。這里零延遲是非常重要的。”

不僅僅是信號(hào)

獲取信號(hào)接口標(biāo)準(zhǔn)很重要,但是要制造可重用的小芯片,還需要更多的標(biāo)準(zhǔn)。“我們今天必須定制IP。” Walia說,“這可能意味著移除標(biāo)準(zhǔn)的C4,并用微型接觸點(diǎn)替換它們。我們緊密合作,多次迭代。在我們與客戶及其封裝供應(yīng)商之間經(jīng)常會(huì)有三到四次的迭代。”

其中一些問題正在得到解決。Mehta說:“ ODSA和AIB已經(jīng)提出了一種接觸點(diǎn)布局。它定義了SerDes的布局方式或并行線的布局方式。當(dāng)兩個(gè)設(shè)備屬于同一客戶時(shí),它們具有一點(diǎn)靈活性。但是,如果不是閉環(huán)系統(tǒng),那么對(duì)于如功率和熱量的許多事物,都需要標(biāo)準(zhǔn)。”

功率是一個(gè)大問題。“如何通過這些微型接觸點(diǎn)來承擔(dān)100瓦的功率?” Ansys產(chǎn)品營銷總監(jiān)Marc Swinnen問, “你需要有一個(gè)單獨(dú)的電源分配連接,物理連接方案,厚型TSV或什么可以在芯片中承擔(dān)功率的東西。當(dāng)今最常用的技術(shù)是將微型接觸點(diǎn)的集合聚合到作為單個(gè)連接的接觸點(diǎn)區(qū)域中。因此,可以選擇其中的100個(gè),它們都是Vss或Vdd,并且它們都可以協(xié)同工作,電流將分配給各個(gè)接觸點(diǎn)。現(xiàn)在,必須進(jìn)行非常仔細(xì)的分析,以確保所有這些接觸點(diǎn)都不會(huì)過熱而導(dǎo)致局部熔化。”

我們也需要額外模型。“我需要一個(gè)這樣的功率模型,那樣的熱量模型。” Cadence的IC封裝和跨平臺(tái)解決方案產(chǎn)品管理小組主管John Park說, “針腳間距標(biāo)準(zhǔn)是什么?當(dāng)人們開始思考小芯片到小芯片接口的標(biāo)準(zhǔn)時(shí),要考慮一份檢查清單。我相信對(duì)此沒有一個(gè)單一標(biāo)準(zhǔn)。可能會(huì)有5個(gè),10個(gè),甚至更多。封裝的種類繁多,沒有標(biāo)準(zhǔn)適用于所有內(nèi)容。雖然最后我們都會(huì)找到。大型設(shè)計(jì)中可能有數(shù)十個(gè)甚至可能數(shù)百個(gè)小芯片,如果使用層壓板進(jìn)行設(shè)計(jì),整個(gè)面積可能會(huì)變得很大。那么信號(hào)需要傳播多長距離?”

隨著重大問題的解決,新的問題將會(huì)浮出水面。英特爾的Alvarez說:“在CHIPS聯(lián)盟內(nèi)部,通過AIB 2.0,我們正在向小芯片添加其他概念,例如安全性。我們還在尋找其他方法處理接口,協(xié)議等。我們希望為小芯片開發(fā)提供更完整的硬件框架。”

結(jié)論

半導(dǎo)體行業(yè)正在通過標(biāo)準(zhǔn)整合專有小芯片。今天,許多專有解決方案已交由標(biāo)準(zhǔn)機(jī)構(gòu)處理。整個(gè)行業(yè)正在整合這些解決方案,但是只有一定程度的合并是可能的,或者可能符合我們的需求。

案例將推動(dòng)提案的采用率,如果取得初步成功,那么這個(gè)方向?qū)?huì)冒出更多案例,但是它們都可能需要標(biāo)準(zhǔn)做出一些變化,因?yàn)殪`活性和優(yōu)化始終很難平衡。