小芯片(Chiplet)已經(jīng)成為當(dāng)今大廠角逐的一大方向,對(duì)于小芯片來(lái)說(shuō),需要一種芯片到芯片的互連/接口技術(shù),現(xiàn)在已有多種Die-to-Die接口可以滿足這類需求。其中,基于SerDes的或并行的Die-to-Die接口在數(shù)據(jù)速率、引腳數(shù)量和成本等方面都有其獨(dú)特的優(yōu)勢(shì)。但在設(shè)計(jì)用于諸如數(shù)據(jù)中心、人工智能 (AI) 訓(xùn)練或推理、服務(wù)器和網(wǎng)絡(luò)等高性能計(jì)算 (HPC) 應(yīng)用的高端Muiti-die SoC時(shí),為了讓不同的供應(yīng)商開(kāi)發(fā)的Multi-Die SoC實(shí)現(xiàn)互操作,業(yè)界正著力于建立Multi-Die的互連標(biāo)準(zhǔn),以維護(hù)一個(gè)成功的生態(tài)系統(tǒng)。

在眾多Die-to-Die互聯(lián)標(biāo)準(zhǔn)中,OpenHBI已成為提供最高邊緣密度的標(biāo)準(zhǔn),非常適用于必須在兩個(gè)Chiplet之間傳輸極高帶寬的HPC應(yīng)用。

為何使用并行 Die-to-Die 接口?

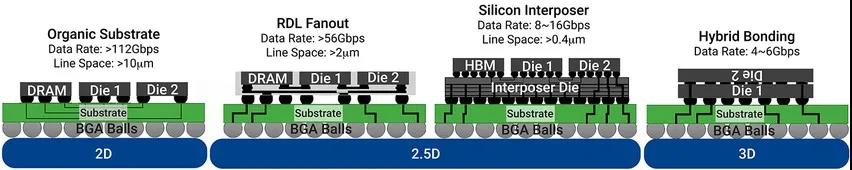

現(xiàn)在多家芯片廠商利用小芯片模型將芯片集成到現(xiàn)有的高級(jí)封裝類型中,這些裸片可以是不同工藝節(jié)點(diǎn)的,裸片可以并排放置,并通過(guò)專用die-to-die接口相連接,這是一種普遍且成本較低的方法。如想獲得更高的密度,可以將這些組塊封裝在2.5D或3D設(shè)計(jì)中。

在此,我們先科普下常見(jiàn)的三種封裝形式,一個(gè)是2D封裝,把各個(gè)Chiplet組裝在有機(jī)基材和層壓板上;一個(gè)是2.5D封裝,它的中介層使用硅或再分配層 (RDL) 扇出,用于在SoC中傳遞Chiplet間的信號(hào);還有一個(gè)是3D封裝,它使用混合粘合技術(shù)來(lái)垂直堆疊Chiplet。

圖 1:封裝選項(xiàng)

其中2.5D封裝由于采用RRL扇出技術(shù),能夠橋接2D技術(shù)的低成本和硅中介層的密度,又有許多代工廠以及傳統(tǒng)的OSAT提供商可提供此類服務(wù),進(jìn)一步降低了成本,因此成為了一種有吸引力的選擇。

對(duì)于那些對(duì)封裝成本和復(fù)雜度不敏感的高性能計(jì)算 SoC,并行Die-to-Die接口已成為首選技術(shù)。這主要是因?yàn)椋⑿蠨ie-to-Die接口基本上都包含了大量的(上千個(gè))IO 引腳,來(lái)驅(qū)動(dòng)跨Chiplet的單端信號(hào)。由于每個(gè)引腳的數(shù)據(jù)速率僅為幾個(gè)G字節(jié)/秒 (Gbps)(8至16 Gbps),且Chiplet之間的距離僅為幾毫米(3至5毫米),因此驅(qū)動(dòng)器和接收器都可以簡(jiǎn)化,同時(shí)實(shí)現(xiàn)遠(yuǎn)低于1e-22至1e-24的系統(tǒng)誤碼率 (BER)。不需要額外的糾錯(cuò)機(jī)制,例如前向糾錯(cuò) (FEC) 和重試,系統(tǒng)BER就可以滿足要求,從而避免增加鏈路復(fù)雜性和延遲。

通過(guò)簡(jiǎn)化IO、消除串并轉(zhuǎn)換 (SerDes) 步驟,并避免超高速信號(hào)傳輸,并行Die-to-Die接口能夠?qū)崿F(xiàn)極高的能效和較低的延遲,同時(shí)支持整個(gè)鏈路的極高吞吐量。因此,并行Die-to-Die接口對(duì)于不受封裝成本和裝配限制的高性能計(jì)算應(yīng)用SoC非常有吸引力。

Die-to-Die接口標(biāo)準(zhǔn)應(yīng)運(yùn)而生

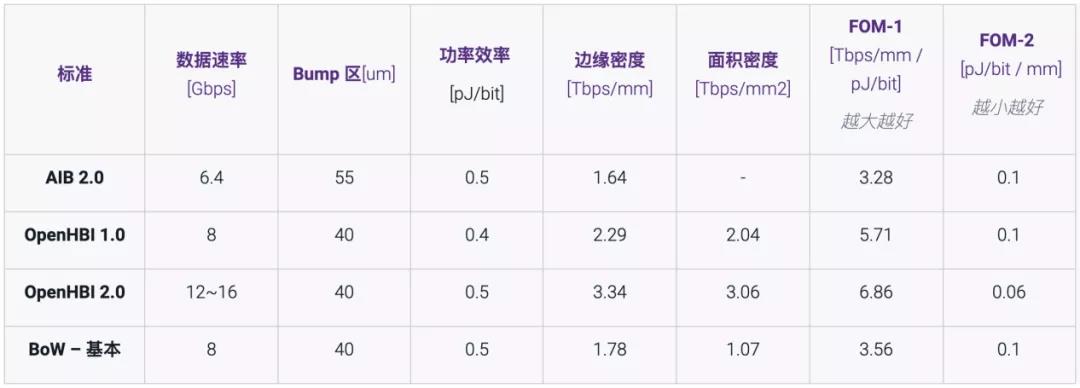

現(xiàn)在的小芯片方案,各家都為并行Die-to-Die接口部署了許多專有架構(gòu)。為了建立一個(gè)穩(wěn)健的生態(tài)系統(tǒng),讓不同的供應(yīng)商所開(kāi)發(fā)的以及不同功能的Chiplet互聯(lián)操作,行業(yè)開(kāi)始制定Die-to-Die接口標(biāo)準(zhǔn),主要包括AIB、OpenHBI、BoW等,為先進(jìn)封裝中的并行Die-to-Die接口提供特性。表1顯示了不同標(biāo)準(zhǔn)的主要特性比較。

表 1:先進(jìn)封裝的并行Die-to-Die接口標(biāo)準(zhǔn)

(來(lái)源:OCP Tech Week全球技術(shù)峰會(huì),2020年11月)

先進(jìn)封裝由于凸塊間距大,封裝路由密度高,在同等能效的情況下,對(duì)外形尺寸和邊緣效率的要求更高。在以上這些標(biāo)準(zhǔn)中,OpenHBI能提供最高邊緣密度的標(biāo)準(zhǔn),非常適用于必須在兩個(gè)Chiplet之間傳輸極高帶寬的應(yīng)用。它可達(dá)到每引腳8Gbps的速度,在最大的數(shù)據(jù)速率下可以達(dá)到3mm的最大互連長(zhǎng)度,并實(shí)現(xiàn)小于或等于0.5pJ/bit的功耗目標(biāo)。

什么是 OpenHBI?

OpenHBI利用JEDEC的HBM3電氣特性和IO類型來(lái)降低風(fēng)險(xiǎn)。它使用低電壓和未端接的單端 DDR 信號(hào)來(lái)傳輸Chiplet之間的數(shù)據(jù)。

OpenHBI標(biāo)準(zhǔn)具有許多關(guān)鍵特征:

整合多個(gè)OpenHBI兼容的Die-to-Die接口,實(shí)現(xiàn)互操作性

利用JEDEC HBM3 IO類型和電氣特性

可與支持HBM存儲(chǔ)器和OpenHBI標(biāo)準(zhǔn)的雙模HBM主機(jī)控制器互操作

支持硅中介層和晶圓級(jí)集成扇出或同等技術(shù)

實(shí)現(xiàn)對(duì)稱Die-to-Die接口

實(shí)現(xiàn)目標(biāo)速度:每引腳 8Gbps,正邁向12-16Gbps

在最高數(shù)據(jù)傳輸速率時(shí)提供長(zhǎng)達(dá)3mm的互連距離

實(shí)現(xiàn)小于等于0.5pJ/bit的功耗目標(biāo)

提供大于1.5T位/毫米(包括發(fā)射器和接收器)的線性(邊緣)帶寬密度

定義 PHY 和邏輯 PHY 抽象層,輕松適配上層

支持正常的和旋轉(zhuǎn)的Chiplet方向

可以調(diào)整帶寬和邊緣(DW 數(shù)量)以匹配各種用例

支持小芯片 (Chiplet) 配置和測(cè)試 (CCT) 接口

支持通道修復(fù),提高制造良率

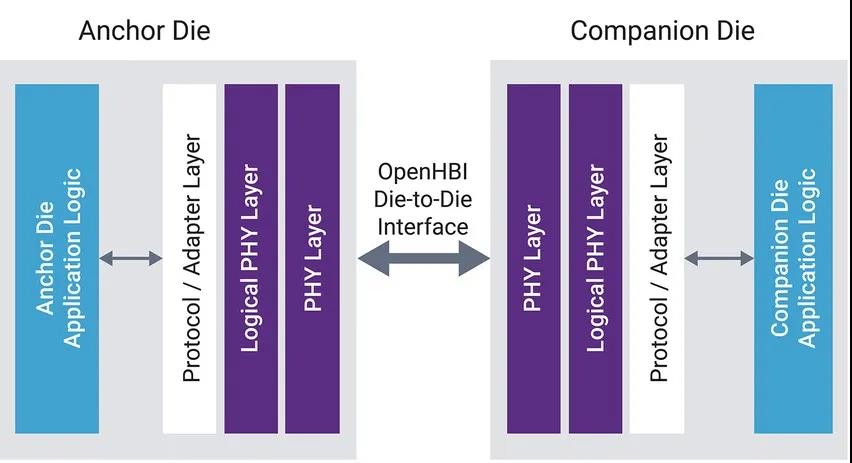

OpenHBI標(biāo)準(zhǔn)主要針對(duì)圖2所示的下層(PHY和邏輯PHY層),然后將適配器層用于與上層(協(xié)議層)進(jìn)行連接。因此,系統(tǒng)可實(shí)現(xiàn)不依賴于各個(gè)應(yīng)用所用的協(xié)議。

圖 2:OpenHBI 接口邏輯劃分

PHY層主要執(zhí)行提供時(shí)鐘、變速器(數(shù)據(jù)速率轉(zhuǎn)換 N:1)、校準(zhǔn)和訓(xùn)練、通道修復(fù)以及數(shù)據(jù)傳輸和恢復(fù)的功能。如果需要,邏輯 PHY層將執(zhí)行以下功能:奇偶校驗(yàn)生成和校驗(yàn)、數(shù)據(jù)成幀和對(duì)齊、數(shù)據(jù)總線反向、位重新排序。

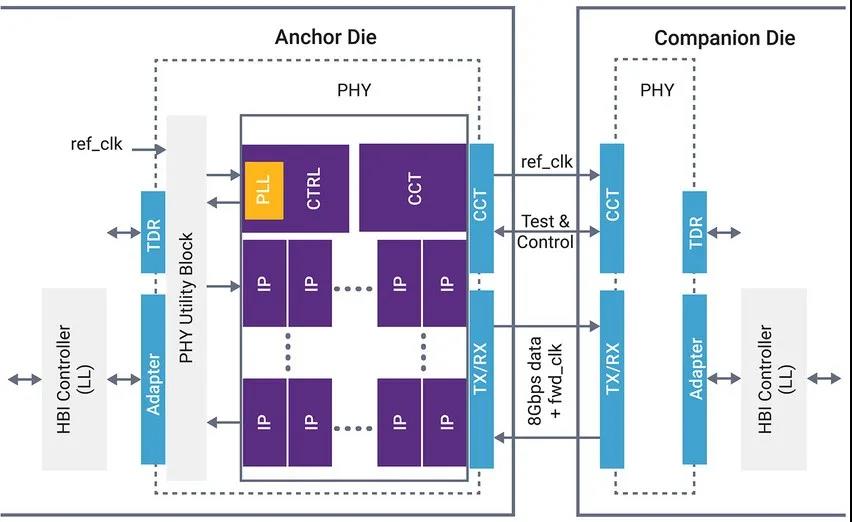

圖3展示了一種OpenHBI PHY實(shí)現(xiàn)方案,可以將不同的功能分割到不同的實(shí)現(xiàn)中。

圖 3:OpenHBI PHY IP模塊圖

PHY使用時(shí)鐘轉(zhuǎn)發(fā)技術(shù),其中傳輸時(shí)鐘和數(shù)據(jù)也在Chiplet之間傳輸。接收端基于DLL的簡(jiǎn)單數(shù)據(jù)恢復(fù)電路,可節(jié)省功耗和面積。

除了有效載荷數(shù)據(jù)路徑外,PHY還實(shí)現(xiàn)低速CCT,可供錨芯片和小芯片用于傳達(dá)配置和狀態(tài)參數(shù)以及控制DWORD初始化、校準(zhǔn)和測(cè)試過(guò)程。OpenHBI PHY實(shí)現(xiàn)I3C、JTAG和供應(yīng)商自定義信號(hào)。此外,CCT將參考時(shí)鐘從錨芯片傳播到小芯片Chiplet,以便它們共享相同的時(shí)鐘參考。

OpenHBI PHY的其他主要功能包括:

帶有APB/TDR接口的配置端口,用于訪問(wèn)內(nèi)部控制和狀態(tài)寄存器 (CSR)

可配置PHY,支持多種DWORD數(shù)量,以適應(yīng)具體用例

裸片測(cè)試(已知良好Chiplet)和封裝后測(cè)試的綜合可測(cè)試性,包括關(guān)鍵模塊 BIST、各種環(huán)回模式、模式生成和匹配能力,以及生成重建的眼圖,作為 pass/fail 測(cè)試。

新思科技IP助力小芯片的互聯(lián)

一些芯片設(shè)計(jì)公司可能擁有開(kāi)發(fā)自己的小芯片和IP的資源,但即使是較大的公司也負(fù)擔(dān)不起內(nèi)部開(kāi)發(fā)所有IP的費(fèi)用。他們可能希望采購(gòu)第三方IP以節(jié)省時(shí)間和金錢(qián)。

在這樣的背景下,新思科技可提供一系列Die-to-Die IP,包括高帶寬互聯(lián) (HBI) 和基于SerDes的PHY和控制器。DesignWare? HBI PHY IP支持多種標(biāo)準(zhǔn),包括AIB、BoW和OpenHBI。該IP實(shí)現(xiàn)了一個(gè)寬并行和時(shí)鐘轉(zhuǎn)發(fā)的PHY接口,以先進(jìn)的2.5D封裝為目標(biāo),以利用基于內(nèi)插器的技術(shù)中更精細(xì)的芯片到芯片連接。

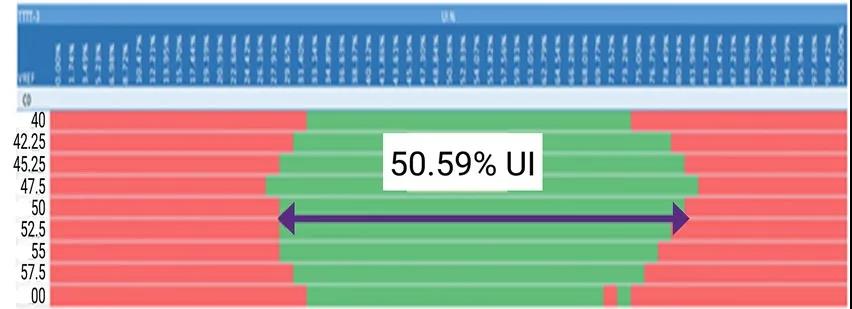

圖 4:使用新思科技HBI+PHY的Die-to-Die鏈路的眼圖

無(wú)疑,小芯片的發(fā)展前景廣闊,尤其是摩爾定律走到極限的情況下,但是小芯片仍然面臨諸多難題,如設(shè)計(jì)和集成、生態(tài)系統(tǒng)復(fù)雜性、制造/測(cè)試和產(chǎn)量,資質(zhì)和可靠性、標(biāo)準(zhǔn)等,但業(yè)界正在圍繞著這些難題逐個(gè)攻克,相信,未來(lái)會(huì)有更多的應(yīng)用采用小芯片的方案。