現(xiàn)代微處理器是世界上最復(fù)雜的系統(tǒng)之一,但其核心是一個(gè)非常簡單而優(yōu)美的器件——晶體管。如今的微處理器中有數(shù)十億個(gè)近乎完全相同的晶體管。因此,提高晶體管的性能和密度是促使微處理器及受其驅(qū)動(dòng)的計(jì)算機(jī)更高效工作的最直接的方法。

這是摩爾定律的前提,即便現(xiàn)在它已經(jīng)(幾乎)走向了終點(diǎn)。制造更小、更好的微處理器晶體管愈發(fā)困難,而且昂貴無比。只有英特爾、三星和臺(tái)積電(TSMC)具備在這一微型化前沿領(lǐng)域開展業(yè)務(wù)的能力。它們都在制造相當(dāng)于7納米節(jié)點(diǎn)的集成電路。這是摩爾定律初期遺留下來的名稱,現(xiàn)已沒有明確的實(shí)際意義,但它仍然反映了集成電路功能和器件微型化的程度。

目前7納米制造工藝已屬前沿技術(shù),但三星和臺(tái)積電今年4月宣布,他們將開始轉(zhuǎn)向5納米節(jié)點(diǎn)。三星還另外宣布,公司認(rèn)為,行業(yè)使用了近10年的晶體管已經(jīng)完成使命,新一代3納米節(jié)點(diǎn)將在2020年前后開始限量生產(chǎn),目前它正用于一項(xiàng)全新設(shè)計(jì)。

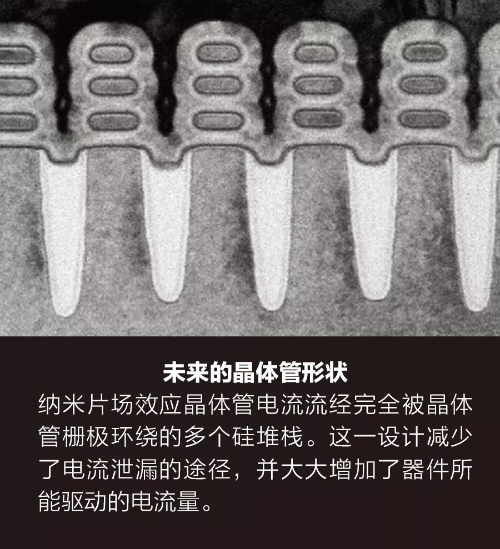

這類晶體管名稱繁多,有環(huán)繞式柵極、多橋溝道、納米梁等,但在研究領(lǐng)域,我們一直稱它為納米片。名稱不是很重要,重要的是,它并非只是為邏輯芯片設(shè)計(jì)的下一代晶體管;它很可能是最后一代。當(dāng)然,側(cè)重的主題會(huì)有所變化,但從現(xiàn)在起可能全部都是納米片。

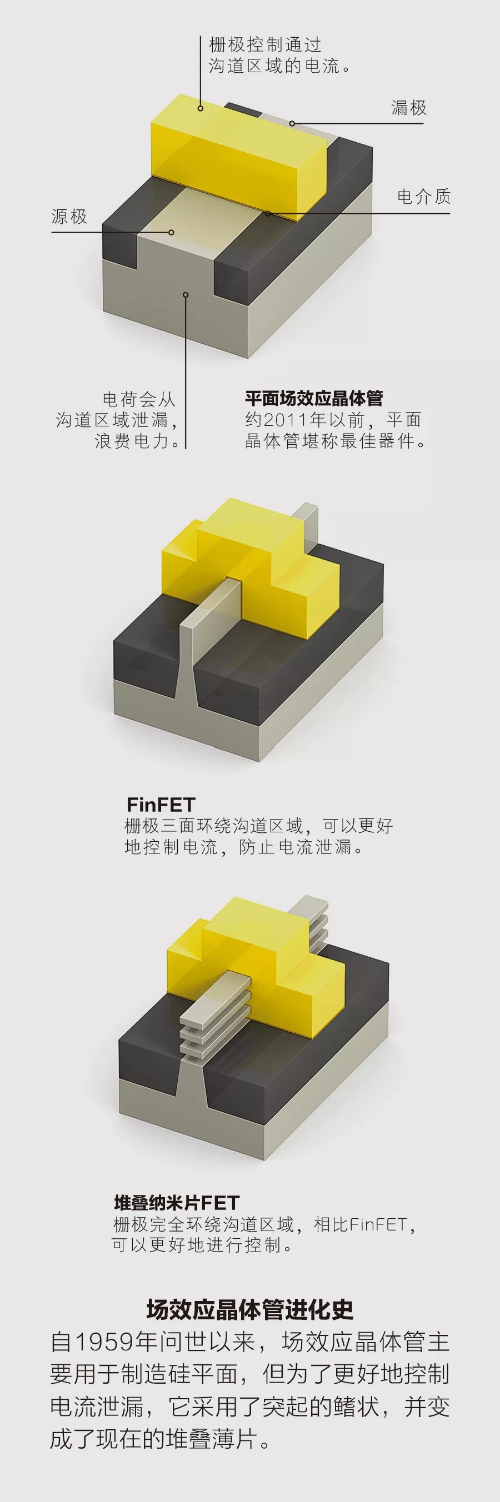

金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET,即微處理器中使用的晶體管)自1959年誕生以來,其形狀和材料都發(fā)生了變化,但基本結(jié)構(gòu)(柵極疊層、溝道區(qū)域、源極和漏極)一直保持不變。在其原始形式中,源極、漏極和溝道基本上是硅摻雜其他元素原子的區(qū)域,這樣就可以形成一個(gè)移動(dòng)負(fù)電荷豐度(n型)或一個(gè)移動(dòng)正電荷豐度(p型)區(qū)域。我們需要兩種類型的晶體管來實(shí)現(xiàn)構(gòu)成當(dāng)前計(jì)算機(jī)芯片的互補(bǔ)金屬氧化物半導(dǎo)體(CMOS)技術(shù)。

MOSFET的柵極疊層位于溝道區(qū)域的正上方。當(dāng)前的柵極疊層由介電材料層上的金屬(用于柵極)制成。這種組合旨在使晶體管溝道區(qū)域形成電場(chǎng),同時(shí)防止電荷泄漏。

向柵極施加足夠大的電壓(相對(duì)于源極),就會(huì)在電介質(zhì)和硅之間的界面附近形成一層移動(dòng)電荷載流子。電荷載流子完全橋接源極和漏極后,電流即可通過。將柵極電壓降至接近于零,會(huì)關(guān)閉傳導(dǎo)通路。

當(dāng)然,要使電流從源極流向漏極,首先需要在溝道上設(shè)置電壓。隨著晶體管結(jié)構(gòu)越來越小,這種電壓帶來的影響最終會(huì)導(dǎo)致晶體管歷史上最大的形狀變化。

這是因?yàn)樵礃O-漏極電壓可以在電極之間形成自身的導(dǎo)電區(qū)域。隨著每一代晶體管誕生,溝道區(qū)域越來越短,漏極電壓的影響也越來越大。電荷會(huì)泄漏到柵極附近區(qū)域下方,從而導(dǎo)致晶體管永遠(yuǎn)不會(huì)完全關(guān)閉,浪費(fèi)電能并產(chǎn)生熱量。

為了阻止多余的電荷流,溝道區(qū)域必須變薄,從而限制電荷通過的路徑。柵極需要從多個(gè)側(cè)面環(huán)繞溝道。因此,鰭式場(chǎng)效應(yīng)晶體管(FinFET)應(yīng)運(yùn)而生。其溝道區(qū)域的兩側(cè)向上傾斜,在源極和漏極之間形成了一個(gè)細(xì)長的“硅鰭”,為電流流通提供了更寬的通道。之后柵極和電介質(zhì)以三面而非一面覆蓋在鰭上。

FinFET無疑取得了巨大成功。雖然FinFET在十多年前就已問世,但直到2011年,英特爾才率先推出了商業(yè)化的22納米節(jié)點(diǎn)FinFET,三星、臺(tái)積電等公司緊隨其后。從那時(shí)起,在摩爾定律擴(kuò)展的最后階段,它始終是尖端硅邏輯的主力。可惜花無百日紅。

FinFET無法向3納米節(jié)點(diǎn)推進(jìn)。十多年前,我們?nèi)撕推渌艘粯樱赃@樣或那樣的形式預(yù)見到了這一點(diǎn)。

盡管FinFET性能優(yōu)越,但它自身也存在著問題。首先,它引入了一個(gè)原“平面”晶體管沒有的設(shè)計(jì)缺陷。要認(rèn)清這個(gè)問題,必須了解到,在晶體管的速度、功耗、制造復(fù)雜性和成本之間需要相互權(quán)衡。這種權(quán)衡與溝道寬度有很大關(guān)系,溝道寬度在器件設(shè)計(jì)領(lǐng)域稱為Weff。寬度增大意味著可以驅(qū)動(dòng)更多的電流,更快地開關(guān)晶體管,但這也會(huì)導(dǎo)致制造過程更復(fù)雜、成本更高。

在平面器件中,可以通過調(diào)整溝道的幾何形狀來進(jìn)行平衡,但是FinFET鰭的靈活性欠佳。連接晶體管形成電路的金屬互連線成層地排布在晶體管之上。正因如此,在不干擾互連層的情況下,晶體管鰭的高度(相當(dāng)于平面設(shè)計(jì)中的寬度)不能發(fā)生太大變化。如今,芯片設(shè)計(jì)師通過制造具有多個(gè)鰭的單個(gè)晶體管來解決這一問題。

FinFET的另一個(gè)短板是,它的柵極僅三面環(huán)繞矩形硅鰭,使得底部與硅體相連,因而泄漏電流可以在晶體管關(guān)閉時(shí)流動(dòng)。許多研究人員推斷,要實(shí)現(xiàn)對(duì)溝道區(qū)域的終極控制,柵極需要完全將其環(huán)繞。

至少在1990年,研究人員就已經(jīng)得出這一合乎邏輯的結(jié)論。當(dāng)年,研究人員報(bào)道了首個(gè)柵極完全環(huán)繞溝道區(qū)域的硅器件。從那時(shí)起,便有一代研究人員致力于環(huán)繞式柵極。到2003年,研究人員試圖最大程度地減少泄漏,將溝道區(qū)域變成一條狹窄的納米線。納米線連接著源極和漏極,并被柵極四面環(huán)繞。

那么,為何環(huán)繞式納米線無法構(gòu)成最新晶體管的基礎(chǔ)?同樣,還是溝道寬度的問題。電子幾乎無法從細(xì)導(dǎo)線逃逸,因此當(dāng)晶體管應(yīng)當(dāng)關(guān)閉時(shí),它就會(huì)關(guān)閉,但當(dāng)晶體管打開時(shí),它也無法為電子提供流動(dòng)空間,會(huì)限制電流,降低開關(guān)速度。

將納米線堆疊在一起,使寬度增加,可以獲得更多Weff以及電流。三星公司的工程師在2004年推出了這種結(jié)構(gòu),稱為多橋溝道FET。不過它也存在一些局限性。首先,像FinFET的鰭一樣,堆疊不能太高,否則會(huì)干擾互連層。另一方面,每增加一條納米線就會(huì)擴(kuò)大器件的電容,減慢晶體管的開關(guān)速度。最后,由于制造極細(xì)納米線頗為復(fù)雜,它們的邊緣往往很粗糙。表面粗糙會(huì)阻礙電荷載流子的速度。

2006年,在法國原子能委員會(huì)電子與信息技術(shù)實(shí)驗(yàn)室(CEA-Leti),與我們中的一員(本文作者Ernst))合作共事的工程師提出了一個(gè)更好的想法。他們沒有通過堆疊納米線來連接源極和漏極,而是堆疊薄硅片。他們的想法是,在更小的晶體管中增加溝道寬度,同時(shí)嚴(yán)格控制泄漏電流,從而提供性能更優(yōu)、功耗更低的器件。在我們另一個(gè)成員(Khare)的指導(dǎo)下,2017年,IBM研究院進(jìn)一步推進(jìn)了這一概念,表明由堆疊納米片制成的晶體管實(shí)際上能比占相同芯片面積的FinFET提供更多的電力。

納米片設(shè)計(jì)還有另外一個(gè)好處:它恢復(fù)了過渡到FinFET時(shí)失去的靈活性。納米片可以加寬來增加電流,也可以縮窄來降低功耗。IBM研究院已將它們分成3個(gè)堆棧,尺寸從8納米到50納米不等。

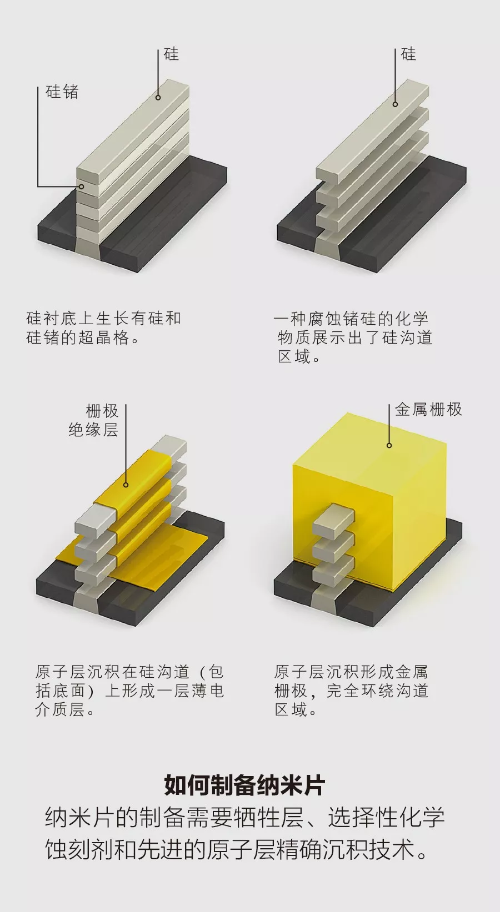

如何制造納米片晶體管?考慮到多數(shù)半導(dǎo)體制造工藝都是從硅的頂部直接切割,或者從暴露的表面直接填充的,這似乎是一項(xiàng)艱巨的任務(wù)。納米片需要去除其他材料層之間的材料,并用金屬和電介質(zhì)填充這些間隙。

主要訣竅在于構(gòu)造所謂的超晶格,這是一種由硅和鍺硅兩種材料組成的周期性層狀晶體。研究人員已經(jīng)制造了19層超晶格,但鑒于相關(guān)機(jī)械應(yīng)力和電容,使用如此多層晶格有失明智。在選擇適當(dāng)?shù)膶訑?shù)后,我們使用了一種化學(xué)物質(zhì),能夠選擇性地蝕刻鍺硅,但對(duì)硅不做處理,只留硅納米片連接源極和漏極。實(shí)際上這并不是什么新想法;20年前,法國電信和意法半導(dǎo)體公司的工程師在實(shí)驗(yàn)性的“空洞層上的硅”(silicon-on-nothing)晶體管中就使用了這種技術(shù),在晶體管溝道區(qū)域下方掩埋了一層空氣來力圖限制短溝道效應(yīng)。

構(gòu)建好硅納米片溝道區(qū)域后,就需要填補(bǔ)溝道空隙。首先用電介質(zhì)環(huán)繞溝道,然后用金屬形成柵極疊層。這兩個(gè)步驟均采用了十多年前才引入半導(dǎo)體制造領(lǐng)域的原子層沉積技術(shù)來完成。在這一過程中,一種氣態(tài)化學(xué)物質(zhì)會(huì)被吸附到芯片裸露的表面甚至是納米片的底部,形成單層。之后加入第二種化學(xué)物質(zhì),與前一種化學(xué)物質(zhì)發(fā)生反應(yīng),留下所需物質(zhì)(如電介質(zhì)二氧化鉿)的原子層。這一過程極為精確,沉積材料的厚度甚至可以控制到單個(gè)原子層。

納米片設(shè)計(jì)的一個(gè)驚人之處是,它可以延伸摩爾定律,這實(shí)際上超越了硅在溝道中的應(yīng)用。問題在很大程度上在于熱量。

晶體管的密度隨著每一個(gè)技術(shù)節(jié)點(diǎn)的增加而增加,但是十年來集成電路能夠合理消除的熱量(功率密度)依然保持在每平方厘米100瓦左右。芯片制造商已竭盡全力避免超出這一基本限制。為了降低溫度,時(shí)鐘頻率不超過4千兆赫。處理器行業(yè)轉(zhuǎn)向了多核設(shè)計(jì),正確地推斷出幾個(gè)較慢的處理器核心可以在產(chǎn)生較少熱量的情況下,完成與單個(gè)快速處理器相同的工作。要想再次提高時(shí)鐘速度,需要比硅更節(jié)能的晶體管。

有一種可能的解決方案是將新材料引入溝道區(qū)域,如鍺或由元素周期表第三列和第五列元素組成的半導(dǎo)體,如砷化鎵。在某些半導(dǎo)體中,電子的移動(dòng)速度可以提高10倍以上,因此這些材料制成的晶體管開關(guān)速度可以加快。更重要的是,電子移動(dòng)速度更快,這樣就可以在較低的電壓下操作設(shè)備,從而提高能源效率,減少熱量產(chǎn)生。

受早期納米線晶體管和超晶格結(jié)構(gòu)研究的啟發(fā),我們其中的一員(葉培德)在2012年用銦鎵砷化鎵(III-V族半導(dǎo)體)構(gòu)造出了一些三納米片器件。結(jié)果好于預(yù)期。使用這種納米片晶體管,每微米溝道寬度的電流可達(dá)到9000微安,大約比目前的最佳平面銦鎵砷MOSFET高3倍以上。如果進(jìn)一步改進(jìn)制造工藝,這種晶體管的性能會(huì)有無限潛力。堆積更多納米片就有可能將性能提高10倍甚至更多。(位于加州馬里布的休斯實(shí)驗(yàn)室的研究人員目前正在研究堆疊數(shù)十片納米片,用以開發(fā)氮化鎵動(dòng)力器件。)我們相信這一策略對(duì)未來的高速節(jié)能集成電路意義非凡。

銦鎵砷并非未來納米片晶體管的唯一選擇。研究人員還在探索其他具有高遷移率電荷載流子的半導(dǎo)體,如鍺、砷化銦和銻化鎵。例如,近期,新加坡國立大學(xué)的研究人員將砷化銦制成的n型晶體管和銻化鎵制成的p型晶體管組合,構(gòu)建出了完整的CMOS集成電路。不過,使用摻雜鍺可能是一個(gè)更簡單的解決方案,因?yàn)殡娮雍屯ㄟ^它的正電荷載流子(空穴)速度都非常快。此外,鍺仍然存在一些制造工藝和可靠性問題。因此,業(yè)內(nèi)首先可能會(huì)采取折中方法,使用硅鍺作為溝道材料。

總而言之,堆疊納米片似乎是制造未來晶體管的最佳方式。芯片制造商對(duì)這項(xiàng)技術(shù)信心十足,有意在不久的將來將其納入發(fā)展路線圖。隨著與高遷移率半導(dǎo)體材料集成,納米片晶體管將會(huì)代領(lǐng)我們進(jìn)入人人都能夠預(yù)見的未來。