從目前看來,多家公司正在采用小芯片模型,作為他們開發(fā)下一代類 3D 芯片設計的一種手段,但這種方法在成為行業(yè)的主流技術(shù)之前,還有很長的路要走。

使用小芯片模型實現(xiàn) 3D 芯片設計需要幾個部分。一些大玩家擁有這些作品,但大多數(shù)都是專有的。其他人則缺少一些關(guān)鍵組件,因此難以開發(fā)這些設計。但是一些實體正在將這些部件推向市場,這可能會在未來的某個時候讓客戶更容易獲得小芯片。

如今,公司、政府機構(gòu)和研發(fā)組織都在大力支持小芯片,小芯片正在成為開發(fā)高級系統(tǒng)級設計的替代方法。使用這種方法,供應商可以在庫中擁有模塊化芯片或小芯片的列表。小芯片可以具有不同的功能和工藝節(jié)點。客戶可以混合搭配小芯片,然后將它們組裝在現(xiàn)有的高級封裝或新架構(gòu)中。這樣做的目標是能加快上市時間并降低成本。

這個概念并不新鮮。多年來,AMD、DARPA、英特爾、Marvell 和其他公司都開發(fā)了支持小芯片的設計。如今,英特爾、AMD 和其他公司正在開發(fā)下一波基于小芯片的產(chǎn)品。“明年你會看到越來越多的小芯片設計,”TechSearch International 總裁 Jan Vardaman 說。

在推進復雜芯片設計方面,小芯片可能比傳統(tǒng)方法具有一些優(yōu)勢。傳統(tǒng)上,為了推進設計,供應商會在片上系統(tǒng)(SoC)上集成多個功能。然后,在每一代,他們都會在 SoC 上塞進更多的功能。但這種方法在每一代都變得越來越困難和昂貴。

雖然有些人會繼續(xù)走這條路,但其他人正在尋找先進封裝等替代品。推進芯片設計的另一種方法是在封裝中組裝復雜的芯片。先進封裝有多種形式,小芯片是眾多方法之一。但是小芯片有望以更低的成本實現(xiàn)模仿當今 SoC 的新架構(gòu)。

盡管如此,這種方法還處于起步階段,在成為廣泛客戶使用的主流產(chǎn)品之前,該技術(shù)還有很長的路要走。今天,只有少數(shù)公司擁有開發(fā)這些產(chǎn)品的能力。大多數(shù)企業(yè)都沒有到位的專業(yè)知識。這使得開發(fā)類似小芯片的設計變得困難。

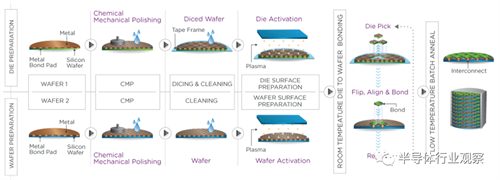

基本上,設計基于小芯片的產(chǎn)品需要幾個方面的能力,包括設計能力、die、die到die互連和制造策略。這些部分中有許多是在公開市場上出現(xiàn)的,但它們是分散的。其他部分正在研發(fā)中。

但是小芯片方法有一些新的發(fā)展:

臺積電正在為代工客戶提供類似小芯片的設計。

其他代工廠以及 OSAT 正在開發(fā)小芯片策略。

開放域特定架構(gòu) (Open Domain Specific Architecture :ODSA) 子項目是一個行業(yè)組織,正在這里開發(fā)幾個關(guān)鍵部分。ODSA 還在為所有開發(fā)人員開發(fā)小芯片設計和建模指南。

它希望有一天你可以在公開市場上買賣小芯片。

還有其他一些努力。即便如此,供應商仍面臨著小芯片的各種設計、集成、制造和供應鏈挑戰(zhàn)。

為什么是小芯片?

多年來,IC 供應商一直依靠縮放來推進芯片設計,在每個新節(jié)點的 SoC 上封裝更多晶體管。當今最先進的芯片擁有數(shù)十億個晶體管。但是芯片縮放變得越來越困難,并且縮放的價格、性能和功耗優(yōu)勢比晶體管縮小得更快。

到了 3nm以后,finFET將失去動力。從 2022 年的 3nm 節(jié)點開始,該行業(yè)正在轉(zhuǎn)向一種稱為全環(huán)柵的新型晶體管。

“Gate-all-around 或 GAA 晶體管是一種改進的晶體管結(jié)構(gòu),其中柵極從四面八方接觸溝道并實現(xiàn)持續(xù)縮放,” Lam Research大學項目主管 Nerissa Draeger 說。“納米片在概念上可能很簡單,但它們給制造帶來了新的挑戰(zhàn)。”

設計成本是另一個問題。IBS 首席執(zhí)行官Handel Jones表示,設計 28 納米芯片的平均成本為 4000 萬美元。相比之下,設計 7 納米芯片的成本為 2.17 億美元,設計 5 納米芯片的成本為 4.16 億美元,3nm 設計更將耗資 5.9 億美元。

多年來,該行業(yè)已經(jīng)認識到這些有問題的趨勢。基于異構(gòu)集成的先進封裝是實現(xiàn)以前只能通過擴展 SoC 才能獲得的優(yōu)勢的另一種方式。業(yè)界已經(jīng)為多種應用開發(fā)了各種先進的封裝類型,但由于成本原因,這種方法通常僅限于高端應用。

不過,這種情況正在開始改變。“業(yè)界對先進封裝的投資越來越多,并一直致力于通過擴展封裝級間距和將更多功能集成到一個新的封裝中,來提高系統(tǒng)級互連密度、降低功耗、實現(xiàn)更小的外形尺寸和更低的成本。單一包裝,” Brewer Science 的高級項目經(jīng)理Xiao Liu說。

先進封裝解決了當今系統(tǒng)中的若干挑戰(zhàn)。例如,在系統(tǒng)中,數(shù)據(jù)在單獨的處理器和存儲設備之間來回移動。但有時這種交換會增加延遲并增加能耗。解決問題的一種方法是將內(nèi)存和處理器更緊密地結(jié)合在一起,并將它們集成到一個封裝中。

“需要以更低的功耗獲得更高的內(nèi)存帶寬,” Amkor高級產(chǎn)品開發(fā)高級總監(jiān) Dave Hiner在最近的一次演講中說。“在這里你可以看到內(nèi)存的聯(lián)合封裝,無論是在封裝內(nèi)還是在芯片上。”

在另一個例子中,供應商傾向于在單個芯片上集成所有功能。但這種方法都變得越來越困難和昂貴。

“有一個解決方案,就是將該 SoC 分解為其功能塊,然后將它們重新封裝或?qū)⑦@些功能塊重新構(gòu)成小芯片。這些小芯片本質(zhì)上是彼此相鄰放置在一個封裝中,” Hiner 說。

“小芯片方法很有吸引力。我們看到的趨勢是,越來越多的客戶希望找到一種將不同部分集成在一起的方法。他們希望將不同功能的芯片混合搭配在一起,”臺積電高級副總裁 Kevin Zhang 說。

小芯片與其說是一種封裝,不如說是一種方法論。客戶可以利用小芯片模型并將芯片集成到現(xiàn)有的高級封裝類型中,例如扇出和2.5D。在3D-IC 中,還可以選擇在邏輯上堆疊邏輯或在存儲器上堆疊邏輯。

那么最好的解決方案是什么?“問題是我們的目標是什么,” ASE研發(fā)副總裁 CP Hung在最近的 IEEE 電子元件和技術(shù)會議 (ECTC) 的一個小組中說。“對于多個芯片,您必須考慮 I/O 密度。我們可以在倒裝芯片中處理。如果這還不夠,我們可以考慮扇出。如果我們有多個內(nèi)存需要集成,我們可能需要使用 2.5D。”

圖 1:高性能計算封裝的不同選項、基于中介層的 2.5D 與扇出基板上芯片 (FOCoS)。資料來源:日月光

Chiplet 的應用和挑戰(zhàn)

并非所有產(chǎn)品都需要基于 Chiplet 的設計。事實上,對于許多應用來說,這有點過了。但是對于特定的應用程序,小芯片方法提供了靈活性,支持各種設計。在一個例子中,英特爾正在開發(fā) Ponte Vecchio,這是一種包含 47 個tiles或小芯片的 GPU。其中兩個基于 10nm finFET。該設計總共擁有 1000 億個晶體管。

在另一個例子中,AMD 正在開發(fā) 3D V-Cache,這是一種堆疊在處理器上的緩存小芯片。這兩款設備均基于臺積電的 7nm 工藝。

圖 2:AMD 的 3D V-Cache 將緩存堆疊在處理器上。資料來源:AMD

我們甚至可以使用成熟節(jié)點的設備來實現(xiàn)小芯片設計。

“你可以擁有射頻毫米波和光互連等技術(shù)。他們將使用不同于 FPGA 或 CPU 的技術(shù)。你還可以擁有其他技術(shù),包括GaN,”英特爾研究科學家 David Kehlet 說。

開發(fā)基于小芯片的設計并不簡單。根據(jù)思科的說法,以下是主要挑戰(zhàn):

設計和集成

生態(tài)系統(tǒng)復雜性

制造、測試和產(chǎn)量

資質(zhì)和可靠性

標準

“一般來說,要使任何技術(shù)變得更加主流或成熟,您都需要一個重要的驅(qū)動力,”思科技術(shù)和質(zhì)量副總裁 Jie Xue 在 ECTC 說。“驅(qū)動力來自擁有大批量需求的客戶,所以他們推動了投資,推動了開發(fā),并推動了成本。”

一開始,設計師需要考慮很多問題。在 ECTC 上,AMD 的高級研究員 Bryan Black 概述了小芯片的設計注意事項和挑戰(zhàn):

如何劃分系統(tǒng)中的芯片

設計重用

管理參數(shù)變化

電力輸送

互連速度

分區(qū)開銷

全局時鐘

Die安全

熱管理

設計人員還應該預先考慮與制造過程有關(guān)的其他問題。QP Technologies銷售和營銷副總裁 Rosie Medina 表示:“例如,為基于小芯片的設計提供合適的基板和/或中介層至關(guān)重要。”此外,客戶需要考慮設計和制造基板和/或中介層的時間和成本。“

換句話說,除了設計考慮之外,提前制定制造策略也很有意義。理想情況下,獨立的設計和制造團隊應該攜手合作。設計不僅應該在現(xiàn)場工作,而且必須具有生產(chǎn)價值。

選擇制造合作伙伴至關(guān)重要,這里有幾種選擇:1) 在內(nèi)部制造封裝;2) 與代工廠合作;3) 參加 OSAT;4) 與多個供應商合作。

每個選項都是可行的。供應商選擇取決于能力、制造規(guī)模和成本。客戶傾向于與他們信任的供應商合作。

尋找die,互連

圍繞小芯片開發(fā)設計只是成功的一半。要將基于小芯片的設計投入生產(chǎn),供應商需要多個部件,例如知識產(chǎn)權(quán) (IP) 內(nèi)核、已知良好芯片 (known-good die

:KGD) 和芯片到芯片互連。

KGD 是裸片。在小芯片中,目標是在封裝中組裝好的芯片。IP 核涉及開發(fā)芯片的構(gòu)建塊,例如 I/O、處理器核和庫。

您在哪里可以找到小芯片的 IP 核和芯片?有多種選擇,包括開發(fā)自己的技術(shù)、前往代工廠和/或OSAT以及聯(lián)系無晶圓廠 ASIC 設計公司。

AMD、英特爾和其他一些公司擁有開發(fā)自己的小芯片和 IP 的資源。開發(fā)內(nèi)部die/IP 需要時間和金錢,但有一些優(yōu)勢。IC 供應商擁有有關(guān)內(nèi)部芯片以及它們?nèi)绾闻c他人交互的關(guān)鍵數(shù)據(jù)。

”如果封裝中的每個芯片都是為特定產(chǎn)品定制設計的,就像我們在 AMD 所做的那樣,那么某些事情,例如供電、互連、時鐘、緩存層次結(jié)構(gòu),以及其他所有事情都由一個設計團隊同時處理,這使得開發(fā)變得更加容易,“AMD 的 Black 說。

但即使是較大的公司也負擔不起內(nèi)部開發(fā)所有 IP 的費用。他們可能希望采購第三方 IP 以節(jié)省時間和金錢。

這可能是一個重大挑戰(zhàn)。例如,供應商可能想要使用另一家公司的die。但該公司可能不想分享芯片的內(nèi)部工作原理,這對于充分表征它至關(guān)重要。即使他們愿意共享數(shù)據(jù),芯片仍需要經(jīng)過驗證和測試過程。

”問題是,我們是在內(nèi)部開發(fā)die還是在外部找到它們?這將決定芯片如何與架構(gòu)交互,以及我們?nèi)绾螌⑺鼈兘M合在一起。這將影響他們在物理層面上的互動方式,“Black說。”在五年時間框架內(nèi),我們將面臨挑戰(zhàn)的是不同組織的異質(zhì)部分。我們?nèi)绾螌⒁患夜镜男酒蚕斫o另一家公司以制造更復雜的設備?如果die來自多個不同的來源,那么我們最終會面臨各種挑戰(zhàn)的無盡配置。“

大多數(shù)公司內(nèi)部沒有這些部件。挑戰(zhàn)在于找到必要的部分,這需要時間和資源。所以也許與代工廠和/或 OSAT 合作更有意義。

一些代工廠和 OSAT 正在實施他們的小芯片戰(zhàn)略,但并非所有供應商都一樣。一方面,臺積電提供了一種交鑰匙方法。這家代工廠巨頭擁有大量經(jīng)過認證的內(nèi)部和第三方 IP 核目錄。客戶可以選擇使用這些 IP 模塊中的任何一個來開發(fā)傳統(tǒng)芯片。

臺積電表示,許多用于傳統(tǒng)芯片的相同 IP 核和裸片可用于開發(fā)基于小芯片的設計。它還具有制造能力。

”商業(yè)模式與我們的晶圓業(yè)務沒有什么不同,“臺積電的Kevin說。”我們與客戶合作確定正確的小芯片和集成方案。當我們將不同的芯片堆疊在一起時,每個芯片都來自我們的客戶。它們都是客戶特定設計的 IP。他們選擇想要整合的tile。我們提供的解決方案可幫助客戶將不同的小芯片與不同的高級集成技術(shù)集成在一起。“

其他代工廠可能有類似或不同的策略。OSAT 也在研究他們的小芯片策略。不過,就目前而言,大多數(shù)供應商的策略類似于當前的封裝流程。和以前一樣,代工廠為客戶制造芯片。從那里,他們將完成的芯片發(fā)送到 OSAT,后者負責處理封裝組裝要求。

一些代工廠提供各種封裝組件,例如中介層。他們甚至會為客戶提供TSV制造工藝。但是大部分打包工作是由 OSAT 處理的。

最終,OSAT、代工廠和其他公司希望將小芯片提升到一個新的水平。許多人正在與 ODSA 合作,這是一個尋求將小芯片帶給大眾的行業(yè)組織。ODSA 正在研究多種技術(shù),包括標準芯片到芯片接口、參考設計和工作流程。所有這一切都導致小芯片設計交換 (Chiplet Design Exchange:

CDX) 的出現(xiàn),這是一個開放的市場,可以買賣來自不同供應商的認證小芯片。

ODSA 的 Jawad Nasrullah 表示:”我們正在編寫一份 CDX 白皮書,該白皮書將為業(yè)界提供有關(guān)構(gòu)建小芯片模型的指南。“ ”建模的一致性是開發(fā)組件交易市場的關(guān)鍵。“

但是至少在兩三年內(nèi)不會出現(xiàn)小芯片的公開交換。實現(xiàn)這一目標需要時間和資源。

同時,對于小芯片,供應商需要一種芯片到芯片互連/接口技術(shù),該技術(shù)將一個芯片連接到另一個芯片封裝中。為了實現(xiàn)管芯到管芯互連,供應商在每個die上設計了一個微小的 IP 塊。該塊由帶有電路的公共物理接口組成。這樣,可以連接具有通用接口的芯片,使它們能夠相互通信。

第一波基于小芯片的設計將芯片到芯片互連與公司自有設備的專有接口相結(jié)合。但是為了擴大小芯片的采用,該行業(yè)需要具有開放接口的互連,使不同的芯片能夠相互通信。

這是小芯片的主要絆腳石。

到目前為止,英特爾開發(fā)了市場上為數(shù)不多的開放接口之一。該技術(shù)稱為高級接口總線 (AIB),是一種在小芯片之間傳輸數(shù)據(jù)的接口方案。

供應商需要不止一種芯片到芯片互連方案。其他技術(shù)正在研發(fā)中,但尚不清楚何時準備就緒。這些包括:

ODSA 正在定義一個名為 Bunch of Wires (BoW) 的芯片到芯片接口。

光互連論壇正在開發(fā)一種稱為 CEI-112G-XSR 的技術(shù)。XSR 為小芯片實現(xiàn)每通道 112Gbps 的芯片到芯片連接。

Xilinx 正在開發(fā) OpenHBI,這是一種源自高帶寬存儲器 (HBM) 標準的芯片到芯片互連/接口技術(shù)。

設計和制造問題

最終,客戶希望設計和制造產(chǎn)品。為此,供應商必須為給定的設計選擇封裝類型或架構(gòu),以及適當?shù)男⌒酒托酒叫酒ミB。這不是一項簡單的任務。這里有許多不同且令人困惑的選項。

一旦做出這些決定,就該進入設計階段了。使用 EDA 工具,供應商通常遵循傳統(tǒng)的設計步驟,例如設計輸入、基板/中介層布線和布局以及驗證。

有些內(nèi)部擁有 EDA 設計工具和專業(yè)知識。其他人可能擁有這些工具,但缺乏設計專業(yè)知識。

作為回應,ODSA 正在制定一套用于開發(fā)基于小芯片的產(chǎn)品的設計指南。該文檔稱為”CDX 工作流程白皮書和設計指南“,描述了小芯片所需的各種建模技術(shù)以及如何實現(xiàn)它們。

在設計階段,供應商必須對所需小芯片的行為屬性進行建模。對機械、功耗和熱特性進行建模也很重要。在投入生產(chǎn)之前,必須了解設計的屬性。否則,問題可能會浮出水面。

以芯片到芯片互連為例。”在die或小芯片之間的高速,低延遲的互連的情況下,有多重挑戰(zhàn),“長電技術(shù)市場總監(jiān)Michael Liu說。”這包括但不限于實現(xiàn)超高帶寬時的低功耗。“

還有其他設計問題。而且,當然,設計必須具有生產(chǎn)價值。每種封裝類型,例如 2.5D/3D、扇出等,都有自己的制造流程。

Momentum 正在推動銅混合鍵合,這是一種支持下一代 2.5D 封裝、3D DRAM 和 3D-IC 的制造工藝。它也是小芯片的理想選擇。針對 10μm 及以下的間距,混合鍵合使用微小的銅對銅連接來連接封裝中的芯片。仍處于封裝研發(fā)階段,混合鍵合提供了比現(xiàn)有方法更高的互連密度。

這不是一個簡單的過程。混合鍵合在過程中幾乎需要零缺陷。產(chǎn)品可靠性仍然是一個問題。

在 ECTC 上,Xperi 展示了具有 35μm 間距的 5 芯片堆疊模塊測試車輛的可靠性和熱性能的第一個結(jié)果。”混合粘合部件增強的可靠性性能與現(xiàn)有技術(shù)相比具有顯著優(yōu)勢,“Xperi 產(chǎn)品營銷副總裁 Abul Nuruzzaman 說,Xperi 是一家為客戶提供混合粘合的 IP 供應商。”混合粘合部件非常適合高溫和/或腐蝕性環(huán)境,例如汽車。“

圖 3:Xperi 的芯片到晶圓混合鍵合流程。資料來源:Xperi

結(jié)論

顯然,小芯片是復雜的,具有不同的部分。將它們放在一起是困難的部分。

在某些時候,解決方案可能會匯集在一起。因為有許多應用可以使用小芯片。